摘要:介紹了SMSC公司生產的嵌入式以太網控制器LAN91C111的主要特點及工作原理,并從系統方案、硬件設計、軟件設計等方面,詳細介紹了基于ALTERA公司的NIOS II軟核處理器芯片LAN91C111芯片來實現以太網互聯通信的原理和方法。

關鍵詞:以太網;互聯網通信;LAN91C111;NIOS

0 引言

隨著CPU性能的大幅度提升,嵌入式系統的設計已經進入了更廣泛的領域。隨著FPGA的不斷發展和規模的進一步強大,SOPC的應用也越來越廣泛。由于SOPC的可編程特性很受嵌入式系統開發人員的青睞,因此,隨著信息產業和微電子技術的發展,可編程嵌入式系統設計已經成為信息產業最熱門的技術之一,FPGA正以各種電子產品的形式進入人們日常生活的各個角落。

以太網以其良好的通用性和帶寬性能成為新一代工業控制網絡的焦點,目前,關于嵌入式以太網的設計方案大部分是基于單片機的。由于單片機的速度慢,而FPCA作為一種特殊的嵌入式微處理器系統,則具有快速處理數據的能力。因此,在嵌入式網絡設備中引入FPGA技術,可以使嵌入式以太網的速度更快。為此,本文介紹基于FPGA的嵌入式系統與LAN91C111型自適應10Mb/100Mb嵌入式以太網的接口電路與實現方法。

1 硬件設計

1.1 FPGA的特點

本系統的主控芯片采用ALTERA公司CycloneII系列的EP2C35F484。FPGA內部集成有鎖相環,可以把外部時鐘倍頻,其核心頻率可以到幾百兆,同時具有豐富的IO資源,可以方便連接外設。FPGA的并行執行程序方式具有處理更復雜功能的能力,而且內部嵌有SOPC和DSP。可編程SOPC是一種特殊的嵌入式系統,具有靈活的設計方式,而且可裁剪、可擴充,同時軟硬件在系統可編程功能。

1.2 嵌入式以太網控制器LAN91C111

以太網控制芯片所選用的SMSC公司LAN91C111芯片是專門用于嵌入式產品的10M/100M第三代快速以太網控制器。該器件具有可編程、CRC校驗、同步或異步工作方式,且具有低功耗CMOS設計和小尺寸等特點,是設計嵌入式以太網網絡接口的良好選擇。LAN91C111的原理框圖如圖1所示。

LAN91C111集成了CSMA/CD(帶碰撞的載波偵聽多路接入)協議的MAC(媒體層)和PHY(物理層)。其主要特點是支持IEEE802.3/802 U以太網標準、自適應10M/100M,全雙工/半雙工收發方式、有8KB的片上FIFO存儲器、支持8位或16位或32位總線方式、支持先進的傳輸隊列管理、有串行EEPROM選擇性配置口、并支持突發數據傳輸、支持全雙工交換式以太網、增強式能量管理功能和低功耗的CMOS設計。

總線接口模塊是由數據總線、地址總線、控制總線以8位、16位、或32位形式與外部數據進行交互。LAN91C111以太網控制器遵循IEEE頒布的802.3以太網傳輸協議,內部集成有8KB的RAM,可通過內部的內存管理模塊、仲裁模塊和DMA共同管理數據包的發送與接收。其仲裁器監視以太網總線的數據交流,一旦發生阻塞。仲裁器一方面通過總線接口單元與外部CPU聯系;一方面控制內存控制單元,實現總線的數據協調。LAN91C111內部的RAM可以緩存數據,在全雙工工作模式下,數據傳輸速率可達到10M/100Mbps。所有內部寄存器的初始值均放在EEPROM中,自舉時可完成自動初始化。在數據傳輸過程中,若以10Mbps速率傳輸,則可采用Manchester編碼,并以兩層曼徹斯特代替三電平,且沒有擾頻器和解擾頻器;若以100Mbps速率傳輸,則先將發送到RAM中的數據包以包號的形式存放在FIFO的發送隊列中,然后按照規則逐個將數據包發送到PHY模塊進行4B-5B編碼,發送數據端可將通過擾頻器整理后的4B-5B數據包變換成MLT-3后輸出。而在接收時,則將數據包復制并發送到解擾頻器進行整理,然后再發送到4B-5B解碼器進行解碼。

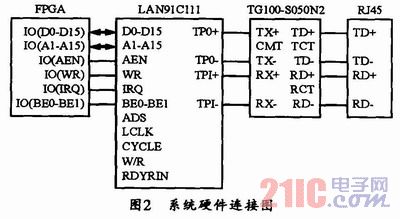

1.3 硬件連接

本設計在FPGA芯片EP2C35中嵌入了32位的NIOS II處理器。由于LAN91C111是專為嵌入式系統設計的,因而其外圍電路相對比較簡單。圖2所示是其硬件連接圖,圖中的地址線、數據線、控制線分別與FPGA相連。由于采用的是16位數據傳輸方式,因此只用到數據總線的低16位。控制線中的AEN為片選信號,INTR0為外部中斷信號,WR為讀寫信號,BE0-BE1為字節選擇端。LAN91C111中的ADS、LCLK、CYCLE、W/R、RDYR-TN信號應均加一個1kΩ的上拉電阻。TG10o-S050N2是以太網的變壓濾波器。TX+、TX-、RX+、RX-分別與LAN91C111的TPO+、TPO-、TPI+、YPI-相連。TG100-S050N2的CMT端也應接一個1kΩ的上拉電阻。RJ45的TD+、TD-、RD+、RD-分別與TG100-S050N2的TD4+、TD-、RD+、RD-相連。在TG100-S050N2的TCT和RCT亦應分別接一個75Ω的電阻和1nF的濾波電容。這樣即可在控制線的作用下完成FPGA與LAN91C111之間的數據通信。

2 軟件設計

ALTERA公司提供的硬件抽象層(HAL)中封裝了系統中硬件的相關細節和驅動程序,用戶可在HAL的基礎上方便地開發存儲等應用程序。

NIOSⅡIDE環境中集成有μCOS II和LWIP,其中LWIP必須在μCOS的支持下使用。μC/OSⅡ是一種免費公開源代碼,結構小巧,而且具有可剝奪

實時內核的操作系統,它可移植、可裁剪,最多可管理64個任務,其每個任務都擁有自己獨立的堆棧,大部分源碼可使用ANSI C語言編寫,整個軟件部分可在NIOS II IDE開發環境下完成。由于程序的內容較多,本文著重介紹LAN91C111的初始化、發送數據、接收數據三個部分的軟件設計方法。

2.1 初始化

ALTERA提供有LWIP的NIOS II端口,其源代碼包含在NIOS II開發工具包中。LWIP可為NIOS II處理器提供對以太網連接棧的快速、開源

地訪問。ALTERA的LWIP端口包括套接字API封裝,提供有標準的、文檔說明齊全的套接字API。LWIP協議棧的主要接口是標準的套接字接口。

除了套接字接口以外,還可調用lwip_stack_init()函數和lwip_devices_init()函數來對堆棧和驅動程序初始化。通過HAL系統代碼可調用

init_done_func()、get_mac_addr()和get_ip_addr()函數來設置MAC地址和IP地址。為了初始化堆棧,在調用OSStart啟動μC/OS II調度程序之前應調用函數lwip_stack_init(),其原型為voidlwip_stack_init( int thread_prio, void(*init_done_func)(void*),void*arg)。堆棧初始化后,還必須調用函數init_done_func(),而該函數必須調用函數lwip_devices_init()。利用函數lwip_devices_init()可以對在system.h中定義的所有已安裝的以太網設備驅動程序進行注冊,若返回一個非0值則表示注冊成功。注冊成功后,TCP/IP棧即可使用,之后便可在程序中創建任務。該函數的參數是接收線程的優先級。LWIP系統碼在設備初始化過程中,可通過lwip_devices_init()函數調用函數get_mac_addr()和get_ip_addr()。用戶通過編寫這些函數,可在系統中將MAC和IP地址存放在任意位置,從而代替在設備驅動程序中固定位置的硬編碼,并增加系統的靈活性。設計時,可以將MAC地址存放在Flash存儲器中,也可以將MAC地址存放在片上內嵌的存儲器中。當所有的初始化都準備好后即可調用OSStart()以啟動RTOS進行任務調度。這個過程需要設置以太網目的地址、以太網源地址、協議類型,然后再按照所設置的協議類型來設置數據包。

2.2 數據的發送和接收

數據的接收和發送可采用中斷方式。中斷服務程序通過檢查LAN91C111的中斷狀態寄存器來判斷是發送中斷請求還是接收中斷請求。初始化完成后,即可創建任務,建立套接字,綁定端口,綁定完之后,再監聽端口。當LAN91C111接收到數據包時,可由EPH模塊察看此數據包的目的地址,若為本網卡的MAC地址或廣播地址或多播地址,則把此數據包傳送到LAN91C111的RAM中,并向處理器發送中斷,由處理器進行數據處理。由于采用的是TCP/IP協議,接收數據應調用read()函數來接收建立連接的套接字中的數據,并將其放入緩沖區。發送過程則是由FPGA將數據傳送到LAN91C111,再由LAN91C111將接收到的數據封裝成數據包,并檢測網絡,當沒有數據傳輸時,再將數據包傳輸到網絡中,并向處理器發送中斷信號,以表示數據傳送完畢。發送數據時通過調用write()函數可將要發送的數據發送到指定連接的目的地址。

3 結束語

本文的整個設計使用了邏輯單元(LE)5314個,占用EP2C35F484芯片內部資源的16%,這充分體現了FPGA資源的豐富性。在傳統設計中,通常選用單片機和低速網卡的設計方案,這在實際應用中,網絡速度相對較慢,而本設計中選用高速的以太網控制芯片LAN91C111和高速的FPGA,極大地提高了系統的網絡數據處理能力,并可滿足網絡數據采集的需求。另外,基于FPGA的NIOSⅡ方案,還可根據實際需要添加不同IP,這也體現了SOPC的靈活性與可裁減性。