1 系統總體設計讀寫

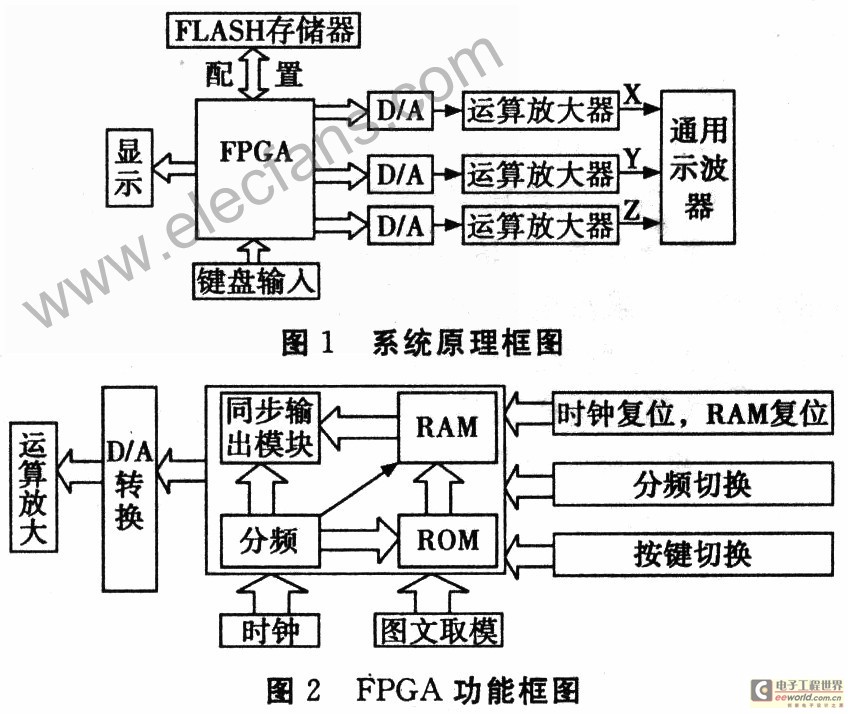

根據設計要求:在示波器上顯示2個以上字符或圖案,如顯示0-9十個數字及英文字符、圖象等,結合示波器顯示原理,設計電路如圖1所示。將要顯示的數字或符號進行取模,得到其二進制形式表示。將轉換好的數據送入FPGA內部RAM存儲。

在設計上我們使用了XILINX的SPARTAN-3芯片,作為控制器,完成總的數控部分、鍵盤和和顯示接口部分的控制。采用八位(或者更高位)D/A轉換,對FPGA芯片輸出二進制數字量進行數一模轉換,在經過高速運算放大器后得到其電壓量。分X,Y兩路輸出給示波器,根據示波器原理,在屏幕上打點顯示數字(或者圖形)。而Z通道作為另一路獨立通道,對顯示的數字亮度進行可控顯示。

2 系統硬件設計

2.1 總體控制模塊

基于本設計,系統控制模塊的部分是具有掩膜可編程門陣列的邏輯器件——FPGA。

Spartan系列FPGA是Xilinx公司可編程邏輯產品中的高性價比產品的代表,而Spartan-Ⅲ系列FPGA是為那些需要大容量、低價格電子應用的用戶而設計的。本系統使用的是XILINX公司的XC3S200型號芯片,其技術參數如下:

●4 320個邏輯單元;

●系統門密度200 k個;

●CLB陣列24*20,共480個;

●最大用戶I/O173,最大差分I/O76;

●分布式RAM容量30 Kbit,Block RAM容量216Kbit;

●嵌入式18x18乘法器支持高性能DSP應用;

●PCI和帶有LVDS的高速差分信號。

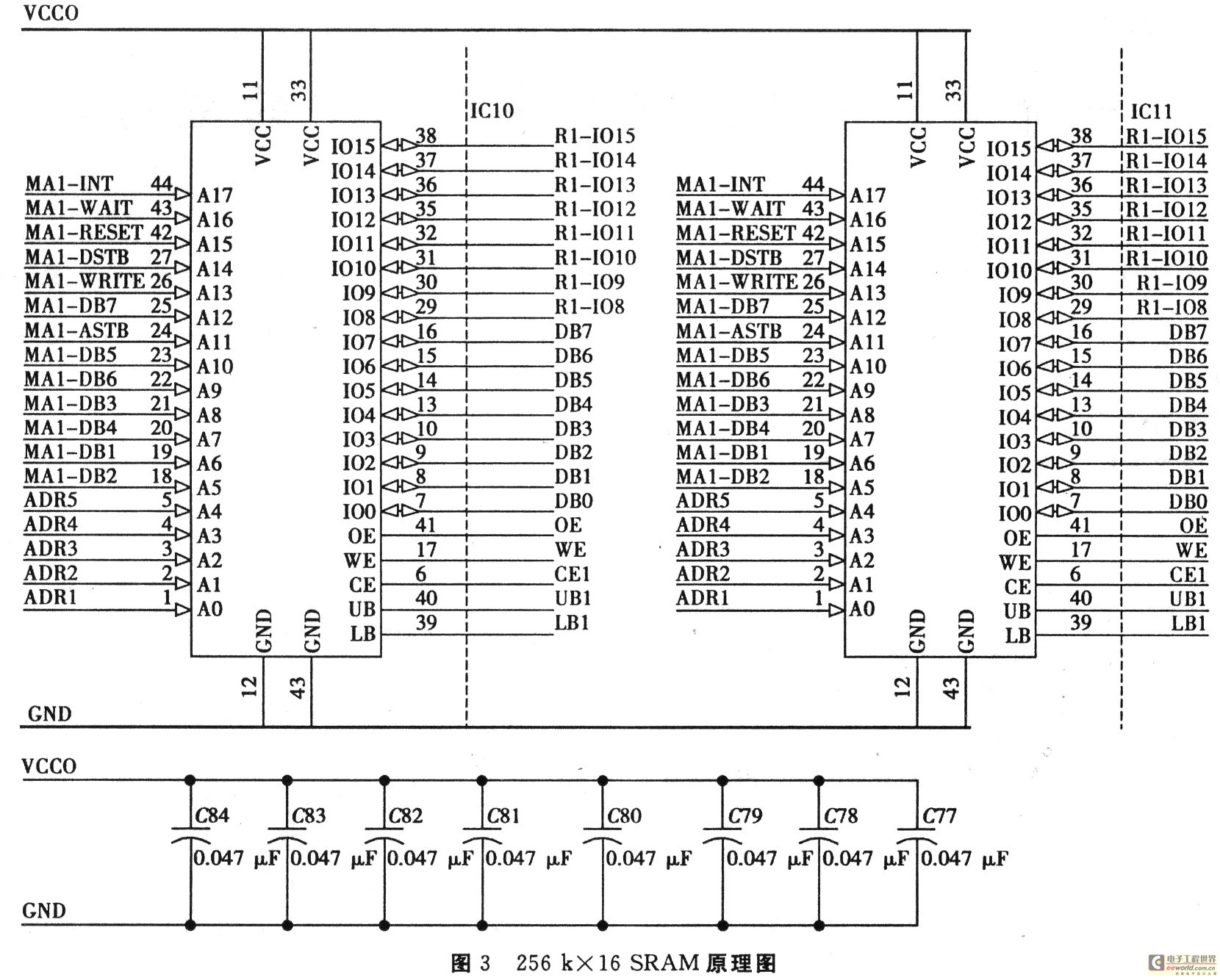

2.2 存儲單元模塊

由于FPGA基于CMOS SRAM工藝,不具備掉電保護功能,當無電源供電時,配置的數據丟失,芯片的功能也隨之丟失。因此,本設計采用FLASH存儲器在線重配置的方法。

2.3 外圍電路模塊

2.3.1 D/A轉換

在D/A選擇上,我們用的是美國半導體公司的 DAC0832,它具有8位并行、中速(建立時間1 us)、電流型、價格低廉等特點。它有單緩沖工作方式、雙緩沖工作方式兩種工作方式。單緩沖工作方式時,一個寄存器工作于直通狀態,一個工作于受控鎖存器狀態。在不要求多相D/A同時輸出時,可以采用單緩沖方式,此時只需一次寫操作,就開始轉換,可以提高D/A的數據吞吐量。雙緩沖工作方式時,兩個寄存器均工作于受控鎖存器狀態。當要求多個模擬量同時輸出時,可采用雙重緩沖方式。

它的技術參數為:建立時間1 us;8位并行;低功率損耗20 mW;支持電壓:5 V~15 V。

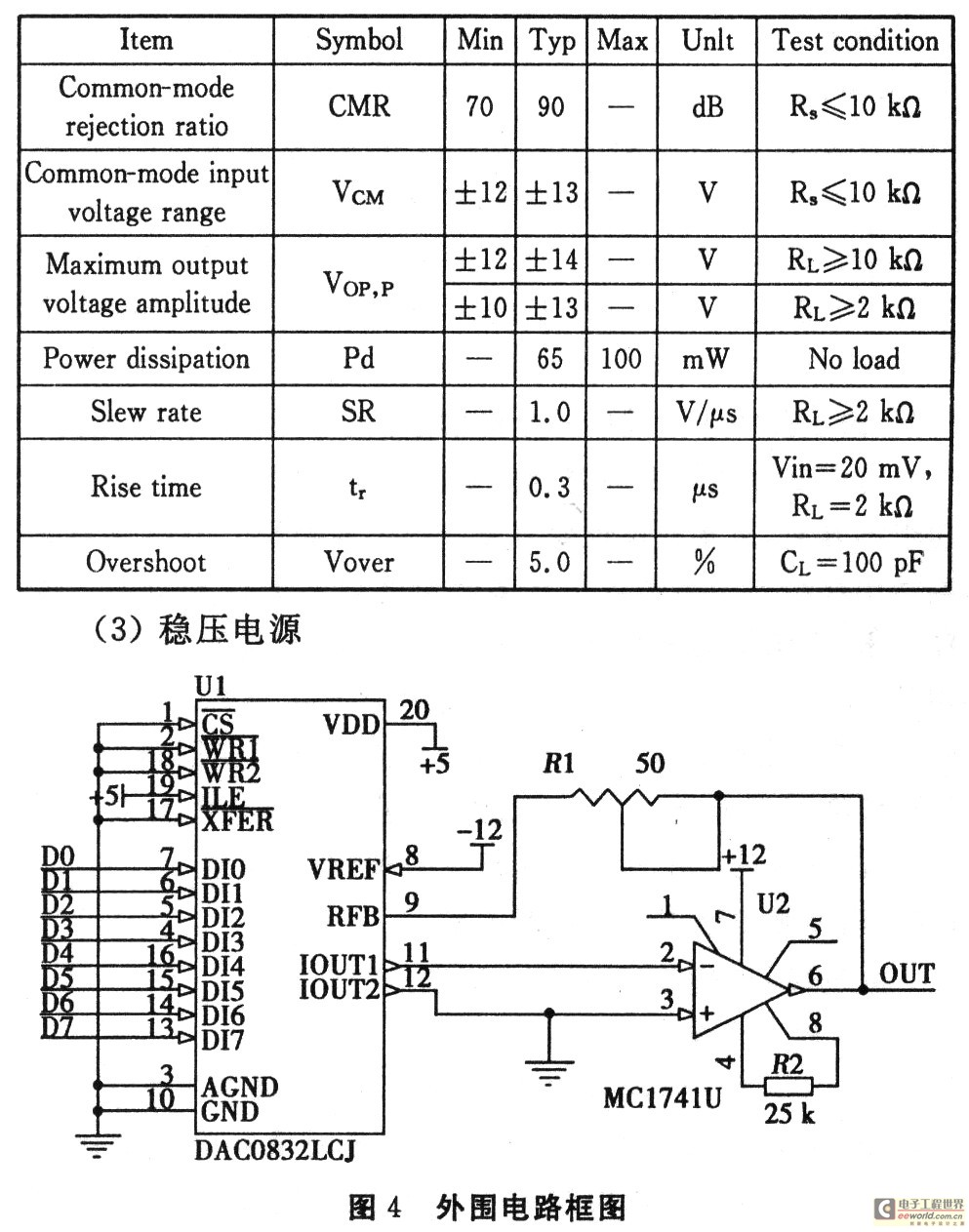

2.3.2 運算放大

在D/A轉換之后,我們得到的是電流信號,而需要輸入示波器的為電壓信號,因此運用運算放大器來進行轉換,同時將運放設計為可調形式,通過調節它便可以調節輸出電壓的大小,達到控制顯示幅值的目的。本設計采用LM741系列運放,其技術指標加下:

3 系統軟件設計

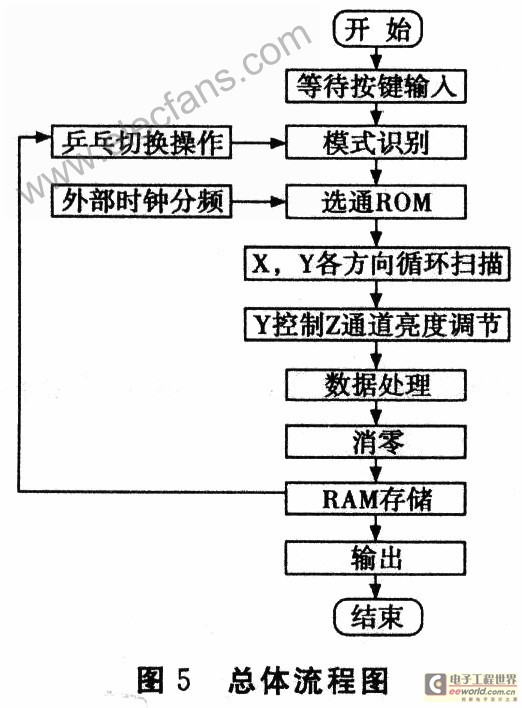

基于VHDL語言的功能與靈活性,非依賴性和可移植性種種優勢,本設計在FPGA編程上采用了VHDL語言實現。總體設計思路:采用50 MHz外部時鐘控制對FPGA內部進行分頻控制,在分頻模塊的作用下得到設計所需要的時鐘信號。通過按鍵選通在ROM內部選擇要顯示的模塊部分,進行X、 Y方向掃描,得到初步的數據,同時外加Z方向掃描來控制所顯圖形的亮度。通過將所有的“1”存儲在一個ROM中作為緩存,達到消除零點的目的。將ROM中的數據轉移到RAM中,通過乒乓交換操作來進行模式轉換,最后通過外圍電路輸入示波器,實現顯示。總體流程圖:

4 結語

本文是基于FPGA的數字示波器圖文顯示系統的硬件/軟件的設計思路和設計方案。此系統設計完成后,測試表明系統可以將相應的圖形文字顯示出來,顯示的圖形和文字與預期的基本一致。該設計滿足了系統的需要,更重要的是具有很強的靈活性和可控性,同時使顯示更加高速度快捷,具有非常廣闊的應用前景。