頻移鍵控(FSK)是用不同頻率的載波來傳送數字信號,并用數字基帶信號控制載波信號的頻率。具有抗噪聲性能好、傳輸距離遠、誤碼率低等優點。在中低速數據傳輸中,特別是在衰落信道中傳輸數據時,有著廣泛的應用。傳統上以硬件實現載波的方法都是采用直接頻率合成器(DDS)實現。但是DDS傳統的實現方式是基于查找表思想,即通過查找預先存儲的正余弦表來產生需要的正余弦值。當頻率、精度要求越高,需要存儲的值也就越多,考慮FPGA的RAM資源有限,傳統的DDS實現方式就有了應用瓶頸。因此導致開發成本過高,甚至無法實現,不適合現代通信系統的發展。

本文提出了應用CORDIC(Coordinate Rotation Digital Computer)算法實時計算正弦值的方案,并基于CORDIC算法在FPGA芯片上設計了2FSK調制器。這不僅能夠節省大量的FPGA邏輯資源,而且能很好地兼顧速度、精度、簡單、高效等方面。

1 CORDIC算法原理及結構

1.1 CORDIC算法原理

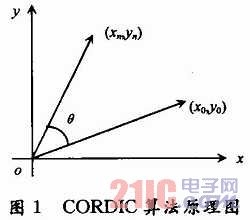

CORDIC算法是由J.Volder于1959年提出的。該算法適用于解決一些三角學的問題,如平面坐標的旋轉和直角坐標到極坐標的轉換等。C-ORDIC算法的基本思想是通過一系列固定的、與運算基數有關的角度的不斷偏擺以逼近所需的旋轉角度。從廣義上講,CORDIC方法就是一種數值計算的逼近方法。該算法實現三角函數的基本原理如圖1所示。

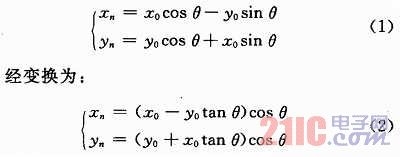

設初始向量(x0,y0)逆時針旋轉角度θ后得到向量(xn,yn),如圖1所示。則:

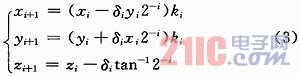

為了避免復雜的乘法運算,用一系列微旋轉來處理,第i次旋轉可表示為:

式中:θi表示第i次旋轉的角度,并且滿足tanθi=2-i;zi表示第i次旋轉后與目標角度的差;δi表示向量的旋轉方向,由zi的符號位來決定,即δi=sign zi。![]()

![]() 為每一級的校正因子,也就是每一級旋轉時向量模長發生的變化,對于字長一定的運算,總的校正因子是一個常數。若總的旋轉次數為n,則總校正因子用k表示為:

為每一級的校正因子,也就是每一級旋轉時向量模長發生的變化,對于字長一定的運算,總的校正因子是一個常數。若總的旋轉次數為n,則總校正因子用k表示為:

由式(7)可知:xn,yn分別為輸入角θ的余弦和正弦值,故基于CORDIC算法可產生正弦載波信號,而且由式(5)可以看出所有運算簡化成加減法和移位操作,因此很容易用硬件實現。

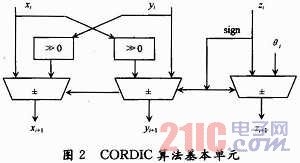

1.2 CORDIC流水線結構

CORDIC算法的實現方式有2種:簡單狀態機法和高速全流水線處理器法。如果計算時間的要求不嚴格,可以采用狀態機結構。這一結構中最復雜的就是兩個桶狀移位器,而桶狀移位器的面積大約和它所包含的傳輸門的數目成正比。盡管可以通過改進CORDIC算法來減小CORDIC處理器的總面積,但桶狀移位器所占的面積并不能減小。另外,這種結構由于只在時間上復用資源,因此,數據吞吐率不高。

由于CORDIC算法的內部數據流規則,決定了在CORDIC處理器解決方案中非常適合采用流水線型微旋轉結構。采用流水線可將一個算術操作分解成一些小規模的加減法和移位操作,并在多個比較高速的時鐘內完成。另一方面,輸出信號的精度只與CORDIC算法的旋轉次數或流水單元數有關,即與級數有關。如需提高精度,只需簡單地增加流水單元即可,其擴展性很好,而且這并不會大量增加FPGA的資源耗費。CORD-IC流水線結構的每一級迭代旋轉的硬件實現基本單元如圖2所示。

2 基于CORDIC算法正弦載波發生器的總體結構

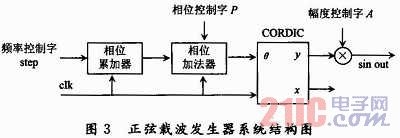

正弦載波發生器系統結構如圖3所示。

在該系統結構圖中,CORDIC計算單元是核心。CORDIC計算單元的輸入由相位加法器提供。相位加法器不間斷地產生角度值,由CORDIC計算單元計算出相應的三角函數值,即可在其輸出端產生連續的數字正弦載波。

通過頻率控制字,改變相位累加器的步長,這樣即可改變正弦載波的頻率。具體的數學推導如下:

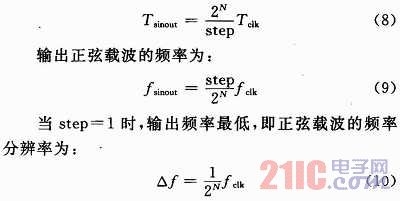

設相位累加器的字長為N,頻率控制字即步長為step,則2N就相當于2π rad,N位中的最低有效位相當于2π/2N rad,即最小的相位增量,step對應的相位為step×(2π/2N)rad,完成一個周期的正弦載波輸出需要2N/step個參考時鐘周期。所以輸出正弦載波的周期為:

可見改變相位累加器的步長step,可以改變正弦載波的頻率;改變相位累加器的字長N,可控制正弦載波的頻率分辨率。在相位累加器后加入相位加法器,通過改變相位控制字P,可以控制輸出信號的相位;通過設置幅度控制字A,可控制最終輸出的正弦載波的幅度大小。因此,通過對相位控制字、頻率控制字或幅度控制字進行多路選擇,可以形成不同進制的調制方式。可以看出,使用該結構可以很容易實現頻率調制、相位調制和幅值調制。

3 2FSK調制器的FPGA設計

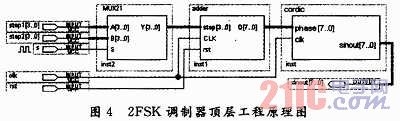

圖4為2FSK調制器頂層工程原理圖。該原理圖主要由三個模塊組成:2選1數據選擇器MUX21、相位累加器adder、正弦載波生成模塊eor-dic。其中,clk為系統時鐘信號,rst為系統清零信號,step1,step2為2個不同的頻率控制字,s為系統頻率控制字選通端。2選1數據選擇器的選通端s受基帶信號控制,當基帶信號為‘0’時,選通控制字step1;當基帶信號為‘1’時,選通控制字step2。通過對step1,step2的選擇,可以實現頻率的切換。

在QuartusⅡ環境中,三個子模塊均用VHDL語言進行設計,系統頂層工程采用原理圖進行設計,對系統頂層工程進行器件選擇、引腳鎖定、編譯、綜合后下載到Cyclone系列EP1C12Q240C8器件中,通過在頻率控制字的引腳選擇不同參數即可在FPGA器件中完成2FSK調制器的設計。

4 系統硬件實時測試

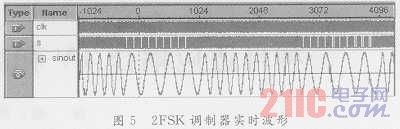

調制器的輸出信號為數字信號,經D/A轉換后可以通過示波器進行測試,也可以直接采用QuartusⅡ軟件中的嵌入式邏輯分析儀Signal-TapⅡ進行測試。

采用SignalTapⅡ進行芯片測試,用戶無需外接專用儀器,就可以對FPGA器件內部所有信號和節點進行捕獲分析,而又不影響原硬件系統的正常工作。經測試得到的實時波形如圖5所示。測試結果表明,基于FPGA和CORDIC算法的2FSK調制器設計方案是正確可行的,且波形流暢,在轉換處能快速進行切換。

5 結語

用FPGA和CORDIC算法實現信號調制,既克服了傳統方法耗費資源、運行速度低等缺點,還具有靜態可重復編程和動態在系統重構的特性,極大地提高了電子系統設計的靈活性和通用性,大大縮短了系統的開發周期。