隨著SoC設計規模的與日俱增,其功能日趨復雜,芯片的驗證階段占據了整個芯片開發的大部分時間。為了縮短驗證時間,在傳統的仿真驗證的基礎上涌現了許多新的驗證手段,如SDV(Software Driven verification)、BFM(Bus Function Model)等,以及基于FPGA的原型驗證技術。

因FPGA工藝及技術的發展,其速度、容量和密度都大大增加,功耗和成本在不斷的降低,使得基于FPGA的原型驗證得到廣泛的應用。基于FPGA的原型驗證可以比軟件仿真速度高出4~6個數量級,而且還可以提高流片成功率,并為軟件開發提供了硬件平臺,加速了軟件的開發速度。

本文主要論述了FPGA基原型驗證的實現方法,并且針對ARM1136為內核的SoC,如何快速而有效地搭建一個原型驗證平臺做了詳細的論述,最后還以UART為例來說明一種簡單、可重用性好、靈活性強的測試程序架構。

1 基于ARM1136的SoC設計

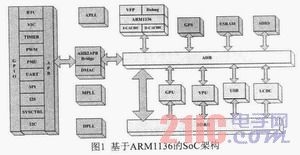

本文驗證的SoC芯片是定位于手持視頻播放設備、衛星導航產品的高性能應用處理器,采用了ARM1136作為內核,ARM11在提供超高性能的同時,還能保證功耗、面積的有效性。

同時在這個架構中還采用了ARM公司的AMBA(Advanced Microcontroller Bus Architecture)總線,它是一組針對基于ARM核的片上系統之間通信而設計的標準協議。在設計中,對于一些處理數據和通訊速度要求較高的設備掛在AHB總線上,而那些對總線性能要求不高的設備掛在APB總線上。

為了能夠提高一些設備間的數據傳輸速度,該設計加入了DMA,其支持存儲器到存儲器、存儲器到外設、外設到存儲的傳輸。

基于ARM11設計的SoC系統構架如圖1所示,這個系統還包括了USB控制器、LCD控制器、圖像處理單元GPU、視頻處理單元VPU、GPS、I2S、通用異步串口UART、同步串口SPI、TIMER、PWM、實時時鐘(RTC)、I2C總線和功耗管理單元(PMU)等。

2 FPGA原型驗證平臺的快速搭建

FPGA的發展為SoC的原型驗證提供了巨大的發揮空間,面對復雜的SoC系統,傳統的一些驗證方法和單一的驗證技術已經不能滿足設計的要求。本文所設計的平臺不僅能加快開發速度,提高流片成功率,而且還具有低錯誤率、快速和簡易的特點,因此特別適合用于RTL代碼更改頻繁的設計中。

2.1 FPGA原型驗證平臺的硬件環境設計

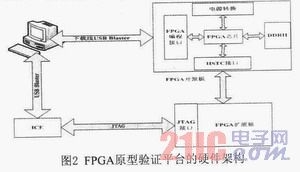

FPGA原型驗證平臺的硬件設計應該考慮FPGA的邏緝資源、應用資源、擴展能力、PCB信號質量、調試難度、組態和成本等方面的因素。本原型系統設計的FPGA開發板采用的是Terasic公司的DE3開發板,其FPGA芯片是StratixIII EP3SL340,擴展板是根據SoC整體驗證方案而設計的PCB板。FPGA原型驗證平臺的硬件架構如圖2所示,為了使FPGA的調試性能增強,該平臺加入了ICE在線調試器,它可以讓驗證人員和軟件開發人員觀察到ARM內核和設計中各個寄存器的狀態信息,并且可以進行單步運行、在線調試等。

2.2 FPGA原型驗證平臺的軟件環境設計

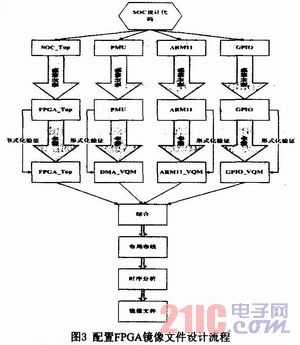

SoC芯片采用的是ASIC工藝流程,ASIC和FPGA在實現結構上是不同的,AISC通常使用綜合工具將RTL級代碼映射到芯片制造廠提供的標準單元上。這些標準單元包括完成邏輯功能的與非門、非門、或非門等基本門單元和完成存儲功能的各類觸發器、鎖存器,以及其它的宏單元。而FPGA器件為了實現可編程功能,通常使用查找表結構實現電路的邏輯功能。本文原型設計流程如圖3所示,在圖示中僅是將部分模塊列出,如PMU和GPIO。

2.2.1 設計代碼的轉換

雖然FPGA和ASIC所用資源和實現方式不同,但在進行原型設計中需要遵循的一個原則就是“尊重原設計”。在FPGA現有資源情況下實現SoC時,盡可能地少改動原SoC設計,在此基礎上需要對原設計做如下轉換:

(1)存儲模塊。存儲單元是必須進行代碼轉換的,ASIC中的存儲單元通常用代工廠所提供的Memory Compiler來定制。如果直接將ASIC代碼中的存儲單元作為FPGA的輸入,通常綜合器是綜合不出來的,即使能綜合出來,也要花費很長時間,并且資源消耗多、性能不好。而FPGA廠商一般提供經過驗證并優化的存儲單元,因此存儲單元要進行代碼轉換。在設計里用FPGA的RAM宏單元來替換ESRAM,SoC芯片里面的DDR PHY是模擬的模塊,此要替換成Altera公司的PHY的IP核。

(2)時鐘和門控。數字電路中,時鐘是整個電路最重要、最特殊的信號。在ASIC中,用布局布線工具來放置時鐘樹,利用代工廠提供的PLL進行時鐘設計。而FPGA中通常已經配置一定數量的PLL宏單元,并有針對時鐘優化的全局時鐘網絡,一般是經過FPGA的特定全局時鐘管腳進入FPGA內部,后經過全局時鐘BUF適配到全局時鐘網絡,這樣的時鐘網絡可以保證相同的時鐘沿到達芯片內部每一個觸發器的延遲時間差異可以忽略不計,因此時鐘單元需要采用FPGA的PLL宏單元和專門的時鐘布線資源來替換。

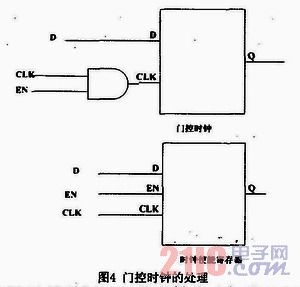

為了減少功耗,SoC設計中使用了門控時鐘(clockgating),如圖4所示,對于FPGA來說這種門控時鐘容易產生毛刺,導致數據不正確,所以在FPGA設計中要使用時鐘使能寄存器代替門控時鐘。

2.2.2 設計綜合

綜合是將較高級抽象層次的描述轉換成較低層次描述,在這里就是把HDL程序轉化成標準的門級結構網表。本設計采用的EDA工具是Sy-nopsys公司的Synplify,將SoC的各個模塊分別進行綜合,綜合時要加約束文件和Altera公司的相應器件的庫文件,產生一個FPGA網表文件。

2.2.3 等價性檢查

形式驗證(Formal Verification)主要用來在覆蓋所有可能輸入情況下,檢查是否與給定的規范一致。等價性檢查(equivalence check-ing)是形式驗證中的一部分,它主要是檢查兩個門級網表(gate-level netlisf)之間是否一致,保證網表處理后不會改變電路的功能,或者檢查RTL和門級網表之間是否一致,保證網表能正確地實現RTL代碼所描述的功能,或者檢查RTL間是否一致,保證兩種RTL描述邏輯一致。這種方法主要是用來尋找實現(Implementation Design)中的缺陷,而不是設計中的缺陷。由于芯片開發中,設計代碼將不斷的更改,都需要

更新FPGA的鏡像文件,這樣在頻繁的鏡像制作過程中,可能會因為環境和設計的更改引出許多實現過程中的錯誤,而本文為了減少這些錯誤,采用的Synopsys公司的Formality工具,主要用于檢查網標和RTL間是否一致,把RTL設計作為Reference Design,而把網標作為Imple-mentation Design,在進行等價性檢查時要加入Altera器件綜合過程中需要的相關庫文件。

2.2.4 設計整合和布局布線

把多個設計文件轉換合并到一個設計庫文件中,并把整合后的設計輸入到Altera公司的QuartuslI工具,將綜合過的網表中的邏輯門映射到FPGA的內部資源中,如ALUT等。

布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內部的物理位置,布線是指利用自動布線軟件使用布線資源選擇路徑試著完成所有的邏輯連接。

2.2.5 時序分析

在設計實現過程中,在映射后需要對一個設計的實際功能塊的延時和估計的布線延時進行時序分析。而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進行時序分析。時序分析不僅可以檢查出我們代碼設計中的時序問題,還可以檢查出由于布局布線產生的時序問題。在本設計中用Altera公司的TimeQuest來進行時序分析,通過對原型設計增加時序約束,提高了工作主頻和減少了關鍵路徑的延時。在設計中經常存在時序違約的情況,這時需要查看違約的關鍵路徑,然后查找原因,進行修改后再進行時序分析,重復整個過程直到滿足要求。

2.2.6 鏡像文件的生成和下載配置

QuartusII經過整合、布局布線等一系列操作后,最終會生成一個配置FPGA的位流文件(.sof洛式),然后利用QuartusII的Programmer工具,通過USB Blaster下載到FPGA,此時FPGA實現了原SoC設計的功能,原型驗證環境搭建完成。

3 FPGA原型驗證測試激勵的設計

測試程序在FPGA基原型驗證中起至關重要的作用,現在的SoC設計很多都采用IP復用的方式,本文所設計出的測試程序有可重用性好、功能覆蓋率高和調試簡易等特點。

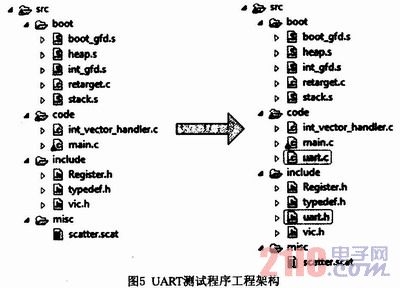

測試程序的基本框架如圖5所示,具體模塊的測試程序只需要根據框架所提供的接口進行編寫相應的測試程序即可,代碼主要由以下四部分組成:

(1)系統啟動部分。主要包含系統的異常向量表和系統啟動后設置ARM內核的配置程序,如各種模式下的堆棧設置、開啟或關閉FIR和IRQ、設定中斷向量表等,在Boot_gfd.s中提供了跳到測試程序的接口。

(2)模塊測試部分。在此部分根據各個模塊的功能,編寫相應的測試函數,系統在執行時會調用這些函數,完成我們各個模塊的功能測試。

(3)頭文件部分。為了方便代碼的編寫和理解,在tyoedef.h文件中對系統的數據類型做了重新定義并包含了部分公用函數的宏定義。一個SoC系統中擁有大量的寄存器,在本設計中用Register.h文件來存放這些寄存器地址的宏定義。

(4)Scatter文件部分。scatter文件是用來描述刪連接器生成映像文件時需要的地址映射信息和加載域信息。

下面以UART模塊為例,在此框架下根據其接口編寫相應的測試程序。

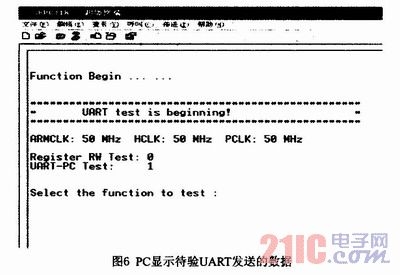

驗證計劃:通過待驗UART與PC進行通信來驗證其功能是否正確,主要驗證的功能點有:1)寄存器讀寫;2)三種工作模式普通模式、自流控模式、LoopBack模式;3)奇偶校驗;4)波特率;5)FIFO觸發級。

測試程序:根據上邊的功能點可以劃分兩個測試的基本的函數,一個是寄存器讀寫的測試函數UART_RWTst(),還有一個就是UART工作配置函數UART_Config(),這個函數提供一個接口,通過這個接口可以配置UART的工作模式、奇偶校驗方式、波特率大小、FIFO觸發級。在更高層的測試應用程序中調用配置程序,變化配置參數,使其與PC進行收發數據,然后查看或比對數據,判別其功能是否正確。測試程序文件結構如圖5所示。

驗證結果:當待驗UART向PC發送數據時,在PC的超級終端會顯示這些數據,UART功能驗證結果可通過觀測或數據比對來判斷,如圖6所示。

4 結論

同樣的測試激勵程序在此原型平臺的執行速度要比SDV(Software driven verification)平臺快4~6個數量級。本驗證平臺的搭建過程中對其進行了形式驗證和時序分析,大大減少了在原型設計中由于FPGA實現而導致的錯誤。本平臺的軟件測試程序具有接口簡單、易調試、可重用性好等特點,筆者在此原型平臺下完成了部分模塊的驗證,有效地提高了驗證效率,縮短了項目的開發周期,加大了流片成功率。