數字濾波器具有比模擬濾波器精度高、穩定、體積小、重量輕、靈活、不要求阻抗匹配,以及能夠實現模擬濾波器無法實現的特殊濾波功能等特點,因此數字濾波器被廣泛應用于圖像處理和識別、語音處理和識別、通信、雷達、人工智能、核技術等多個領域。

數字濾波器的實現方法很多,采用FPGA器件實現具有速度快、效率高、成本低、開發周期短等優點,而且還可以直接使用Altera公司提供的FIR/IIR IP core或采用LPM的設計方法進行設計,使數字濾波器設計變得簡單、可靠。本系統通過一個實例說明如何通過Matlab設計并在FPGA器件上實現IIR橢圓函數濾波器。

1 IIR數字濾波器的Matlab設計

1.1 IIR數字濾波器設計要求

本系統的設計指標如下:模擬信號采樣頻率為2MHz,每周期最少采樣20點,即模擬信號的通帶邊緣頻率為fp=100kHz,阻帶邊緣頻率fs=200kHz,通帶波動Rp≤0.1dB(通帶誤差不大于5%),阻帶衰減As≥42dB。換算為數字域指標為:Wp=0.1π,Ws=0.2π,Rp=0.1dB,As=42dB。

1.2 IIR數字濾波器設計方案

(1)根據設計要求確定濾波器數字域指標

換算為數字域指標為:Wp=0.1π,Ws=0.2π,Rp=0.1dB,As=42dB。

(2)采用Matlab軟件設計濾波器系統函數

IIR濾波器系統函數是采用計算機輔助工程CAE工具進行設計的。系統函數H(z)的計算采用Matlab軟件設計比較方便,其中有兩個現成的函數可以使用:ellipord(Wp/pi,Ws/pi,Rp,As)函數用來計算數字橢圓濾波器的階次N和3dB截止頻率Wn;ellip(N,Rp,As,Wn)函數可以求得直接型橢圓IIR濾波器的各個系數。

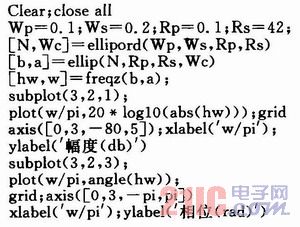

根據要求,設計采用Matlab軟件實現IIR濾波器的源程序如下:

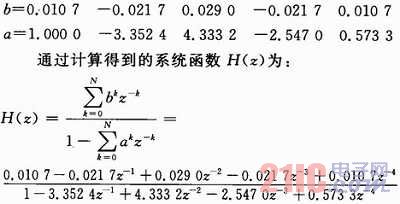

利用Matlab軟件可以得到如下結果:

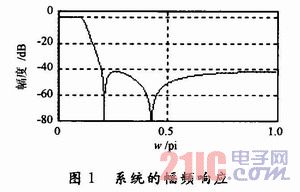

這是一個四階IIR系統,通過Matlab計算出該系統的頻率響應如圖1所示,可見能滿足設計要求。

(3)確定濾波器網絡結構

本設計如果采用直接型結構實現,則需用的乘法器和延遲單元相對較多,而且分子和分母的系數相差較大,需要較多的二進制位數才能實現相應的精度要求。

為了克服上述缺點,采用二階級聯實現。IIR濾波器采用級聯型的網絡結構既可以對各基本節的零點、極點方便地單獨進行調整,又可以降低對二進制數位數的要求。

這里采用Matlab中的“二階部分傳遞函數”tf2sos()完成IIR濾波器直接型網絡結構到級聯型網絡結構的轉換。

將IIR濾波器由直接型變為級聯型的Matlab語言源程序如下:

可以看出,每個二階節的分子、分母系數差異減少了。值得注意的是,在分配二階節的增益時,要保證每個節不會發生運算溢出,可以先用Matlab軟件分析計算來合理安排各節的增益。經過計算,本文采用第一級分配0.1626,第二級分配0.0658,可以保證在要求的輸入范圍,沒有數據溢出發生。

(4)濾波器參數量化

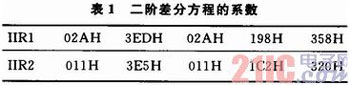

差分方程的量化后各系數如表1所示,這里采用10位定點純小數補碼表示。

2 IIR數字濾波器的FPGA實現

2.1 總體設計方案

根據上述參數計算可知,需要設計的IIR濾波器為2個二階節的系統級聯形式,其二階節系統函數的差分方程均為:

![]()

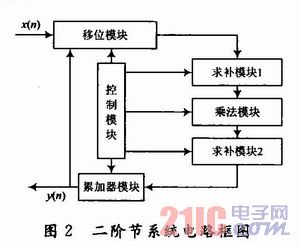

可以看出,一個二階節的實現,需要五次乘法運算、四次加法運算(采用二進制補碼將減法運算變為加法運算),兩個二階節共需要10次乘法運算,所有乘法運算均為無符號數的乘法運算,所以使用時需要先將兩個補碼乘數轉換為無符號數相乘后,再將乘積轉換為補碼乘積輸出,送入累加器求和。根據以上設計思想可知,一個二階節系統均由控制模塊、移位模塊、求補模塊、乘法模塊和累加器模塊等模塊組成,其系統電路框圖如圖2所示。

由于IIR濾波器的兩個節系統電路結構完全相同,只是系數不同,故另一個二階節的設計與此類似。

2.2 主要功能模塊的設計

控制模塊主要用來產生對其他模塊的時序控制。

累加模塊的功能是將10位×1位乘法器的5個輸出數據在10個時鐘周期內累加后,并將結果輸出。

移位模塊主要完成數據交換功能,將輸入數據送入輸入寄存器x(n)中,同時將x(n)寄存器上一時刻的數據送入x(n-1)寄存器,同時又將x(n-1)寄存器上一時刻的數據送入x(n-2)寄存器。同理有y(n)→y(n-1)→y(n-2)。

求補模塊主要根據每路乘法器2個輸入數據的補碼,判斷輸入數據的正負,設置該路乘積結果正負標志位,并對輸入的負數進行求補運算,保證乘積是在2個無符號數之間進行,再根據該路乘積結果正負標志位,對乘積結果進行求補運算,保證送入累加器的數據為補碼。

將設計好的各模塊按照二階節系統電路框圖銜接,即可完成IIR濾波器其中一個二階節系統的設計。只要修改差分方程的系數就可完成另一個二階節系統的設計。

2.3 仿真結果

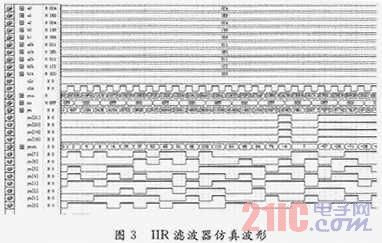

各功能模塊設計、調測完成之后,按照總體設計方案完成IIR濾波器的實現,并下載到Altera公司的EP1C6Q240C8器件上驗證,QuartusⅡ中的仿真結果如圖3所示。

圖3中:xn為輸入信號,采用單極性方波周期信號;頻率為100kHz,在采樣頻率為2MHz時,每個周期采樣20個點,換算成數字域頻率為0.1π;二次諧波的數字頻率為0.2π;yn為濾波輸出。觀察仿真波形可知,所設計的IIR濾波器符合設計要求。為了更直觀地觀察IIR濾波器濾波后的輸出結果,可將仿真波形文件轉換為*.tbl文件,在Matlab中描繪波形。

3 結語

數字濾波器的應用十分廣泛,實現方法很多,運用Matlab語言,能很容易地設計出具有嚴格指標要求的數字濾波器。采用FPGA器件實現數字濾波器的方法,大大縮短了設計周期,降低了成本,提高了設計的可靠性、靈活性,為數字濾波器的設計與實現提供了一種有效的方法。