本文討論的基于AD9957的多波形雷達信號產生器實現方案,融合了RS 232串口通信、FPGA和DDS等多種技術,具有數字化、多功能和可編程的特點,并在模塊化設計方面做了一些探索和嘗試性研究。

1 整體方案設計

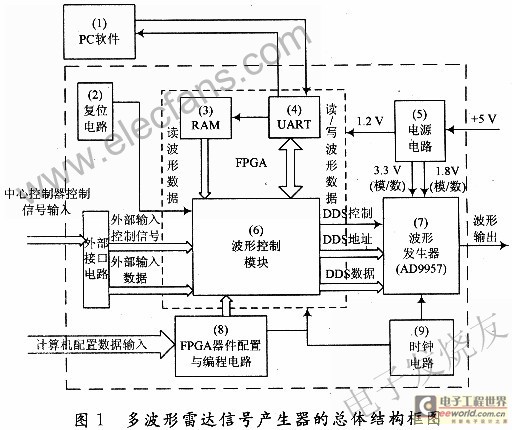

圖1為多波形雷達信號產生器的總體結構框圖。系統主要由PC軟件,波形控制和波形產生三部分構成。圖1中各部分電路簡介如下。

(1)PC軟件編程。應用VC編寫人機交互界面,并用其調用Matlab產生的數據。

(2)復位電路。波形產生器的上電復位或手動復位電路,對波形產生器進行上電初始化或手動初始化。

(3)波形數據庫內存RAM。波形數據庫內存存儲項目要求的所有波形數據,為波形發生器提供需要的波形數據。

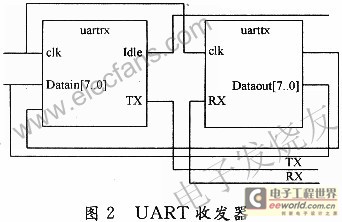

(4)UART收發器。完成PC與FPGA之間的通信。

(5)電源電路。為波形產生器、波形控制模塊提供需要的電源。

(6)波形控制模塊。波形控制模塊接收從接口電路輸入的控制信號,按照系統的要求,完成對波形發生器的波形數據配置,輸出需要的波形信號。

(7)波形發生器。波形發生器是信號產生器的波形信號源。

(8)FPGA器件配置與編程電路。FPGA器件配置與編程完成對FPGA器件的數據編程與配置。

(9)時鐘電路。為波形產生器和FPGA提供工作時鐘。

2 主要功能模塊介紹

2.1 數字正交上變頻芯片AD9957介紹

AD9957是美國AD公司(Analog Devices Inc.)生產的具有18位I,Q數據和通路,內置14位數/模轉換器的數字正交上變頻集成電路。AD9 957具有32位相位累加器;內置1 024×32 b RAM,可實現內部調制功能;內部采用1.8 V和3.3 V供電,超低功耗;內置的低噪聲參考時鐘倍頻器允許用低成本、低頻外部時鐘作為系統時鐘,同時仍可提供優良的動態性能。AD9957有3種工作模式:正交調制模式、單頻輸出模式、插值DAC模式。

2.2 UART收發器設計

本文中PC與FPGA內部RAM間的通信是通過UART收發器完成的。圖2為通過FPGA設計的UART收發器的頂層原理圖,主要由uartrx(接收模塊)和uarttx(發射模塊)兩部分構成。在完成數據傳輸的同時還可以通過集成到Matlab人機界面中的串口調試程序查看FPGA接收到的數據的正確性,可以簡化程序調試過程。

2.3 波形控制模塊

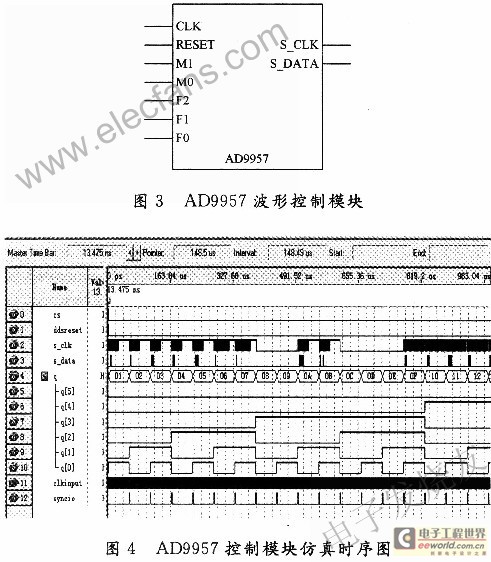

目前波形控制器通常采用單片機、現場可編程門陣列器件和DSP三種方法來實現。基于系統時序控制要求、電路改動與運行可靠性、開發成本及周期等多個方面綜合考慮,在設計中選擇FPGA來實現波形控制電路。FPGA不僅可以解決電子系統小型化、低功耗、高可靠性等問題,而且其開發周期短、開發軟件投入少、可重復編程使用。圖3為AD9957的波形控制模塊。其中M1和MO是模式控制碼,F[2..O]是工作區選擇碼,S_CLK為串口時鐘,S_DATA為串口數據。圖4為AD9957控制模塊仿真時序圖,從圖中可以看出S_DATA和S_CLK是一一對應的。

3 軟件模塊化設計

3.1 設計流程

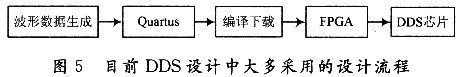

圖5所示為目前大多采用的DDS設計流程,首先要根據系統要求進行波形數據設計,并將其以某種格式儲存成文件,隨后用FPGA設計軟件(Quartus等)進行RAM設計,RAM的對應數據指定為設計的波形數據文件,最后利用邏輯將數據配置到DDS中。如若需要修改波形數據,就需要將上述步驟進行一次,如若多次修改,是比較繁瑣的。

圖6所示為本設計中采用的基帶波形數據產生流程,通過在軟件界面中輸入波形參數,采樣率等數據,通過軟件算法,產生數據并將據送入FPGA內置的RAM中,在FPGA輸入控制信號的控制下,將采樣數據送入DDS芯片中。

3.2 PC軟件

PC機應用軟件完成所有與波形數據相關的運算以及與硬件的數據通信功能,如圖7所示為基于Matlab GUI的應用軟件界面界面部分,其包含以下一些功能:

(1)波形數據的產生。對指定的波形形式、脈寬、帶寬等參數的信號進行仿真,包括時域波形數據的運算和頻譜分析、顯示,并保存數據。目前可生成LFM,NFLM,相位編碼和三角波的信號形式,如需要可添加任意波形。

(2)計算機數據通信。通過計算機串行口連接系統主板以實現基于RS 232接口的異步串行數據通信,接口簡單,配置方便。目的是實現所需波形數據由計算機到波形產生硬件存儲器的下載、校驗。

(3)用戶軟件界面。該界面可完成波形選擇;時寬、帶寬、采樣率、中頻頻率設定;信號時域波形、頻率一時間關系顯示;基帶采樣數據生成、下載等功能。

(4)可移植性。基于Matlab編譯的人機界面的M文件可經Matlab編譯器(cornpiler)轉換為C或C++等不同類型的源代碼,并再次基礎上根據需要生成可獨立運行的應用程序文件,不需要Matlab環境的支持,大大擴展了程序的應用范圍。同時對M文件編譯后,運行速度大大提高。

4 實驗結果

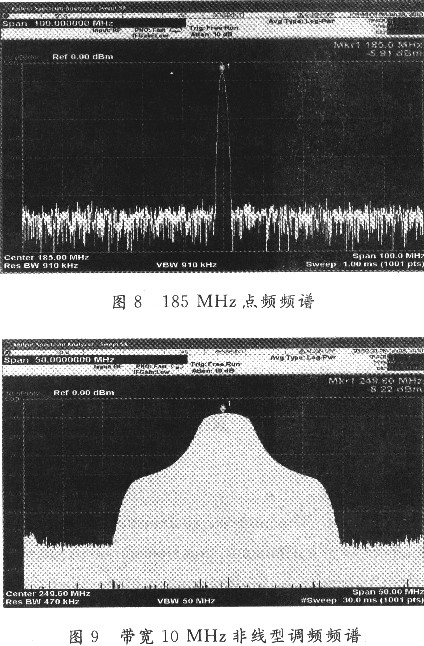

圖8為AD9957工作在單頻輸出模式下,系統時鐘1 GHz,0 dBm,輸出185 MHz點頻頻譜,其雜散優于-70 dBc。圖9為AD9957工作在正交調制模式下,帶寬10 MHz,時寬20μs非線型調頻信號頻譜。由于篇幅所限,線性調頻、相位編碼等信號不在此一一列出。

5 結語

該設計主要討論一種基于DDS的雷達信號的實現方法,系統設計中將軟件與硬件相結合,操作簡便、靈活,并使軟件具有一定的可移植性。Matlab的編程界面使得操作者能夠方便快捷地修改數據。實驗結果證明了基于AD9957的多波形雷達信號產生器實現方法的正確性。由于異步通信數據傳輸的低速率和FPGA內置ROM容量的有限性,因此如果在PC與RAM間要求更高速度的數據傳輸,可以考慮換用PCI總線或計算機網口傳輸;當需要大時寬信號或采樣數據量很大,超出單片FPGA內部存儲器容量,可換用大容量的芯片或外加存儲設備。