機載數據總線技術是現代先進飛機電傳操縱系統和航空電子綜合化最重要的關鍵技術之一,它是計算機網絡技術在航空電子底層的具體實現,決定著飛機性能和航電系統綜合化程度的高低。本書從數據總線技術基礎、計算機網絡OSI七層參考模型兩方面介紹了機載數據總線的基礎技術,用于民用飛機上的ARINC-429、AmNC-629和CSDB機載數據總線,以及應用于軍用飛機上的MIL-S1D-1553B、MIL-STD-1773、STANAG3838/3910機載數據總線,線性令牌傳遞總線LTPB、光纖分布式數據接口FDDI和航空電子統一網絡中可變規模互連接口SCI,光纖通道FC,以及目前最新全雙工交換式以太網AFDX,全面分析了它們的技術特點、協議規范、拓撲結構及通信接口設計方法,并給出了典型的應用實例。

該轉換卡采用Top-Down自頂向下的設計方法,并綜合嵌入式可配置微處理器技術,來對系統進行模塊化設計。頂層模塊則采用圖形設計方式,底層模塊由VerilogHDL語言描述,并利用Quartus lI完成仿真及綜合,然后在ALTERA公司的Cyclone II系列EP2C40芯片來實現。此設計提升了系統的處理速度和穩定性。降低了系統的功耗和成本。

1 MIII總線介紹

MIII總線是某型飛機火控電子設備的專用數據通信總線,又稱第三級總線。MIII總線是單向地址、雙向數據、半雙工通信總線。

MIII總線的接口邏輯信號與電信號之間的邏輯關系是:邏輯“1”對應邏輯高電平;邏輯“0”對應邏輯高電平。

MIII總線接口信號線根據功能可分為三組,即數據通信總線、地址通信總線和信號控制總線。其中,數據通信總線包括0pKlK2~15pKlK-2;地址通信總線:0pAl~15pAl。總線的“輸入”表示從MIII總線轉換板向某飛機火控設備輸出數碼標志,“輸出”則表示從某飛機火控設備向MIII總線轉換板輸入數碼標志。MIII的A1地址選通主要用于跟蹤地址數據與選擇設備,外部寫選通則用于在從MIII總線轉換板向某飛機火控設備傳輸數據和地址時的數碼跟蹤。外部接收選通則用于在從某飛機火控設備向MIII總線轉換板傳輸數據時的數碼跟蹤。

2 RS422通信協議

目前通用的串行通信接口標準主要有RS 232,RS 422和RS 485,其中RS 232屬于單端不平衡傳輸協議,傳輸距離短,抗干擾性差;RS 485與RS 422均為平衡通信接口,但RS 485他只有一對雙絞線,工作于半雙工模式。RS 422屬于一種平衡通信接口,采用全雙工通信模式,傳輸速率高達10 Mb/s,傳輸距離長2 000 m,并允許在一條平衡總線上連接最多10個接收器[1]。由于該類電路的優異性能,RS 422接口芯片已廣泛應用于工業控制、儀器、儀表、多媒體網絡、機電一體化產品等諸多領域。

3 轉換板總體設計

MIII總線轉換板的總體結構如圖l所示,由接口電平轉換電路、總線接口控制邏輯、雙口存儲器和RS422轉換模塊組成。其中總線接口控制單元主要用于地址和數據的收發和寄存,以及接口控制信號和驅動信號的產生等;雙口存儲器RAM用來存放數據和地址,包括MIII總線發送的數據以及PC機發送到MIII總線上的數據和地址;接口電平轉換電路由單雙向驅動電路芯片組成,該電路的作用是提供符合MIII總線要求的驅動電平信號。

3.1 總線轉換設計邏輯

在總線接口控制單元的設計開發中,在嚴格執行國軍標對地面設備的研制規范等要求下,為了保證系統的可靠性,提高系統的可擴展性和性能,并盡可能采用成熟的技術和器件。

基于上述設計原則,MIII總線接口板的硬件電路應采用FPGA器件來實現。采用FPGA實現,FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

設計從系統的整體出發,應用Ouartus II軟件,并采用結構化描述方式來對設計對象的功能特性進行分析,然后自上而下逐步將問題細化,再根據分析的結果劃分功能模塊,并根據電路功能出發使用VerilogHDL語言對各模塊電路進行數據流描述,然后利用Quartus II軟件進行各模塊的功能仿真,再連接各模塊進行邏輯綜合及優化,最后下載到FPGA芯片。

3.2 RS422轉換模塊

此模塊采用SP3490芯片進行RS422通信協議轉換SP3490是一系列+3.3V低功耗的全雙工收發器,它們完全滿足RS-485和RS-422串行協議的要求。這兩個器件與Sipex SP490、SP491的管腳互相兼容,同時兼容通用工業標準規范。SP3490和SP3491由Sipex的BiCMOS工藝制造而成,可實現低功耗操作,但性能不受影響。它們符合RS-485和RS-422串行協議的電氣規范,數據傳輸速率可高達10Mbps(帶負載)。圖2所示為RS422轉換模塊的電路原理圖。

3.3 總線接口控制單元

總線接口控制單元的主要功能是MIII總線地址和數據的收發、轉換、寄存以及接口控制信號和驅動信號的產生等。SOPC)是一種特殊的嵌入式系統:首先它是片上系統(SOC),即由單個芯片完成整個系統的主要邏輯功能;其次,它是可編程系統,具有靈活的設計方式,可裁減、可擴充、可升級,并具備軟硬件在系統可編程的功能。它是用可編程邏輯技術把整個系統放到一塊硅片上,來用于嵌入式系統的研究和電子信息處理。 SOPC是一種特殊的嵌入式系統,它是片上系統(SOC),即由單個芯片完成整個系統的主要邏輯功能但它不是簡單的SOC,它也是可編程系統,具有靈活的設計方式,可裁減、可擴充、可升級,并具備軟硬件在系統可編程的功能。

關鍵字:FPGA RS422 MⅢ總線

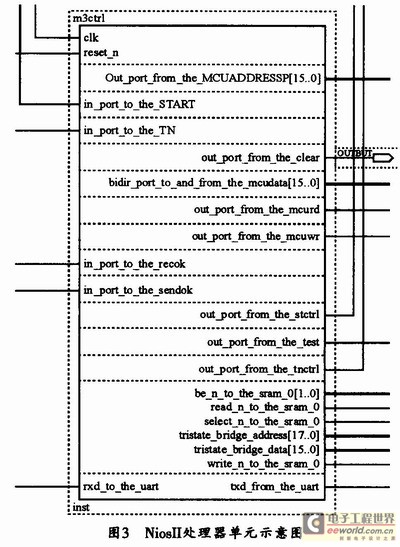

(1)Nios II處理器

Nios 處理器具有32位指令集的第二代片上可編程的軟核處理器, 其最大優勢和特點是模塊化的硬件結構,以及由此帶來的靈活性和可裁減性。相對于傳統的處理器,Nios Ⅱ系統可以在設計階段根據實際的需求來增減外設的數量和種類。設計者可以使用ALTERA 提供的開發工具SOPC Builder, 在PL D器件上創建軟硬件開發的基礎平臺,也即用SOPC Builder創建軟核CPU和參數化的接口總線Avalon。在此基礎上, 可以很快地將硬件系統(包括處理器、存儲器、外設接口和用戶邏輯電路)與常規軟件集成在單一可編程芯片中。而且, SOPC Builder還提供了標準的接口方式,以便用戶將自己的外圍電路做成Nios Ⅱ軟核可以添加的外設模塊。這種設計方式, 更加方便了各類系統的調試。采用QuartusII軟件SOPC Builder生成的Nios II處理器單元如圖3所示。

具體工作時,當數據流向為RS422串口到MIII總線時,NIOSII處理器可將數據從RS422串口接收緩沖存儲器中讀出,并輸出至MIII總線發送緩沖單元中,同時還將數據發送到外部的SRAM中進行存儲;而當數據流向為MIII總線到RS422串口時,其方式其之類似,其不同點是由于MIII總線的傳輸速率遠大于串口的傳輸速率。

(2)MIII總線收發

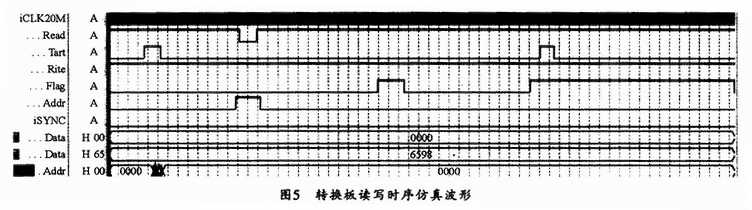

MIII總線收發功能則獨立于Nios系統。它充分利用FPGA可靈活配置的特點,并用VerilogHDL語言實現MIII總線的實時性和可靠性要求較高的關鍵部分,然后模擬MIII總線的邏輯功能,最終實現MIII總線數據、地址的收發以及與Nios系統通過自定義的接口實現通訊。MIII總線的信號時序如圖4所示。

該轉換板的讀寫時序可用VerilogHDL語言描述,然后采用有限狀態機實現上述操作,并用Quartus II進行時序仿真,其仿真波形如圖5所示。

3.4 接口電平轉換電路

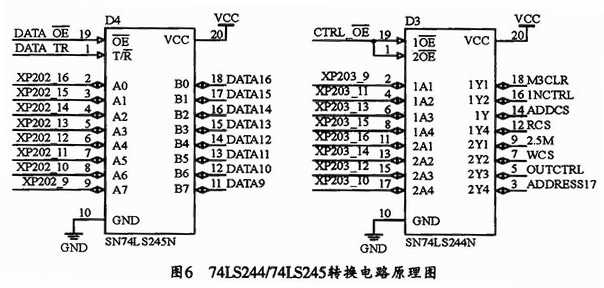

由于FPGA可編程器件的輸入/輸出電平通常是3.3 V,而對接MIII總線設備是OC門輸入/輸出。OC門又稱集電極開路電路,其內部電壓為+5 V。所以,FPGA的輸入/輸出需要進行兩次電壓轉換。

其中,第一次電壓轉換是把FPGA輸入/輸出電平的3.3 V轉換為5 V電平。由于數據信號是讀寫雙向的,而地址和控制信號是單向的(由MIII總線發送到對接MIII總線設備),因此,其數據信號應當用74LS245芯片來進行轉換,而地址和控制線則應用74LS244芯片來轉換,其電路原理如圖6所示。

由于對接MIII總線設備內部是OC門輸入/輸出,而且由于OC門電路的輸出管的集電極懸空,使用時需外接一個上拉電阻到電源。一般情況下,OC門會使用上拉電阻以輸出高電平,此外,為了加大輸出引腳的驅動能力,選擇上拉電阻阻值的原則是降低功耗及芯片的灌電流能力應當足夠大,從而確保足夠的驅動電流足夠小。其具體的電平轉換電路原理圖如圖7所示。

FPGA輸入/輸出的信號,經過以上兩個步驟的電平轉換,就能符合MIII總線對接設備的輸入/輸出信號要求。至此,只需MIII總線轉換板輸入/輸出的地址、數據和控制信號按照MIII總線時序進行收發,就可以實現MIII總線通信。

4 結束語

本文介紹了某型火控電子設備的專用數據通信總線(MIII總線)轉換板的設計方法,給出了MIII總線的總線通信功能。同時介紹了應用F-PGA實現MIII總線部分電路的實現方法。事實上,利用FPGA可簡化系統結構,縮短設計周期,提高系統的性能和可擴展性。目前,該轉換板經過與某型火控電子設備聯調證明,其功能正常,工作穩定,且已得到了用戶好評,收到了良好的社會和經濟效益。