為了擴展VME總線和CAN總線的應用范圍,充分利用兩種總線的不同傳輸特點,采用了模塊設計方法,提出一種基于FPGA和MCU的總線轉換方案。該方案給出了FPGA與上位VME總線部分的VME總線接口設計,利用MCU控制CPLD擴展的多通道CAN節點完成CAN總線部分的設計,還給出軟件實現上的重點、難點和流程。實現了兩種不同總線的轉換,滿足了工業環境對兩種總線混合使用的要求。

CAN(Controller Area Network控制器局域網)以其高性能、高可靠性以及獨特的設計等優點,為分布式控制系統實現各節點之間實時、可靠的數據通信提供了強有力的支持。CAN總線突出的可靠性、實時性和靈活性顯示了它突出的優勢,成為公認的最有前途的總線標準,廣泛地應用于工業自動化、船舶、醫療設備、工業設備等方面。VME(Versa Module Eurocard)是一種通用的計算機總線,結合了Motorola公司Versa總線的電氣標準和在歐洲建立的Eurocard標準的機械形狀因子,是一種開放式架構。其獨特的緊密耦合(Closely coupled)硬件構架,為其外圍系統模塊的設計提供了良好的基礎,使VME總線廣泛地應用于工業控制、軍用系統、航空航天、交通運輸和醫療領域。

本文提出了基于FPGA的VME總線和CAN總線之間的傳輸轉換方案,滿足一些特殊工業環境的需要,具有一定的研究意義和實用價值。

1 轉換系統的硬件設計

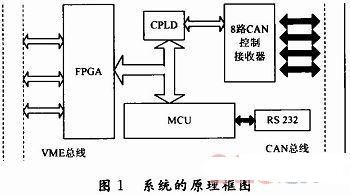

該系統由VME總線接口模塊、CAN總線節點(8路CAN節點)模塊、復雜可編程邏輯器模塊、MCU模塊4部分核心模塊構成。整個系統在一個3U標準的VME板卡上實現,機構緊湊,布局合理。系統的原理框圖如圖1所示。

1.1 VME總線接口模塊

整個系統實現是兩種通信之間的轉換,所以數據的發送都是由上位主機發送的。由于FPGA控制靈活,所以很方便實現與VME總線的連接。文中FPGA器件選用XILINX公司的XC2S200系列的5PQ208,56Kb專用存儲器,最高運行速度200MHz,I/O電壓在3.3~5.5V,地址總線、數據總線,/AS,/IACKIN,/IACKOUT,SYS CLK等可以直接與5PQ208連接。

1.2 CAN總線節點模塊

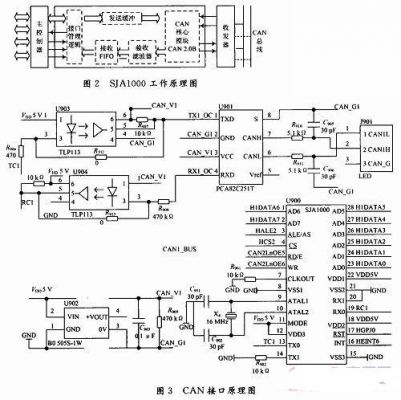

CAN總線節點模塊是該系統中的主要模塊,選用Philips公司生產的SJA1000,它負責連接總線與8路CAN選通主控制器CPLD之間的數據通信,其整個系統功能如圖2所示。收發器選用P82C251T。CAN接口原理如圖3所示。

1.3 復雜可編程邏輯器件(CPLD)模塊

在系統中,由于FPGA的地址總線和數據總線是分開的,而SJA1000的地址和數據線是分時復用的,所以在總線接口上有一定差異,因此選用MAX3000系列可編程邏輯器件EPM3128來進行邏輯變換。該CPLD芯片有豐富的宏單元,80個用戶I/O管腳,管腳間延遲時間是10ns,最高速度可達100MHz,能夠滿足系統設計的需要。可編程邏輯器件在系統中的功能為:轉換FPGA與CAN控制器SJA1000之間的地址總線和數據總線;通過對FPGA的地址線譯碼,擴展CAN控制節點的通道。

1.4 MCU處理器

由于CAN總線的最高傳輸速度是1Mb/s,所以該部分選取宏晶STC12C5A60S2,FLASH程序存儲器為56KB。SRAM為1280B,2個專用的UATR,豐富的CPU資源滿足作為下位機的CPU控制單元,主要完成兩種總線協議的轉換,負責將從FPGA過來的VME總線轉換成CAN總線格式,并傳輸到指定CAN節點;同時也將CPLD選通的CAN通道數據,轉換為FPGA能識別的VME總線格式,并在MCU中斷主機時,將數據反饋給VME主機。

2 轉換系統的軟件設計

2.1 軟件設計思路

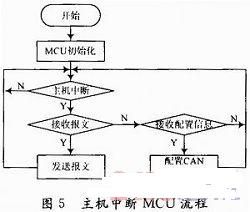

由FPGA構建8個雙口RAM,8路CAN控制器通過這8個雙口RAM與上位VME總線主機進行數據通信,RAM口分別映射到VME總線主機內存地址和MCU存儲器空間中。系統數據傳輸采用MCU中斷主機(VME主機)和主機中斷MCU兩種方式,前者通過觸發主機外部中斷實現,由雙口RAM里面的中斷控制來決定的,在觸發中斷后,提示主機讀取CAN控制器接收到的數據以及CAN控制器的工作狀態。主機中斷MCU方式是通過MCU的外部中斷管腳實現的,是由主機寫入雙口RAM的控制字實現的。觸發該中斷后,MCU就從主機接收要發送的報文,并發送到相應的CAN節點上,并配合主機配置CAN控制器的控制模式。中斷流程如圖4,圖5所示。

2.2 FPGA的軟件設計

在該系統中,數據都由VME主機控制,所以FPGA構造雙口RAM(或者8個區域即可),使VME主機和MCU在RAM中完成數據傳輸。即主機要發送的數據放入RAM中等待MCU提取,同時MCU發送的數據放入RAM中等待VME主機提取。

2.3 CAN節點軟件設計

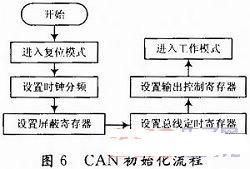

CAN節點軟件是本系統的重點,它包括CAN控制器初始化、報文發送和報文接收3個部分。初始化主要完成設置工作方式、接收方式、屏蔽寄存器、驗收代碼寄存器、波特率和中斷寄存器,并且要在復位模式下進行初始化。初始化流程如圖6所示。

報文發送就是將代發的數據按照CAN總線協議的數據格式,組成一幀一幀的報文,送入SJA1000的發送緩沖區,觸發SJA1000發送即可;報文接收同理。

2.4 MCU轉換程序設計

微控制器程序設計的主要目的是以最快的速度響應中斷請求,完成兩種總線數據的轉換和傳輸。編程時采用模塊化思想,每個模塊完成一定的功能。編程采用Keil公司的Keil μVision3編程工具,設計分為:初始化系統、使能中斷、查詢總線,隨時準備響應MCU中斷主機(VME主機)和主機中斷MCU兩種中斷觸發,并且完成VME總線和CAN總線之間的重組和交換,及時將轉換后的信息相應地傳送給VME主機或者發送到CAN節點上。流程如圖7所示。

3 測試分析

測試過程由VME總線端和CAN總線端互相發送數據包。其中,測試了5組由VME總線發送到CAN總線的數據包;5組由CAN總線發送到VME總線的數據包,記錄如表1所示。由表1測試結果所示,該系統中CAN總線節點都設置在1Mb/s的速率下,系統可以準確地接受和發送數據包。系統正確率之所以會隨通信速度的提高而提高,主要原因在于系統在不同的通信速度時,數據包發送頻率、發送的最小延時間隔都不相同。如果需要進一步的提升數據發送的正確率,需要系統在硬件設計和PCB板制作上分別努力,才能保證盡可能小的干擾,盡可能大的提高系統的穩定性和抗干擾性。

4 結語

該系統充分利用了VME總線和CAN總線的優點,在FPGA和MCU的基礎上實現相應的電路的連接和軟件的設計,成功地完成兩種不同總線之間的轉換,擴展了兩種總線的應用范圍