在采用FPGA進行設計時,您的設計團隊規模是不是越來越大?您是否花費很多時間來嘗試重新使用其他人的設計?您是否花費大量的時間來進行驗證?如果是,那您一定要集中精力,接下來Altera亞太區產品市場經理謝曉東將介紹Altera如何幫助您解決這三個尖銳問題。

Altera亞太區產品市場經理謝曉東

您只需做定制邏輯——解決設計規模難題

隨著各種應用對精度及速度等方面的需求越來越苛刻,芯片復雜度和規模在不斷增加。以Altera高端FPGA Stratix系列為例,其規模(邏輯密度)從2002年到2010年增長了13倍。雖然這能讓系統性能大大提升,但設計的工作量和復雜度也成倍增長,即使可以適當地增加人手,但畢竟設計團隊的規模還是有限的,在設計工具一定的條件下,加上公司對于產品上市時間的壓力越來越大,要按計劃完成項目將會困難重重。

如何提高設計效能呢?提高設計抽象級是一個很實用的方法。從門級到寄存器傳送級(RTL)再到IP級,現在很多設計其實都是一個搭積木的過程,用不同的IP拼成一個系統。但是即使到了IP級別,隨著器件容量的增長、設計復雜度的增加,以及一些全球化的企業要在部門之間、項目之間分享一些子系統的需求不斷增加,現有工具(SOPC Builder)就有待提升。謝曉東經理展示了沒有采用Qsys和采用Qsys所需要做的設計工作對比圖,如圖1所示。可見,Altera系統級集成工具Qsys能幫助設計者把標準內核(存儲、標準接口、處理器等)和膠合邏輯(用來做仲裁、中斷控制、拓撲結構、帶寬匹配、互聯、橋接等)做好,大大減輕了工作量。Qsys讓設計者把精力集中在定制邏輯上,這也是客戶最關心的部分,用來做差異化,實現產品價值。

圖1 沒有采用Qsys和采用Qsys所需要做的設計工作對比圖

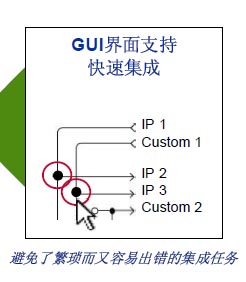

針對標準內核,Altera提供100多種Qsys兼容IP,如接口協議IP(PCIe、TSE)、存儲器IP(DDR、DDR2、DDR3)、視頻和圖像處理IP、嵌入式IP(JTAG、UART、SPI、RS232)以及處理器IP。Qsys還自動完成繁瑣、容易出錯的集成任務,并且提供GUI界面支持快速集成。謝經理特別提到:“Altera致力于一個工具能支持所有的處理器。Altera自己擁有兩種:帶ARM Cortex-A9內核的雙核SoC FPGA以及Nios II 軟核處理器。此外還有Altera嵌入式聯盟所支持的軟核處理器(用FPGA模擬CPU),如MIPS、MIPS32、ARM Cortex-M1(ARM的策略就是希望把Cortex-M1放在FPGA上)、Nios II SC DO-254(對魯棒性要求很高的應用,如軍事)和Freescale Coldfire V1,如果希望用Nios II去做ASIC,Synopsys也提供License。

在膠合邏輯方面,Qsys自動完成繁瑣、容易出錯的集成任務。Qsys有圖形化界面,接口(如時鐘、復位,中斷、抑制)能在GUI界面上快速集成,設計者只要把鼠標放在兩個IP之間的接口,一點就可以了,操作十分簡單,如圖2所示。

圖2 Qsys圖形化界面

NoC和子系統級的設計重用——解決設計重用難題

設計者常常需要對原先成熟的設計進行更新和改進,也要使用別人設計的IP,會遇到設計重用帶來的問題:一般需要重新設計接口以及需對各種修改過的設計提供支持。而Qsys提供Avalon總線接口(FPGA的)以及ARM的AMBA AXI3、AXI4標準總線接口,Qsys的芯片網絡(NoC)體系結構可以幫助做FPGA與ARM之間的高性能互聯,例如,對于Altera新推出的集成了ARM Cortex-A9處理器的SoC FPGA,Qsys將會發揮很大的作用。

Qsys還提供組件編輯器工具,可以把自己設計的RTL引入Qsys中,封裝成一個IP來用。而且操作也是很簡單的圖形化界面。

Qsys在設計重用上的最大特色就是能做到子系統級別的設計重用。在設計一個超大系統時, 由于IP很多,用SOPC Builder時的界面會非常長,如果出現問題(如互聯),要找前面的IP非常難,而Qsys可以做子系統的打包,把某一些IP打包成一個子系統(留一些接口出來),這樣的層次化設計將會極大地方便設計人員。特別是一些國際化公司要在全球范圍內共享設計,例如PCIe 的子系統,其中有PCIe 的IP、DMA 以及其他邏輯,可以通過Qsys把這部分打包之后重用,這是之前IP級設計工具做不到的。這也是一些國際化的客戶選擇Altera的原因。

定制GUI系統控制臺——解決驗證難題

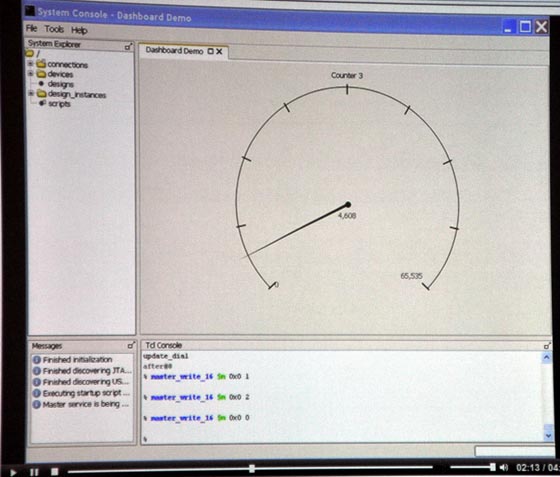

很多FPGA設計者都反饋:設計雖然很快的,但是系統驗證和調試是很痛苦的過程。業界很多調試工具都是基于寄存器的調試,如果出問題要自己去分析問題大概出現在設計的哪一部分,再用SignalTap工具逐個寄存器進行讀寫操作,這使得工作量非常大,也存著許多不確定性。Qsys中有一個系統級調試工具——系統控制臺,它提高了調試的抽象級,把設計看成不同的子模塊,通過在總線上對地址進行讀寫操作,鎖定問題出現在哪個模塊,再用SignalTap去調試,從而大幅度縮短了驗證時間。謝曉東表示:“其實,Altera很多調試工具,如收發器、外部存儲器接口工具等,就是基于系統控制臺開發出來的。”

很多時候調試都是很枯燥的命令行,而系統控制臺的另一大特點就解決了這個問題,它提供定制圖形用戶界面,讓客戶定制自己喜歡的界面,使調試變得簡單和享受。

圖3 Qsys定制GUI系統控制臺

Qsys巡回研討會正在進行中

為了讓更多的工程師切身體會Qsys的優勢,Altera將在亞太區15個主要城市舉辦Qsys研討會。研討會的形式不單是演說,主要是可以讓工程師們實際操作。他們可以使用Qsys開發一個嵌入式設計,并且通過實驗看到在Qsys中使用PCIe的優勢,讓工程師在半小時之內開發一個基于PCIe的設計。謝曉東也特別讓記者體驗了一下Qsys的PCIe和DDR3參考設計。此外,Qsys的培訓資料都是中文版的。

需要提醒廣大使用Altera SOPC Builder的工程師們,雖然在老設計上還是可以用SOPC Builder去設計,但是Altera今后不會再更新SOPC Builder 的IP和支持器件,新的IP和器件都是放在Qsys上,Altera將為客戶從SOPC Builder轉到Qsys提供很多支持,如設計案例、文檔和培訓等。打開以前的SOPC Builder,就會提示是否轉到Qsys,系統會幫你自動轉換,當然有些地方需要少許修改,但不會花很長時間。Qsys代替SOPC Builder是必然的,所以趕緊開始使用吧!

圖4 給工程師培訓時用的開發板,由Altera合作伙伴友晶科技Terasic.提供的