I.概述

本文將:

. 總結針對計算應用的典型同步降壓調節器負載設計規范;Tjcn、負載電流、DC和瞬態調節

. 簡單概述帶來典型的每相20 - 30 A電流的因素;工作頻率、瞬態響應和效率

. 解釋三要素概念=>額定輸出電流由三個因素確定:輸出功率/電流、效率,以及Tjcn-amb熱阻抗

. 總結功率級(Power Stage)器件設計特性,優化效率和熱阻抗

. 展示在效率、功率損耗和溫升等方面的測量數據

. 解釋采用如何測量安裝在電源板上的零部件的熱阻抗

. 探討受輸出電壓影響的效率和熱阻抗,及所產生的HS/LS占空比(duty cycle)

. 結論

II.典型的同步降壓計算負載規范

針對典型的同步降壓調節器計算負載需求,對功率級系列部件進行優化。這些應用將具有大范圍的電流水平且可以是單相或者多相。通過在每相基準上比較電源系統(power train)規范,我們注意到,許多設計顯示了共同的工作范圍。典型的每相電源系統規范為:

. 電源系統占空比為5 % - 40 %

. 工作頻率:300 kHz到600 kHz

. 負載功率:25 W

. 負載電流:25 A

針對此設計范圍,已對部件的功率級設定進行了優化。選擇了最通用的設計作為目標工作點- 12 Vin, 1 V / 25 A 輸出。

III.決定負載規范的因素

上述的參考設計規范—占空比、頻率、功率和電流—是通過平衡相當廣泛的電氣和散熱限制來設定的。對于典型的多相CPU電源,這些限制包括:

. 靜態負載運行期間的輸出峰峰值電壓紋波

. 負載瞬變期間的輸出電壓偏移

. 系統溫升極限

. 硅Tjcn設計極限

. 輸入電流紋波

將會討論每個設計因素的影響,以及折衷方案如何推動電源系統規范達到每相電流極限和工作頻率。

滿足這些系統性能目標需要平衡相互沖突的要求。對于穩態和瞬態負載,設計必須具有低輸出電壓紋波。每相DC電流、峰峰值紋波電流和工作頻率都會影響輸出調節。通過增加電源系統電感,可以減少靜態輸入和輸出紋波,但較大的電感將會降低供電瞬態性能。較高的工作頻率將減少紋波并改進瞬態性能,但較高的工作頻率將會引起效率降低,因為增加了開關損耗,由此增加了器件的溫升。

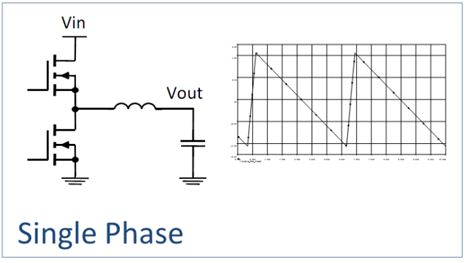

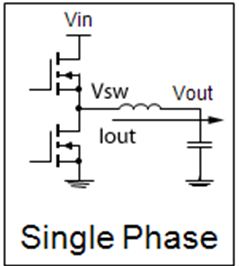

用于解決此局限的設計方法就是將總負載電流分成幾個并聯的電源系統,且允許每個都有相對高的紋波電流值。圖1和圖2顯示了單相設計與多相設計的紋波電流比較。

圖1. 單相紋波電流

圖2. 多相紋波電流

多相設計的優勢為幾個低頻單相電源系統的電流交錯。這帶來了較低的峰峰值紋波和較高的紋波頻率。對于給定的紋波電壓,還允許減少輸出電容數。對于每一個電源系統,可以使用小電感來實現良好的瞬態響應。但這將導致紋波的增加。通過相電流的交錯,將減少產生的輸出電流紋波,同時仍然允許良好的瞬態響應。另外,大多數控制器具有瞬態運行模式,允許對準各個相位,用于優化轉換速率。

對于給定的電感/電容元件的設置,較高的工作頻率將導致紋波減少并改進瞬態響應;或者設計人員可以選擇保持紋波恒定,并減少電感和輸出電容元件的尺寸。

注意,通過增加電源頻率或減少輸出電感,無法單獨滿足CPU負載的初始急速瞬態階段要求。需要低阻抗陶瓷電容的網格運作來滿足初始瞬態。但在減少剩余的輸出電容方面,更快的電源瞬態響應是有效的。

典型的每相25A、300kHz – 600kHz電源系統規格,是基于這些限制條件的最佳平衡。因此針對這一電流和頻率范圍所設計的器件將涵蓋范圍廣泛的應用。

IV.三要素

當新的部件發布時,我們常常會詢問它的額定電流。飛兆半導體的數據表使用行業標準方法來規定額定電流,基于元件放置在極大的散熱器上,并測量每個芯片發熱達到其額定Tjcn額定值時所需要的電流。這使得可替換元件之間容易比較,但在實際電源應用中對部件的有效電流能力的理解有些局限。

就像一只三條腿的凳子,部件的有效額定電流將基于三個不同因素的平衡:

. 輸出功率

. 效率

. Jcn-Ambient 熱阻抗

如圖3所示,對于在期望的額定電流上運行的部件,它必須滿足這三個限制因素的平衡;功率(Vout x Iout)、效率和熱阻抗。圖3中,25 A的灰色平面與曲面相交部分顯示了在Vout = 1 V時,實現25 A所需的效率和阻抗組合。例如,假如設計的效率為90%,那么它必須具有低于14 C / W的熱阻抗,以便保持溫升低于40 C。

圖3. 額定電流與效率和熱阻抗的比較

由于在過去的五年里器件性能得到了改進, 25 A輸出設計已經從一個三或四個FET D-PAK設計演變為一個雙FET結構,并且現在已經演變為單一的5 mm x 6 mm功率級雙芯片。圖4顯示了在電源系統尺寸方面的顯著減少,這些已在這段時間內發生。

圖4. 對于25 A設計的電源系統演變

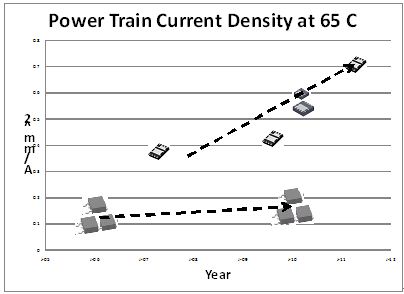

可以使用A/mm^2來表述此尺寸方面的改進,這里mm^2尺寸是安裝部件所需的線路板面積尺寸。這包括封裝外形加上焊接位占位面積。圖5顯示了在密度方面的演變,它們是從一系列飛兆評測板上觀測到的,而這些評測板在過去五年里一直進行測試。

圖5. 電源系統電流密度

在以下章節中,將回顧飛兆半導體能夠實現功率密度的顯著提高的設計改進。

V.功率級器件設計具有優化效率和熱阻抗的特性

如圖3所示,如果需要增加功率密度,就必須通過降低功率損耗、改進熱阻抗或者同時改進這兩者來提高FET效率。

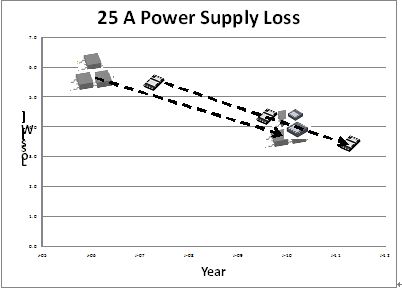

回到圖5中所引用的電源設置,可以標出它們的損耗。圖6顯示出對于圖5中所引用的電源設置,損耗減少了。

圖6.電源損耗

飛兆半導體最新發布的功率級部件顯示了全系列產品的最佳功率密度性能。

功率級系列產品的功率改進是以FET效率和封裝熱阻抗設計這兩者為基礎的。

電源效率受以下因素影響:

. FET硅性能[1]

. 封裝和線路板寄生參數[2][3]

影響硅器件最大負載性能的關鍵來源是低側(Low Side,LS) FET傳導損耗和高側(High Side,HS) FET傳導加開關損耗。LS FET的開關損耗也是一個重要因素。

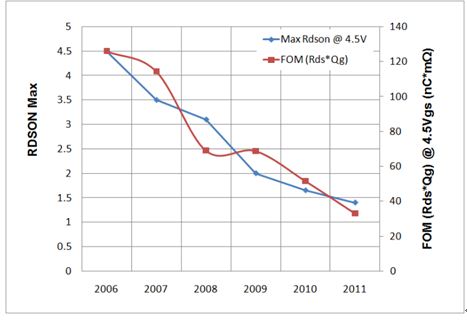

如圖7所示為與時間相對應的Rds和Rds*Qg的改進,隨著時間的推進,飛兆半導體已經在這兩者上實現了顯著改進。傳導損耗與RDSON成正比,而開關損耗與Rds*Qg直接相關。因此,飛兆半導體實現的設計改進減小了這兩個損耗因素。通過減少硅器件特有的導通電阻(m? cm2)來降低Rds。這提供了更多選項,可使用較小的芯片來達到期望的Rds。由于較小的芯片具有較低的柵極電荷,這還將帶來較低的開關損耗。在開關損耗中起作用的其它指標還有Qgd、Coss、Rg和跨導(transconductance)。采用此新一代部件,飛兆半導體能夠縮小芯片尺寸,并在全部指標設置上進行改進。

圖7. 與時間對應的Rds和Rds*Qg改進

FET振鈴性能是一個經常被忽視的因素,但也會影響效率。飛兆半導體的LV FET已包含了專有的(專利申請中)自衰減特性,可使峰值過沖和振鈴持續時間最小化,如圖8所示。采用典型的基于飛兆半導體器件的設計,則無需緩沖電路。對于競爭對手解決方案,其緩沖器可能降低最高效率多達1%。

圖8.飛兆半導體FET中的內在緩沖器

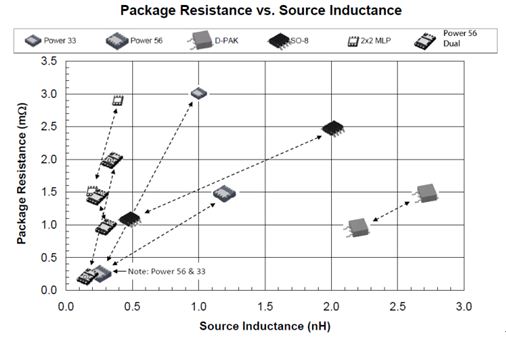

在電源性能中封裝屬性也起到關鍵作用。如圖9和圖10所示,顯著的性能改進已經實現,因為封裝設計已經從D-PAK / SO-8設計發展到分立Power56,然后到雙Power56。D-PAK部件具有低熱阻,但源極電感高。由于使用多源極粘接線,SO-8部件提供了低的源極電感,但Jcn-Case熱阻抗高。

圖9. 封裝電阻對比源極電感

圖10. 熱阻Jcn-Ambient對比Jcn- Case

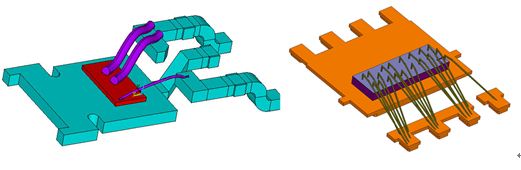

Power56系列則結合了這兩者的最佳屬性,具有良好的Jcn-Case熱阻抗和低源極電感。如圖11所示,Power56封裝具有大導熱面積與大量源極粘接線相結合的優勢。

圖11. D-PAK對比Power56結構

功率級雙封裝則將其帶到了一個新的水平上,消除了HS和LS FET間的線路板寄生電阻和電感。單單此電感可以輕易達到0.1 – 0.2 nH,與分立Power 56封裝的值基本相同。

圖12顯示了功率級非對稱雙FET設計的演變。該功率級在最小的占位面積封裝中結合了分立FET D-PAK和SO-8設計的最佳特性。在該功率級中,HS FET結合了低電感的多源極粘接線和低熱阻抗的金屬漏極襯片。LS FET采用低熱阻抗的大金屬漏極襯片。飛兆半導體的第一代功率級部件使用多個粘接線來連接LS芯片源極。第二代使用固體金屬夾來連接LS源極,從而改進封裝熱性能并減少LS源電感。功率級雙FET設計也消除了HS和LS FET間的線路板互連電阻和電感。

圖12. 功率級封裝的演變

VI.針對效率、功率損耗和溫升的測量數據

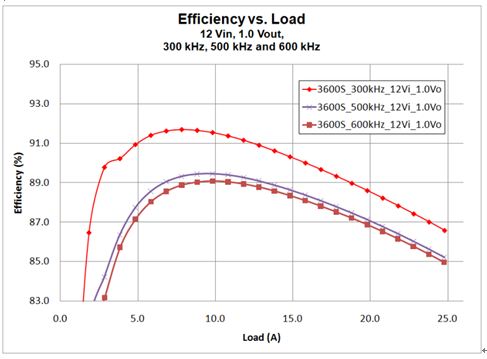

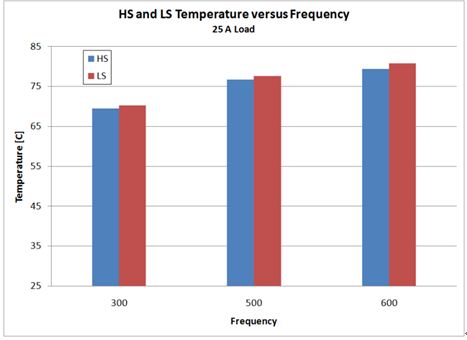

在FET FOM和封裝結構中采用最新的重要改進,飛兆半導體現在能夠在單一Power 56封裝空間中提供25 A解決方案。圖13和圖14顯示了在評估設計中測量的功率級部件的高效率和低工作溫度。

圖13. 功率級FDMS3600S的效率

圖14. HS和LS器件的溫度與頻率對比

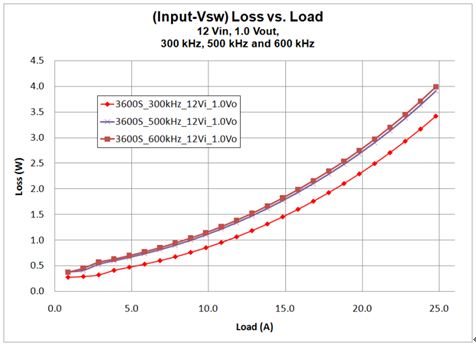

功率損耗通常從測試板的輸入到輸出中測得,但對于估算熱負載,專注于FET損耗和Tjcn上所產生的溫升是非常有用的。為做到這點,通過減去電感功率損耗來調整功率損耗估算值,如圖15所示。對于飛兆半導體的效率測量,除了測量Vout,也可測量Vsw 的DC平均值。從功率損耗估算值中減去(Vsw-Vout)*Iout,可提供更好的FET損耗估算值。此近似值非常適用于中到大電流水平,這里電感RMS和DC電流接近相等。

圖15. 估算電感損耗

圖16顯示了從測試板輸入腳到輸出電感的功率損耗。

圖16. 輸入-Vsw功率損耗

此損耗包括幾個因素;柵極驅動器損耗、線路板傳導損耗和FET損耗。在較高的功率水平上,溫升成為限制,FET開關和傳導損耗將占主要地位,還包括線路板銅損耗。在大負載下,柵極驅動損耗將不再是一個重要因素。

如圖17所示,由于功率耗散和熱阻抗不同,封裝內的HS和LS將在略有不同的結溫下工作。

圖17. 在600 kHz, 25 A負載下的FDMS3600S

VII.熱阻抗測量數據

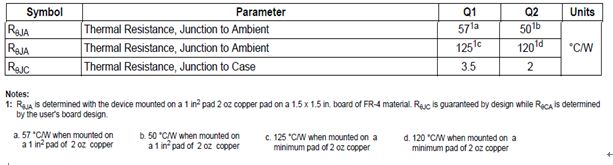

對于安裝在標準測試板上的部件,功率級數據表將顯示Jcn-Case和Jcn-Amb熱阻抗規范。

圖18. 熱阻抗規范

但這些數值僅適用于安裝在測試夾具上的雙FET封裝,且只有一個芯片供電。對于部件安裝在電源板上的多FET,其性能和兩芯片供電有著更復雜的關系。

如圖18所指出的,Jcn-Amb阻抗將受Case-Amb成分的強大影響。這是電源板的熱阻抗,且由實際的電源板設計來確定。一個額外的復雜因素就是設計內的功率耗散位置間的熱耦合。如果HS和LS FET均有功率損耗,一個芯片的溫升將感應第二個芯片的溫升且成比例。估算所產生的芯片溫度變化是一項困難的工作。

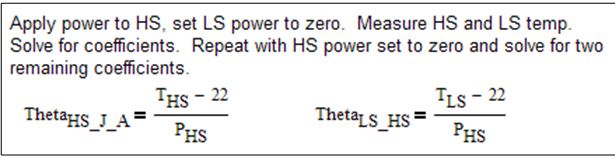

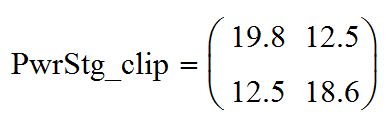

針對安裝在實際應用板上的FET封裝,飛兆半導體用于模擬交叉發熱的方法就是測量熱阻抗矩陣。

模擬兩個FET的一個簡單矩陣可以提供對熱性能的很好的了解。一旦確定矩陣,對于任何HS和LS功率損耗組合,都可以計算單個FET芯片的溫度。

圖19顯示了矩陣的一個實例,針對給出的HS/LS功率損耗比例,如何使用矩陣來計算單個芯片的溫度。在此實例中,Tjcn假定為22 C。

圖19. 熱阻抗矩陣

為求出矩陣中的單個元素,圖19的公式改寫為如圖20中所示的公式。在此實例中,假定環境溫度為22 C。

圖20. 求出矩陣系數

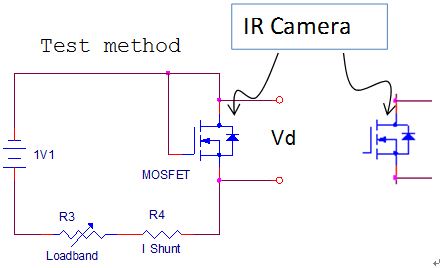

圖20顯示可以通過每次給一個器件供電來確定熱矩陣的元素,然后測量板上安裝部件的兩個芯片所產生的溫升。進行該測試的一個簡便方法是,在一個FET的體二極管中施加電流,然后使用IR照相,測量兩個FET的溫度。圖21所示為測試設置。

圖21. 熱阻抗測試方法

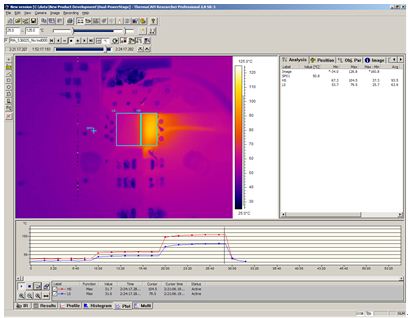

圖22顯示了一個測量實例。飛兆半導體通過使用自動化效率測量設備進行此測量,按照每步10分鐘,逐步改變負載,通過幾個功率水平。劃出直線使其與所產生的數據相符,溫度與功率測量值相比的斜率就是期望的矩陣值。

圖22. 在功率級封裝中使一個FET發熱

此測量將描述安裝在實際板上的部件熱阻抗。為達到最好的準確度,不可去除關鍵功率元件,比如此測試中的輸出電感。該電感將充當熱流路徑,并且將略微降低Jcn-Amb阻抗。

圖23顯示了此計算的一個實例。所產生矩陣的對角元素將會是每個芯片的Jcn-Amb阻抗,非對角元素將模擬芯片間的發熱。圖23和圖24顯示了測量數據和所產生的矩陣項實例。通過取兩測量項平均值來計算非對角項。

圖23. 計算熱矩陣系數

圖24. 測量熱矩陣

因為HS芯片較小且封裝片也較小,因而它的阻抗略高。

VIII.使用熱矩陣作為分析工具

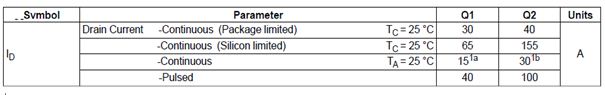

典型的FET數據表將列出幾個不同數字作為器件的額定電流。圖25顯示了一組典型的規范值。這些數值都假定部件放置在規定的測試夾具中,且電源施加在兩個芯片中的一個上。

圖25. 功率級額定電流

電源設計的最大額定電流通常由FET的Tjcn來規定。對于連續運行在150 C上的FET,通常由供應商來給出額定值。但因為電源板允許的工作溫度和其它限制,客戶經常選擇較低的溫度極限,比如105 C。他們的設計還將規定一個最高的環境溫度,比如65 C。因此,FET的最大允許溫升可能僅為40 C。如果設計中兩個FET中的任一個達到了該極限,那么設計就會處于其最大工作電流上。

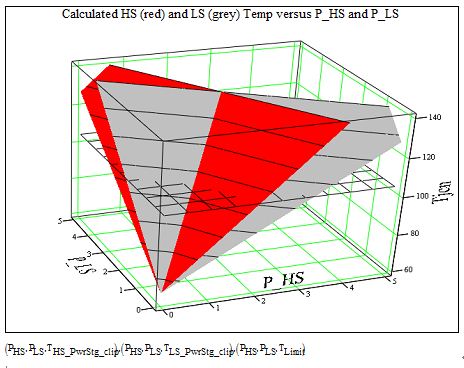

在圖26的標繪中,對于每一個芯片,我們顯示了Tjcn < 105 C的設計極限如何與預測溫度相交。設計極限將由Tjcn溫度極限與兩個平面的交叉點來設定。

注意,封裝功率耗散極限轉變為HS對LS功率變化比。相比于通過LS芯片面積輸出1 W,通過HS芯片面積輸出1 W產生的溫升將會較大。

計算機輔助電路設計程序(PSPICE)和混合模式仿真等程序可以用于估算器件損耗[3]。然后可以使用熱矩陣來預測每個FET的Tjcn。使用熱矩陣來預測FET的Tjcn可提供幾方面的了解。因為有兩個發熱元件且它們之間存在交叉耦合,該結構不再具有一個簡單固定的Jcn-Amb阻抗指標。有效的封裝熱阻抗將是變化的,取決于HS和LS的功率比例。為預測每個芯片的最高溫度,設計人員必須使用矩陣來計算Tjcn。

圖26. HS和LS溫度與功率對比

對于一系列HS / LS功率級,可以使用矩陣來計算FET對的最高Tjcn。而后,此數據可以轉化為一組等高線,標繪出溫度與功率的對比。圖27顯示了一個實例。典型的12 V -> 1.1 V電源設計將具有HS /LS功率分配,范圍在30/70 到40/60內。如等高線顯示,功率級設計的最大功率處理能力將隨HS / LS功率損耗的比例變化而變化。針對章節II中引用的典型設計范圍,已選擇功率級HS和LS FET來提供優化的性能。

功率等高線還可用于判斷散熱封裝設計的改進。圖27顯示的等高線可用于飛兆半導體的當代功率級部件與先前一代的對比。這兩者的結構細節如圖12所示。對于LS FET源極連接,先前一代部件使用粘接線。而當代部件使用固體金屬夾。圖27顯示了通過此新設計實現的改進的熱性能。在整個HS/LS功率范圍內,新封裝能夠實現較高的凈功率水平耗散。

圖27. 功率等高線

開關頻率和電壓比(Vout/Vin)等設計因素都將影響HS與LS功率損耗比。圖28顯示了測量數據,這里相同的功率級部件運行在幾個不同的輸出電壓上。這兩個芯片的溫度由單個FET和來自相鄰FET的熱耦合這兩者來確定。注意,在此實例中,隨著Vo增加,最高溫度從LS芯片轉到HS芯片上。

圖28. HS和LS測量溫度與Vo的對比

IX.結論

在單一Power56封裝中安裝25A電源系統解決方案是一項挑戰性任務。僅在幾年前,25A解決方案需要三到四個FET。有了FET FOM、減少封裝寄生和封裝熱性能方面的最新進展,25A功率級雙芯片方案現已成為現實。

通過使用熱矩陣分析,我們已經說明了在實際應用中如何比較封裝的功率處理能力,以及最大功率和額定電流如何隨HS / LS功率比例而變化。在一系列輸出電壓和工作頻率下可應用該設計,這些知識是非常重要的。