0 引言

RLC單獨測量的方法有很多,對電阻的測量最為簡單。電容電感對時變信號敏感,可將電容電感轉換成與電量、時間和頻率相關的物理量,通過對電量、時間或頻率的測量獲得電感電容值。目前通過不同的模擬電橋電路可以實現RLC參數的較精確測量,在測量時需要預先甄別RLC類型再選著合適的測量電橋和測量頻率,因此測量時智能化水平不高。隨著數字信號處理技術的成熟,以及AD芯片性能的提升,采用數字信號處理的方法逐漸替代了傳統模擬測量信號相位、頻率、幅度信息,降低了模擬器件的使用量和系統復雜程度,便于智能化控制。

基于MSP430的智能LRC測量系統,利用高速數模轉換電路將信號量化處理,FPGA進行高速數字信號處理獲得信號相位、幅值信息。這樣不僅減少了模擬器件的數量,也減少了信號傳輸中的衰減和模擬器件溫度變化以及供電變化等引入的附加干擾。此外,采用MSP430單片機的智能控制技術,使測量系統具備自動分析、識別、計算的能力。用戶只需開機接入待測量元件即可獲得待測元件的RLC值。

1 系統總體設計

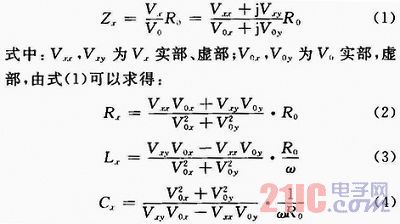

系統采用矢量比例法測量RLC的方法,如圖1所示。圖中參考阻抗用標準阻抗R0代替Z0,可推導出:

由式(2)~(4)可知,只要知道Vx,V0實部、虛部就可以測量待測R,L和C的值。

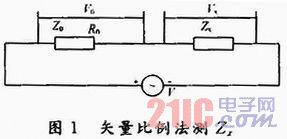

系統測量過程中總體信號流程如圖2所示,系統首先需要產生頻率非常穩定的正弦波作為圖1的信號源,接入待測元件后,由于V0信號不便直接測量,因此需要減法電路做差后求得V0。為了保證測量精度,系統采用高速高精度的AD芯片進行兩通道交流信號同步采樣,采樣前需要將信號差分化處理。當采樣完成后,數據傳給FPGA進行傅里葉變換。利用傅里葉分析法,對采樣的信號進行FFT變換就能分離出V0,Vx的實部和虛部。FPGA分離出的V0,Vx的實部和虛部數據經單片機MSP430F4617計算,結果將顯示在液晶顯示器上。

2 系統硬件設計

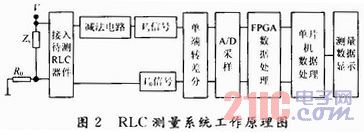

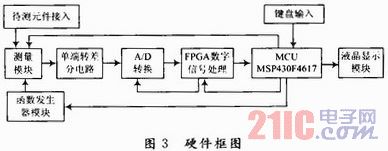

測量儀的硬件由MCU模塊、FPGA數據處理模塊、A/D采樣模塊、單端轉差分模塊、測量接入模塊、函數發生器模塊、鍵盤模塊、液晶顯示模塊構成,硬件框圖如圖3所示。

2.1 系統主控制MCU模塊

儀器的控制核心采用MSP430F4617單片機,該芯片有2個16位定時模塊單元,多路12位A/D采樣轉換模塊,12位D/A轉換模塊,多路時鐘系統,存儲容量大,數量多的I/O口,在整個系統中是利用率比較高的器件。在系統測量過程中,首先用于分析測量數據,根據測量值與沒定參數比較,然后再反饋給控制測量模塊選擇合適R0達到最佳測量狀態。根據初步測量結果反饋控制函數發生器以及內部定時器選擇合適函數頻率,進行精確的測量,最終控制液晶顯示器將測量的元件的電學特性RLC值輸出顯示。

2.2 FPGA數字信號處理模塊

FPGA芯片采用XC3S200A芯片,系統中高速A/D采樣芯片工作頻率較高它的控制時鐘以及采樣時序主要由FPGA控制產生,同時利用FPGA處理數字信號速度快的特點對圖3兩路信號V0,Vx進行FFT運算分離出實部虛部信息,并將數據傳送給單片機。

2.3 A/D采樣模塊

為了減小圖3中2個模擬輸入信號V0,Vx的相位誤差,系統采用AD7862高速、低功耗、雙核12位模數轉換器(ADC)芯片進行采樣。該器件內置2個4μs逐次逼近型A/D轉換器、兩個采樣保持放大器、一個2.5 V內部基準電壓源和一個高速并行接口,它有4個模擬輸入組成2個通道A和B(分別用于采樣V0、Vx信號),每個通道的兩個輸入(VA1與VA2或VB1與VB2)可同時進行采樣和轉換,通過A0(FPGA控制)作為輸入選擇通道,采樣時序由FPGA提供。

2.4 單端轉差分電路

后級A/D采樣電路需要在差分輸入狀態下達到最佳采樣精度,所以需要將前級測量模塊產生的V0,Vx差分化預處理,這里采用全差動運算放大器THS4503進行轉換,THS4503具有非常卓越的線性度,輸出模式可調,電壓工作范圍寬(5V,5V,12V,15V)工作帶寬可達370MHz,轉換速度極快達到2 800 V/s。另外,還需要REF2330芯片為THS4503以及A/D采樣模塊提供基準電壓。

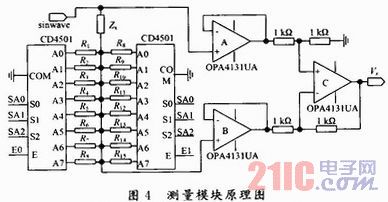

2.5 測量模塊

測量模塊是待測元件與標準R0分壓部分,主要包括減法電路求Vx、減法求V0電路以及標準電阻R0選擇電路,如圖4所示。由于圖2中的Vx不便直接測量,所以通過減法電路來求Vx。當圖4減法電路求得Vx的同時,也引入了新的環境變量,因此,使V0也通過相同的電路環境以減小系統誤差。可以分析得出,當圖1中Vx/V0為1:1時測量精度最高,所以需要調整R0與待測元件的分壓接近1:1來保證測量精度。標準電阻R0

由MSP430單片機控制的模擬開關CD4051進行軟件選擇。

2.6 函數發生器模塊

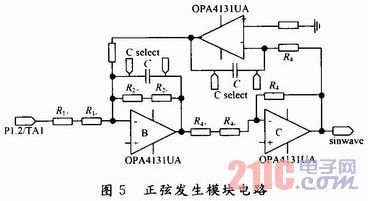

在圖1測量原理中,測量是工作在正弦信號的條件下,要保證測量的精度,測量頻率必須保證相當穩定。所以,利用晶體振蕩器振蕩頻率穩定性高的特點來獲得測量頻率將很好的保證我們測量的穩定性。同時利用單片機定時器分頻晶振產生的頻率,可以獲得頻率穩定性高的各種頻率。單片機的定時器輸出為方波信號,要獲得正弦信號,需要對方波信號進行濾波,將方波的中心頻率信號濾出并保證相當的信號強度,因此需要設計一款性能良好的濾波器。此外,設計的濾波器必須有較高的Q值以提高選頻特性。其電路原理如圖5所示。

圖中電路實質是雙二次帶通濾波器,它的特點是調整過程十分簡單,增益由改變R1調整,Q由改變R2調節,而改變R3則影響輸出頻率。單片機輸出方波信號從圖5中R1輸入后,經雙二次帶通濾波器濾波后輸出正弦信號。系統通過單片機控制的雙刀雙擲模擬開關CD4052選擇不同的電容C來實現測量頻率的自動切換。此外,為了減小溫度影響,電路中R1,R2,R3采用由正負溫度系數電阻按一定比例串聯的溫度補償設計。

3 系統軟件設計

系統軟件設計包括主程序、MCU與FPGA通信子程序、鍵盤子程序、液晶顯示子程序、數據處理子程序。

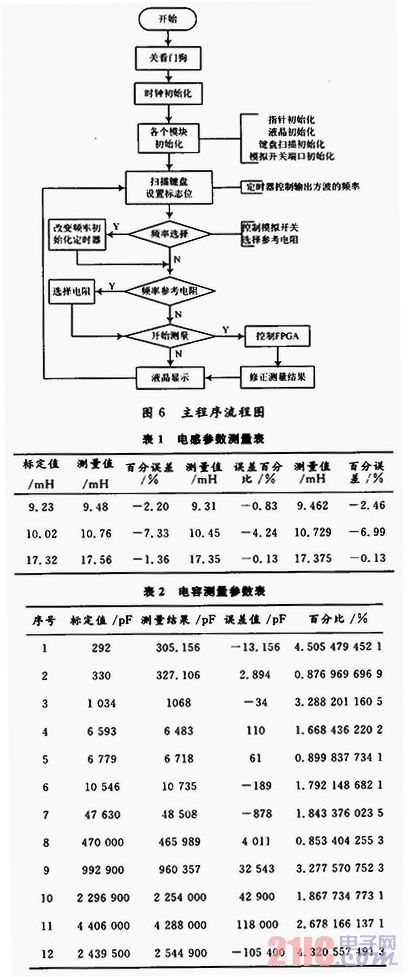

主程序設計流程為開始后先進性初始化,關閉看門狗以防止程序初始化時被復位,將系統時鐘初始化,接著是對各模塊(指針、液晶、鍵盤掃描、模擬開關端口)等子系統指針初始化,然后進入測量調整階段。測量調整階段先進行鍵盤掃描(鍵盤掃描主要用在調試階段最終不需要鍵盤輸入)設置標志位,設置定時器控制輸出方波頻率并根據鍵盤標志位判斷是否需要進行手動頻率切換,控制模擬開關自動選擇參考電阻,通知FPGA進行信號處理,并根據初步測量結果進行頻率和R0調整,對測量結果進行修正,最終控制液晶輸出測量結果。主程序設計流程圖如圖6所示。

4 結果及討論

測量值與數字電橋測量值對比如表1~表3。

設計的RLC測量儀的電阻測量范圍為50 Ω~20 MΩ,誤差在5%以內,電感測量范圍為1 mH~1 H,誤差在為8%以內,電容測量范圍為100 pF~50μF,誤差在5%以內。

設計采用了單片機智能控制技術,實現了系統的智能化控制和輸出。高速A/D采樣轉換技術,實現了信號的高速轉換以及數據的高速采集。基于FPGA的數字信號處理技術,實現了數據的高速處理計算。目前該裝置由于模擬開關內部電阻較大(約120 Ω)限制了部分范圍的RLC測量精度,需要改用導通電阻更小的模擬開關來完善。