隨著多媒體和通信技術的發展,視頻圖像處理的實時性成為人們關注的熱點。視頻圖像處理一般都是用數字信號處理器 (digital signal processor,DSP)來完成的。為了滿足實時性要求,往往采用多DSP或DSP陣列的方法,使系統在成本、重量、功耗等方面都會快速升高。現場可 編程門陣列(FPGA)運算的并行性和內嵌DSP核等特點,能夠提高運算速度滿足視頻處理的實時性要求。在視頻圖像顯示、處理時,采用的顏色空間主要有 RGB,YCrCb兩種。RGB基于三基色原理,顏色實現簡單,在計算機、電視機顯示系統中應用廣泛,YCrCb將顏色的亮度信號與色度信號分離,易于實 現壓縮,方便傳輸和處理。在視頻壓縮、傳輸等應用中經常需要實現RGB與YCbCr顏色空間的相互變換。這里推導出一種適合在FPGA上實現從RGB到 YCbCr。顏色空間變換的新算法,采用單片FPGA完成電路設計,利用FPGA內嵌DSP核實現乘法運算,提高了轉換算法的運行速度。

1 顏色空間

在RGB顏色空間中,自然界所有顏色都可以用紅(R)、綠(G)、藍(B)三種顏色的不同強度組合而重現。RGB的取值范圍分別為0~255,表1列出了幾種顏色對應的R,G,B取值。

RGB生成顏色容易實現,被廣泛應用在計算機、彩色電視機的顯示系統中。但是RGB表示顏色的效率并不是很高,3個顏色分量同等重要,而且亮度信息存在于所有顏色分量中,當需要對像素點的亮度或者色度值進行修改時,必須同時改變RGB三者的值。

YCrCb 顏色空間是在開發世界范圍數字分量食品標準過程中作為ITU-R BT.601標準的一部分而開發出來的。在YCRCb顏色空間中,Y表示亮度信號,取值范圍為16~235;Cr,Cb表示色度信號,取值范圍為 16~240,亮度信號與色度信號相互獨立。這種顏色表示方法可以利用人眼的特性降低數字彩色圖像的存儲空間。人眼視覺系統(HVS)對亮度細節的敏感度 高于顏色細節,適當減少色度分辨率不會明顯影響圖像的畫質,易于實現數據壓縮。

2 RGB到YCrCb的轉換

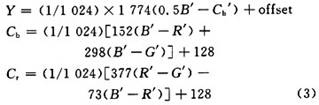

在ITU-R BT.601標準中給出了RGB與YCrCb的轉換關系式如下:

式中:R’,G’,B’表示Garoma校正后的R,G,B值。該轉換關系式是一個3×3乘法矩陣,電路實現時需要9個乘法器和9個加法器,在FPGA中直接實現時將會占用較多邏輯資源。

為了減少邏輯資源的使用,需要對該算法做進一步改進,簡化運算過程,從而以較少的邏輯資源實現轉換電路。首先對Cb,Cr做如下化簡:

Cb=0.148 2(B’-R’)+0.291 0(B’-G’)+128

Cr=0.367 8(R’-G’)-0.071 4(B’-R’)+128

對 y的計算公式進行化簡時,令Y’=0.256 8R’+0.501 4G’+0.097 9B’,Cb’ =-0.148 2R’-0.291 0G’+0.439 2B’,有0.577 2Y’+Cb’=0.495 7B’。為了計算方便,近似值為0.5B’。此時,有Y’=1.732 5(0.5B’-Cb’),與原式誤差為△Y’=0.007 4B’,其范圍為0~1.887。當以Y’表示Y時,需要對誤差作補償。計算公式可表示為:

Y=1.732 5(0.5B’-Cb’)+offset

式中:offset=16-0.007 4B’,化簡后的轉換公式如下:

Y=1.732 5(0.5B’-Cb’)+offset

Cb=0.148 2(B’-R’)+0.291 0(B’-G’)+128 (2)

Cr=0.367 8(R’-G’)-0.071 4(B’-R’)+128

式中:Cb’=0.148 2(B’-R’)+0.291 0(B’-G’),

offset=16-0.007 4B’。

根 據B’的取值不同,offset的取值取整后為14,15,16。在計算過程中,可以用一個數據選擇器根據B’值的不同選擇offset的值。0.5B’ 的計算可以用移位實現。化簡后的轉換算法,對Y,Cb,Cr的計算將比原來節省4個乘法器。在FPGA中,加法器、數據選擇器和移位算法的實現比乘法器簡 單,該化簡將利于減少邏輯資源的應用,簡化實現電路,提高運算速度。

轉換電路結構如圖1所示。

3 基于FPGA的實現

在FPGA中,對乘法的實現比較復雜,可以采用如下幾種方法:

(1)直接用編程語言描述乘法運算,由綜合工具自動實現,用該方法描述,實現簡單,但是耗用比較多的邏輯資源。

(2)利用查找表的方式實現乘法運算,事先把要相乘數據的所有結果算出來存到ROM中,根據輸入數據的值讀取相應的結果,當用該方法相乘數據位數比較多時,會占用大量的存儲空間。

(3)用FPGA中內嵌的乘法器實現,該方法實現簡單,當用VHDL語言實現時,調用相應的乘法模塊即可。

本文采用第三種方法,用專用乘法器來實現轉換公式中的乘法運算。Xilinx的Virtex 4系列FPGA芯片內嵌的乘法器為Xtreme DSPTM Slice-DSP48 Slice其工作頻率高達500 MHz,支持多種獨立的功能,包括乘法器、乘累加器(MAC)、后接加法器的乘法器、三輸入加法器、桶形移位寄存器、寬路線多路復用器、大小及比較器或寬 計數器。本文將運用DSP48 Slice模塊實現乘加運算,在電路結構圖的虛線框中,乘法和加法的運算將用單個DSP48 Slice模塊實現。這樣將會減少轉換關系式中加法器的數量,節約邏輯資源,在程序中可以用元件例化語句調用DSP48 Slice模塊,實現方法簡單,程序簡潔。為了滿足浮點數和運算精度的要求,適合在FPGA中實現,將式(2)改寫為:

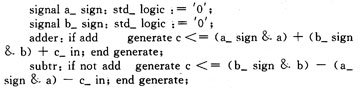

式 中的除法運算可以通過截斷低位數據的方法實現,在截斷數據時,對截去小數部分判斷,采用4舍5人的方法,當截去部分的最高位是1時,有進位,最高位是0 時,直接舍去。用VHDL語言描述式(3)的轉換算法,輸入R’,G’,B’是8位無符號二進制數,進行加減運算時,需要做符號位補位。

在每個運算部件(包括乘法和加減法器)的輸出以及系統的輸入/輸出之間加上緩存寄存器,實現流水線設計,能提高資源利用率,加快運算速度,寄存器級數由運算延時大小決定。在輸出端用計數器控制運算開始時的噪音輸出。箝位電路控制輸出數據范圍滿足顏色空間的要求。

4 仿真結果

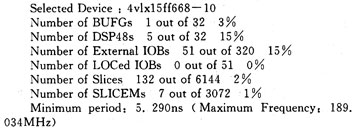

在Xilinx的Virtex4-FX平臺實現現圖1的電路結構,用ISE軟件仿真。資源使用情況如下:

時序仿真結果如圖2所示。

通過圖2可以驗證轉換算法的正確性。在使能信號en有效后,經過6個時鐘的運算時延,輸出端有轉換結果輸出,輸出結果四舍五入,誤差0.5,比以往算法提高了變換結果的精度。

5 結 語

通 過對轉換算法的研究,推導出適合在FPGA上實現的新算法,算法優點突出。算式中乘法器采用DSP48 Slice模塊實現,提高了轉換算法的運算速度。從綜合報告可以看出,除了使用5個DSP48s外,其他資源使用的比較少。運算速度最大能夠達到189 MHz,能夠充分滿足運算量大,實時性要求高的應用。

0 引 言