0 引言

1994年,Compaq、Intel、Microsoft、NEC等7家世界著名的計算機和通訊公司成立了USB論壇。1995年11月正式制訂了USB通用串行總線(universal serial Bus)規范。USBl.1主要應用在中低速外部設備上,它支持的傳輸速率有低速1.5 Mbps和全速12 Mbps。1999年初在Intel的開發者論壇大會上,介紹了USB2.0規范。最新的USB2.0支持3種速率:低速1.5 Mbps、全速12 Mbps和高速480 Mbps。這3種速率可以滿足目前大部分外設接口的需要。本文介紹了目前使用較多的USB2.0控制器CY7C68013與FPGA接口的VHDL實現。本系統可擴展,完全可用于其他高速數據采集、高速數據通信系統中,可以支持寬帶數字攝像設備及下一代掃描儀、打印機及存儲設備等。

1 CY7C68013簡介

CYPRESS半導體公司的EZ-USB FX2系列芯片是最早符合USB2.0協議的微控制器之一,以其良好的性能和獨特的設計在USB接口開發領域占有重要的地位。CY7C68013是EZ-USB FX2系列芯片中的一款高性能USB2.0微控制器,它提供了全面的USB2.0外圍設備解決方案。

CY7C68013將USB外圍接口設備所需的各種功能集成在一個單片電路上,通過集成的USB收發器連接到USB總線的D+和D一端;串行接口引擎(SIE)進行譯碼、編碼、錯誤糾正和位填充,變換USB所需的信號電平;最終,從USB接口SIE發送和接收數據。USB2.0控制器CY7C68013數據傳輸速率快,可支持移動硬盤、ATA、FPGA和DSL調制解調器等接口。CY7C68013主要具有如下特性:

(1)芯片內有480 Mb/s的收發器(PLL和智能SIE),包含全部USB2.O物理層(PHY);

(2)2、3、4倍增緩沖端點FIFO,以適應480 Mb/s的USB2.O傳輸速率;

(3)內部嵌入可運行在48 MHz頻率的增強型8051內核;

(4)4個接口FIFO:它們都可以由外部和內部來提供時鐘,端點FIFO與接口FIFO兩者相結合可以實現縮短USB和外部邏輯電路數據傳輸的時間;

(5)通用可編程接口(CPIF)作為一種編碼狀態設備,可實現時序管理,使得CY7C68013 FIFO達到無縫連接。CY7C68013集成了很多功能,設計時無需考慮外部物理層(PHY),從而大大降低了成本,并減少了芯片間高速信號布線的困難。

2 系統的設計實現

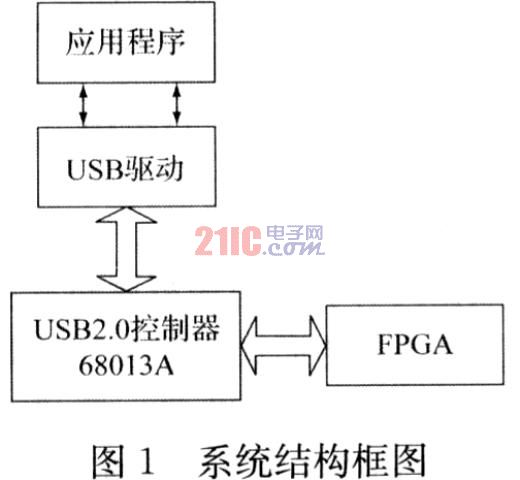

系統結構如圖l所示,本設計中,應用程序是用戶界面;USB驅動用于連接用戶和底層硬件;USB2.O控制器68013用于FPGA和PC間的數據交互。

2.1 硬件結構

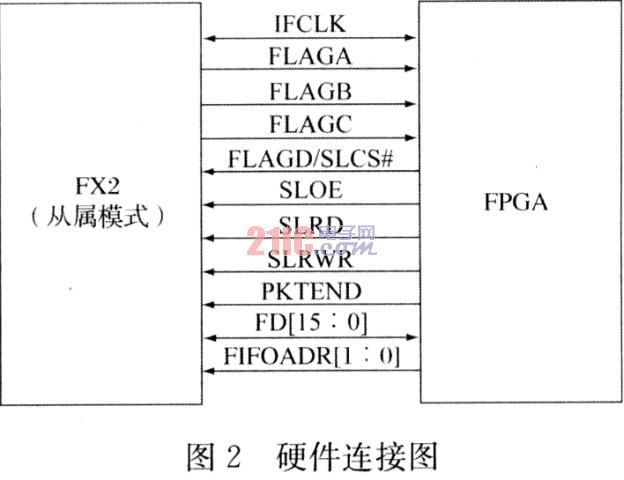

本系統硬件連接主要是由FPGA和USB2.0控制器,如圖2所示。同時也可以根據實際系統的需要,用FPGA實現預定功能,硬件接口模式有Slave FIFO和GPIF兩種接口模式。本方案采用Slave FIFO模式,當EZ-USB FX2工作于Slave FIFO時,外圍電路可像普通FIFO一樣對FX2中的端點2、端點4、端點6、端點8的數據緩沖區進行讀寫。圖2展示了這種模式下FX2和外圍電路的典型連接,其中,IFCLK為接口時鐘,可由芯片CY7C68013產生(30 MHz/40 MHz),也可由外部輸入(5MHz/48 MHz);FLAGA-FLAGD為FIFO標志管腳,用于映射FIFO的當前狀態;SLCS#為從屬FIFO的片選信號,低電平有效;FD[15∶O]為16位雙向數據總線;FIFOADDR[1∶O]用于選擇和FD連接的端點緩沖區;SLOE用于使能數據總線FD的輸出;SLRD和SLRWR可分別作為FIFO的讀寫選通信號;外圍電路可通過使能PKTEND管腳向USB發送一個IN數據包,而不用考慮該包的長度。

2.2 系統軟件

系統軟件設計主要包括3部分:VHDI代碼、USB固件程序(Firmware)以及應用程序。

2.2.1 VHDL程序設計

FPGA是通過Slave FIFO的方式和USB控制器CY7C68013相連的。FPGA讀取數據,通過查詢CY7C68013中FIFO的狀態來判斷是否可以進行讀數據,主要是查詢狀態標志位FLAGC。讀數據程序狀態轉移圖如圖3所示。

狀態1:在空閑時,接到命令,發起傳輸,使地址指向用于下傳數據的FIFO。進入狀態2;

狀態2:查詢讀狀態的FIFO標志FLAGC,如果為FIFO為空,則繼續等待,如果有數據則進入狀態3;

狀態3:使讀數據信號線有效,接收數據,接收完數據后進入狀態4;

狀態4:如果FIFO中還有數據需要接收,則進如狀態2,否則進入空閑狀態。

FPGA在上傳數據時,原理基本相同,方向相反,采用不同的FIFO和查詢狀態標志位。

2.2.2 固件編程

固件編程就是對USB設備的各類寄存器進行配置的過程。固件程序是指運行在設備CPU中的程序,只有在固件程序運行時,外設才稱之為具有給定功能的外部設備。固件要完成以下主要工作:

(1)初始化工作;

(2)對設備進行重新列舉(ReNumeration);

(3)響應中斷,并對中斷作相應的處理;

(4)數據的接收與發送;

(5)外圍電路的控制。

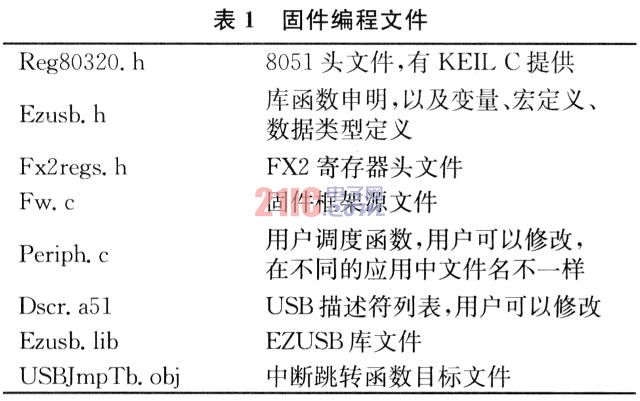

為了簡化固件編程,CYPRESS提供了開發固件庫和固件編程框架,只需在此基礎上添加少量代碼就可以完成固件編程。USB建立固件編程框架的文件見表1,在實際編程過程中,根據自定義,只需要修改Periph.c和Dscr.a51兩個文件。固件代碼固化到一片EEPROM中,設備加電后由FX2通過I2C總線自動加載到片內RAM后自動執行。設備功能、工作方式等均可以通過改寫固件程序,重新配置。

2.2.3 應用程序

應用程序是系統與用戶的接口,設備驅動程序提供應用程序訪問底層硬件的接口。驅動程序采用了CyPress公司的通用驅動程序ezusb.-sys,完全能夠滿足本系統設計的要求。在驅動程序被系統加載后,它的許多進程處于Idle狀態,需要應用程序去調用激活。應用程序利用Win32 API直接調用驅動程序,實現應用程序和驅動程序的信息交互。

應用程序實現了數據下載和數據上傳兩個功能,在Windows操作系統中,只需要通過調用幾條簡單的文件操作API函數,就可以實現與驅動程序中USB設備通信。 Win32應用程序調用WDM驅動程序的Win32 API函數有5個:CreateFile(創建設備)函數;CloseFile(關閉設備)函數;ReadFile(從設備讀取數據)函數;WriteFile(對設備寫入數據)函數;DeviceContronl(設備控制)函數。對于DeviceloControl()函數的調用,驅動程序根據I/O控制命令來決定該如何獲取應用程序的緩沖區地址。

本設計就采用DeviceloControl函數來進行應用程序和WDM設備驅動程序間的通信。以下是DevicelIoControl的聲明:

DeviceIoControl(

HANDLE hDevice;設備返回的句柄

DWORD dwIoControlCode;驅動程序的控制命令

LPVOID lpInBuffer;應用程序發給驅動程序的緩沖區地址

DWORD nInBufferSize;應用程序發給驅動程序的緩沖區大小

LPVOID lpOutBuffer;驅動發給應用程序的緩沖區地址

DWORD lpOutBuffer;驅動發給應用程序的緩沖區大小

LPDWORD lpBytesReturned;存放驅動程序實際返回字節數

LPOVERLAPPED lpOverlapped;同步時置為NULL)

3 測試結果

3.1 PC下傳數據

FPGA采用系統時鐘為50 M,為便于計算傳輸效率和傳輸可靠性,在應用程序中加載計時函數,下傳數據每次發送100M,發送數據為位寬8 b的循環遞增數列,結果顯示下傳數據最大速率為42.1 MB/s,在FPGA中用嵌入式邏輯分析儀查看接收的數據,如圖4所示。每個u_slrd讀脈沖,FPGA讀取一個16 b數據,由于發送時是按照8 b發送,接收數據是16 b,所以每次接收到的16位數據,是2個8位數的組合。從圖4中可以看出FPGA接收數據準確,無丟失數據的情況。

3.2 PC接收數據

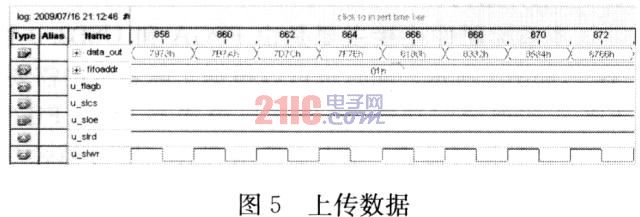

在接收數據時,同理,應用程序每次接收100 M,將讀取的數據以文件bin的形式存儲在應用程序工程目錄下,結果顯示bin文件中數據準確。測得最大傳輸結果為 38.4MB/s,利用FPGA嵌入式邏輯分析儀分析結果如圖5所示,每個u_slwr讀脈沖,FPGA發送一個16 b數據。

4 結束語

本系統通過FPGA控制USB2.O控制器CY7C68013達到高速數據傳輸的目的,具有硬件結構簡單、軟件擴展性強、傳輸數據準確性高等特點,目前下傳和上傳速度分別為42.1MB/s和38.4 MB/s,完全可以應用于高速數據采集、高速數據通信、數字攝像設備及存儲設備等。