文獻標識碼: A

文章編號: 0258-7998(2014)08-0014-03

在電路與信號系統數據傳輸領域,現場可編程門陣列FPGA與通用處理器進行數據通信時一般采用通用處理器外部異步總線接口來處理。采用這種接口方式的優點是接口實現簡單,易操作;缺點是數據傳輸速率低。

因此,當系統對數據傳輸速率要求較高時,這種傳統的FPGA與通用處理器之間的異步數據傳輸方式不能滿足應用的基本需求。

一般來說,通用處理器都包含有同步動態隨機存取存儲器SDRAM(Synchronous Dynamic Random Access Memory)控制器的用途是可以通過接口外部SDRAM存儲器[1]擴展外部存儲空間。SDRAM因為使用同步邏輯傳輸數據,因此具備很高的數據傳輸效率。

如果FPGA與通用處理器進行數據通信時基于SDRAM控制器接口,使用同步邏輯傳輸數據,數據傳輸速率將會較異步傳輸大大提高。采用這種接口方式的優點就是數據傳輸速率高,缺點是接口實現較復雜。

1 設計思路

為了能夠在FPGA與通用處理器之間實現同步數據傳輸,提高數據傳輸速率,要求通用處理器應當包含SDRAM控制器,FPGA與通用處理器之間的數據通信則基于SDRAM控制器接口進行。

在滿足上述條件的前提下,本文提出的一個設計思路是將FPGA模擬為通用處理器SDRAM控制器的一個外接SDRAM存儲器,進而通過SDRAM控制器實現通用處理器與FPGA之間的同步數據傳輸,以提高數據傳輸速率。

為了實現上述設計思路,需要在FPGA內部構建雙向的同步輸入輸出接口STI[2](Synchronous Transmission Interface)與外部通用處理器的SDRAM控制器接口,STI應該嚴格按照SDRAM控制器接口時序進行工作。

2 實現方法

因為通用處理器的SDRAM控制器專門用來擴展系統外部存儲空間,與外部SDRAM存儲器進行接口,因此,在FPGA內部構建的雙向同步輸入輸出接口(STI)必須嚴格按照SDRAM存儲器的工作原理來進行設計,通過STI將FPGA模擬為通用處理器SDRAM控制器的一個外接SDRAM存儲器。此STI接口一端與外部通用處理器的SDRAM控制器進行接口,另一端與FPGA內部的存儲模塊或數據處理單元接口。這樣,FPGA便可以與外部通用處理器實現同步數據傳輸,提高數據傳輸效率。

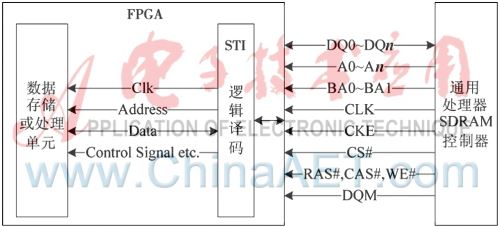

FPGA與通用處理器同步數據傳輸系統結構框圖如圖1所示

STI做為連接FPGA內部數據存儲或處理單元和外部SDRAM控制器的接口,其接口信號輸入端為完整的SDRAM信號輸入。接口信號輸出端為內部數據存儲或處理單元的數據、地址及控制等信號。

圖1中FPGA與通用處理器之間數據位寬為DQ0~DQn;尋址空間由地址信號A0~An及BANK信號BA0~BA1來決定;數據傳輸同步時鐘信號為CLK;時鐘使能信號為CKE;片選信號為CS#;命令譯碼信號為RAS#,CAS#,WE#;數據屏蔽信號為DQM。

FPGA內部的數據存儲或處理單元與STI通過時鐘信號Clk、地址信號Address、數據信號Data、控制信號等實現互聯。

STI的主要功能就是接收來自SDRAM控制器的同步信號,嚴格按照SDRAM工作時序對其進行邏輯譯碼轉換,翻譯成FPGA內部的數據存儲器或處理單元可以正確應用的信號形式,從而確保數據傳輸的準確無誤。

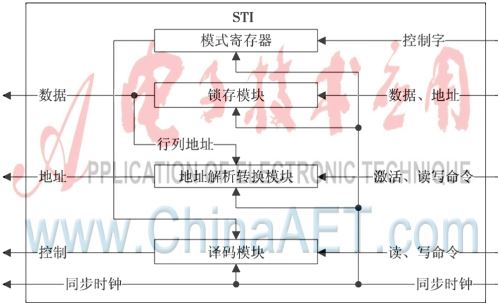

STI包含4個主要的功能模塊[3]:模式寄存器、鎖存模塊、地址解析轉換模塊、譯碼模塊。STI的功能結構框圖如圖2所示。

STI的功能結構框圖如圖2所示

各功能模塊實現的功能分別是:(1)模式寄存器,設定SDRAM控制器的數據突發傳輸長度和讀延時周期;(2)鎖存模塊,鎖存SDRAM控制器發送的數據和地址信號;(3)地址解析轉換模塊,根據SDRAM控制器的激活、讀寫等命令,將SDRAM控制器的行列地址進行解析,轉換成為FPGA內部數據存儲器或處理單元可以直接使用的地址信號;(4)譯碼模塊,結合模式寄存器的配置內容,根據SDRAM控制器的讀、寫命令,譯碼出與數據存儲器或處理單元接口的讀、寫、使能等控制信號。

譯碼模塊產生的讀、寫、使能等控制信號配合地址解析轉換模塊產生的直接尋址地址信號以及鎖存模塊產生的數據信號,結合同步時鐘信號,共同完成對STI后端數據存儲器或處理單元的接口工作。即實現了STI與FPGA內部數據存儲器或處理單元的數據實時寫入和讀取操作,從而完成了FPGA與通用處理器之間數據的實時同步傳輸。

綜上可以得到FPGA與通用處理器同步數據傳輸系統的工作流程如圖3所示。

圖3 FPGA與通用處理器同步數據傳輸工作流程圖

以上所述功能模塊及工作內容的代碼實現全部在FPGA內部完成。

3 實測驗證

將上述同步數據傳輸接口設計方法應用于基于數字信號處理器TS201[4-5]和EP2S180[6](FPGA)的通用信號處理電路板,已經取得很好的實用效果。經過實際測試,采用該方法后,數據傳輸正確無誤,數據傳輸速率是傳統異步接口傳輸速率的5倍以上。

實際測試中,以FPGA內部64 K×32 bit的數據存儲單元為例,DSP與FPGA分別進行異步數據傳輸測試和同步數據傳輸測試[7],傳輸一包數據的容量都為64 K×32 bit。通過FPGA開發環境QuartusII自帶的SignalTapII組件對數據傳輸過程中相關的信號進行實時測試采樣。通過測試得到,采用傳統異步接口數據傳輸時序圖如圖4所示,采用本文所述同步接口數據傳輸時序圖如圖5所示。

從圖4和圖5的時序圖可以很直觀地看出,FPGA與通用處理器之間采用同步數據傳輸較傳統異步數據傳輸有明顯優勢。

本文針對FPGA與通用處理器之間的通信方式,提出了一種通過在FPGA內部構建一個雙向同步輸入/輸出接口(STI)來實現FPGA與通用處理器之間同步數據傳輸的方法,并詳細介紹了該方法的設計思路及實現方法。

本文提供的設計方法具有很高的實用價值,在不增加系統硬件成本的前提下,有效地利用現有資源,將傳統的異步總線接口改進為同步總線接口,提高了數據傳輸的速率,進而極大地提升了系統的工作效率。

最后,給出本文設計方法的應用實例,通過在實際通用信號處理樣機上的測試,驗證了該方法的實用性和有效性。

參考文獻

[1] MICRON.256Mb:x4,x8,x16 SDRAM Features[EB/OL].

(2012-11-08)[2014-04-01].http://www.micron.com/prod-

ucts/dram/sdram#fullPart&236=2.

[2] 夏宇聞.Verilog數字系統設計教程(第2版)[M].北京:

北京航空航天大學出版社,2008.

[3] 袁俊泉,孫敏琪,曹瑞.Verilog HDL數字系統設計及其應

用[M].西安:西安電子科技大學出版社,2002.

[4] Analog Devices.ADSP-TS201 TigerSHARC?誖embedded

processor,Rev.C[EB/OL].(2012-11-08)[2014-04-01].

http://www.analog.com/en/processors-dsp/tigersharc/adsp-

ts201s/products/product.html.

[5] Analog Devices.ADSP-TS201 TigerSHARC?誖processor

hardware reference,Revision 1.1[EB/OL].(2012-11-08)

[2014-04-01].http://www.analog.com/en/

processors-dsp/tigersharc/adsp-ts201s/products/product.html.

[6] Altera.Stratix?誖II device handbook,Volume 1 and Vol-

ume 2[EB/OL].(2012-11-08)[2014-04-01].http://www.

altera.com.cn/literature/lit-stx2.jsp.

[7] Analog Devices.ADSP-TS201 TigerSHARC?誖processor

programming reference,Revision 1.1[EB/OL].(2012-11-08)

[2014-04-01].http://www.analog.com/en/

processors-dsp/tigersharc/adsp-ts201s/products/product.html.

(收稿日期:2014-04-09)

作者簡介:

胡強,男,1978年生,工程師,主要研究方向:電子與信息系統硬件研發。

圖4 采用異步接口數據傳輸時序圖

圖5 采用同步接口數據傳輸時序圖