在特權的上篇博文《基于FPGA的跨時鐘域信號處理——專用握手信號》中提出了使用專門的握手信號達到異步時鐘域數據的可靠傳輸。列舉了一個簡單的由請求信號req、數據信號data、應答信號ack組成的簡單握手機制。riple兄更是提出了req和ack這兩個直接的跨時鐘域信號在被另一個時鐘域的寄存器同步時的亞穩態問題。這個問題估計是整個異步通信中最值得探討和關注的。

很幸運,特權同學找到了很官方的說法——《Application Note42:Metastability in Altera Devices》,一口氣讀完全文,有一個單詞送給這篇文章很合適——“nice”。特權同學過去的所有疑惑都在文章中找到了答案,盡管altera在文章的最后只是竭盡全力的在吹捧自己的好。

如果你E文還不錯(該不會比我這個4次都沒過掉4級考試的家伙差吧,~_~),那么去享受原文吧。或者你可以考慮看看特權同學的翻譯水平,哈哈……

什么是亞穩態?

所有數字器件(例如FPGA)的信號傳輸都會有一定的時序要求,從而保證每個寄存器將捕獲的輸入信號正確輸出。為了確保可靠的操作,輸入寄存器的信號必須在時鐘沿的某段時間(寄存器的建立時間Tsu)之前保持穩定,并且持續到時鐘沿之后的某段時間(寄存器的保持時間Th)之后才能改變。而該寄存器的輸入反映到輸出則需要經過一定的延時(時鐘到輸出的時間Tco)。如果數據信號的變化違反了Tsu后者Th的要求,那么寄存器的輸出就會處于亞穩態。此時,寄存器的輸出會在高電平1和低電平0之間盤旋一段時間,這也意味著寄存器的輸出達到一個穩定的高或者低電平的狀態所需要的時間會大于Tco。

在同步系統中,輸入信號總是能夠達到寄存器的時序要求,所以亞穩態不會發生。亞穩態問題通常發生在一些跨時鐘域信號的傳輸上。由于數據信號可能在任何時間到達異步時鐘域的目的寄存器,所以設計者無法保證滿足Tsu和Th的要求。然而,并非所有違反寄存器的Tsu或Th要求的信號會導致輸出亞穩態。某個寄存器進入了亞穩態后重新回到穩定狀態的時間取決于器件的制造工藝及工作環境。在大多數情況下,寄存器將會快速的返回穩定狀態。

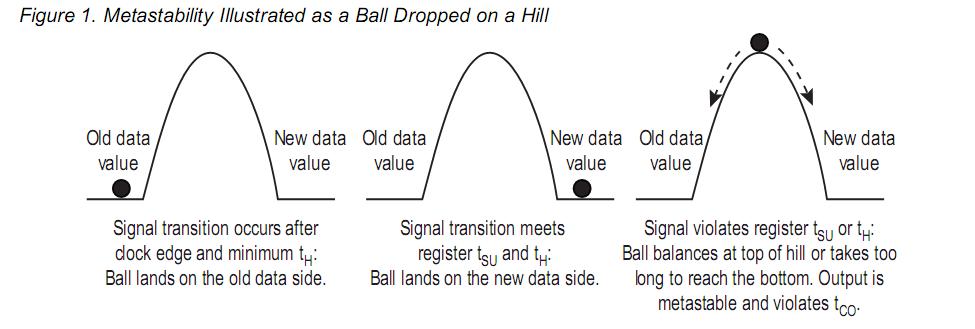

寄存器在時鐘沿采樣數據信號好比一個球從小山的一側拋到另一側。如圖1所示,小山的兩側代表數據的穩定狀態——舊的數據值或者新的數據值;山頂代表亞穩態。如果球被拋到山頂上,它可能會停在山頂上,但實際上它只要稍微有些動靜就會滾落到山底。在一定時間內,球滾的越遠,它達到穩定狀態的時間也就越短。

如果數據信號的變化發生在時鐘沿的某段時間之后(Th),就好像球跌落到了小山的“old data value”一側,輸出信號仍然保持時鐘變化前的值不變。如果數據信號的變化發生在時鐘沿的某段時間(Tsu)之前,并且持續到時鐘沿之后的某段時間(Th)都不再變化,那就好像球跌落到了小山的“new data value”一側,輸出數據達到穩定狀態的時間為Tco。然而,當一個寄存器的輸入數據違反了Tsu或者Th,就像球被拋到了山頂。如果球在山頂停留的越久,那么它到達山底的時間也就越長,這就相應的延長了從時鐘變化到輸出數據達到穩定狀態的時間(Tco)。

圖1

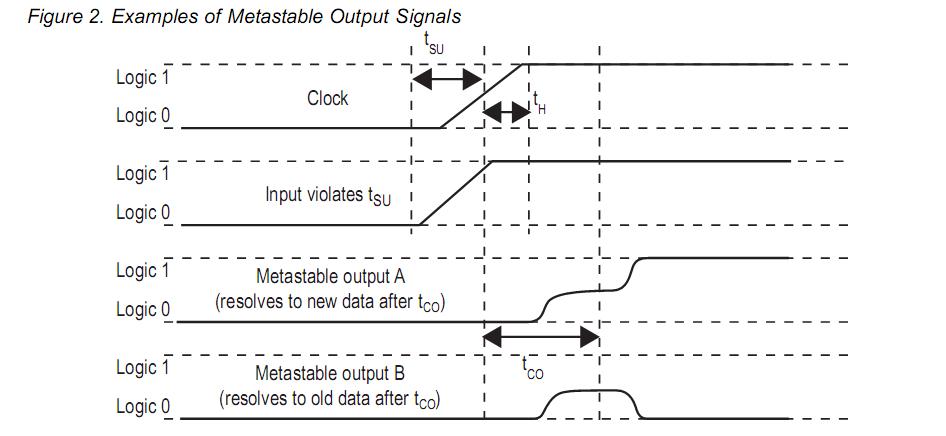

圖2很好的闡釋了亞穩態信號。在時鐘變化的同時,寄存器的輸入數據信號也處于從低電平到高電平的變化狀態,這就違反了寄存器的Tsu要求。圖中的輸出信號從低電平變化到亞穩態,即盤旋于高低電平之間的一個狀態。信號輸出A最終達到輸入信號的新狀態值1,信號輸出B卻返回了輸入信號的舊狀態值0。在這兩種情況下,信號輸出變化穩定在固定的1或者0狀態的時間遠超過了寄存器的固有Tco。

圖2

如果輸出信號在下一個寄存器捕獲數據前(下一個時鐘鎖存沿的Tsu時間前)處于一個穩定的有效狀態,那么亞穩態信號不會對該系統照成影響。但是如果亞穩態信號在下一個寄存器捕獲數據時仍然盤旋于高或者低電平之間,那將會對系統的后續電路產生影響。繼續討論球和小山的比喻,當球到達山底的時間(處于穩定的邏輯值0或1)超過了扣除寄存器Tco以外的余量時間,那么問題就隨著而來。

同步寄存器

當信號變化處于一個不相關的電路或者以不時鐘域,它在被使用前就需要先被同步到新的時鐘域中。新的時鐘域中的第一個寄存器將扮演同步寄存器的角色。

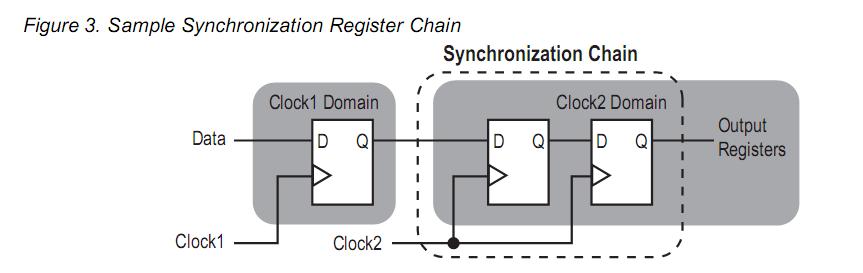

為了盡可能減少異步信號傳輸中由于亞穩態引發的問題,設計者通常在目的時鐘域中使用一串連續的寄存器(同步寄存器鏈或者同步裝置)將信號同步到新的時鐘域中。這些寄存器有額外的時間用于信號在被使用前從亞穩態達到穩定值。同步寄存器到寄存器路徑的時序余量,也就是亞穩態信號達到穩定的最大時間,也被認為是亞穩態持續時間。

同步寄存器鏈,或者同步裝置,被定義為一串達到以下要求的連續寄存器:

■ 鏈中的寄存器都由相同的時鐘或者相位相關的時鐘觸發;

■ 鏈中的第一個寄存器由不相關時鐘域或者是異步的時鐘來觸發;

■ 每個寄存器的扇出值都為1,鏈中的最后一個寄存器可以例外。

同步寄存器鏈的長度就是達到以上要求的同步時鐘域的寄存器數量,圖3是一個兩級的同步寄存器鏈,

圖3

傳輸在不相關時鐘域的信號,都有可能在相對于捕獲寄存器時鐘沿的任何時間點變化。因此,設計者無法預測信號變化的順序或者說信號兩次變化間經過了幾個鎖存時鐘周期。例如,一條異步總線的各個數據信號可能在不同的時鐘沿變化,結果接收到的數據值可能是錯誤的。

設計者必須考慮到電路的這些情況,而使用雙時鐘FIFO(DCFIFO)傳輸信號或者使用握手信號進行控制。FIFO使用同步裝置處理來自不同時鐘域的控制信號,數據的讀寫使用兩套獨立的總線。此外,如果異步信號作為兩個時鐘域的握手邏輯,這些控制信號就需要用于指示何時數據信號可以被接收時鐘域鎖存。如此一來,就可以利用同步寄存器確保亞穩態不會影響控制信號的傳輸,從而保證數據在使用前有充足的時間等待亞穩態達到穩定。

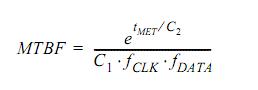

文章其實還沒有結束,只不過altera在后面很官方的提出了所謂的MTBF(mean time between failures)的概念,即所謂的平均無故障時間的概念。列了個公式,分析了各個參數,當然也不忘提他們的器件參數對于這個MTBF做了多大的貢獻。然后也提出了它們是如何進行該公式參數的推導。

我們還是回到主題,在明確了這些基本的概念和基本的方法后,就要學以致用。在上篇博文沒有解決的一個關鍵問題在于如何最有效的進行握手信號req、ack的采樣。這個問題我們可以先以altera提出的MTBF推導公式的各個參數入手分析。

在這個公式中,Tmet就是指寄存器從時鐘上升沿觸發后的時序余量時間,Fclk是接收時鐘域的時鐘頻率,Fdata是數據的變化頻率,而C1、C2則是與器件有關的參數,對于用戶是一個固定值。由此看來,設計者只能通過改變Tmet、Fclk、Fdata來提高MTBF值。MTBF值越大,說明出現亞穩態的幾率越小。要增大MTBF值,可以延長Tmet、也可以降低Fclk和Fdata這兩個頻率。

首先我們看看如何延長Tmet時間。

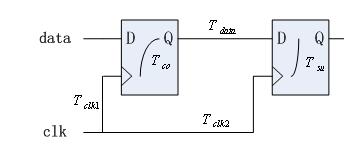

Tmet時間 = 采樣時鐘周期時間 – 輸出信號正常的Tco時間 - 數據到達下一級寄存器的輸入端口的其它延時時間Tdata - 下一級寄存器Tsu時間。

圖4

從嚴格意義上來說,Tmet時間還應該加上時鐘網絡延時時間(Tclk2-Tclk1)。總之,這個Tmet時間是指正常沒有亞穩態情況下,寄存器輸出信號從源寄存器到目的寄存器的建立時間余量。由于決定Tmet取值的參數中Tco和Tsu都是由FPGA器件本身的工藝以及工作環境決定的,設置時鐘網絡延時參數也很大程度上由器件決定,所以,如果在時鐘頻率Fclk和數據變化率Fdata固定的情況下,要增大Tmet值,那么設計者要做的只能是減小Tdata值。而這個Tdata是指兩個寄存器間的邏輯延時以及走線延時之和,要最大程度的減小它,估計也只能是不在連個寄存器間添加任何邏輯而已,正如我們的實例中也只有簡單的input=output。

再看Fclk,它是接收域的采樣時鐘,就是異步信號需要被同步到的那個時鐘域,它的頻率是越小越好。當然了,事物都其兩面性,這個頻率小到影響系統正常工作可就不行了。設計者需要從各個方面考慮來決定這個頻率,不會僅僅為了降低亞穩態發生的概率而無限制的降低系統的時鐘頻率。如此分析,發現這個Fclk基本也是一個比較固定的值,不是可以隨便說降就降的。降低Fclk其實也就是在增大Tmet時間,因為它是Tmet公式計算中的被減數,哈哈,好像是一環扣一環。另外,在不降低采樣頻率Fclk的情況下,通過使用使能信號的方式得到一個二分頻時鐘去采樣信號也可以達到降頻的目的,只不過這樣會多耗費幾個時鐘周期用于同步,但是有時也能夠明顯改善性能。

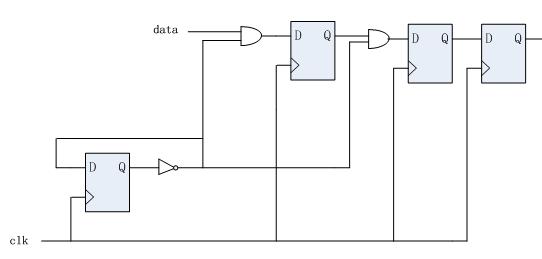

特權同學的二分頻采樣思路如圖5所示,前兩級采樣電路都做了2分頻,然后第三級使用原來時鐘進行采樣。它的好處在于給第一級和第二級同步寄存器更多的Tmet時間,將亞穩態抑制在第二級寄存器輸入之前,從而保證第三級寄存器的可靠采樣。雖然它在一、二級寄存器的輸入端增加了一些邏輯,可能會增大Tdata,但是相比于這個采樣時鐘的一半將額,它的變化是可以忽略不計的。

圖5

另一種辦法是在不降低每級寄存器的采樣頻率的情況下采用更多的同步寄存器,盡量去使用后級的寄存器,這也是一個笨辦法。Altera的筆記里打了一個比喻,如果一個設計你使用了9級的同步寄存器,那么MTBF是100年,而當你使用了10級的同步寄存器,那么MTBF是1000年。這個辦法其實有點類似冗余,這是所有人都知道的可以提高可靠性的原始辦法。這種思路的弊端和前面提到的方法一樣,需要付出多個時鐘周期為代價。

最后看這個Fdata,這個是發送時鐘域的數據變化率,似乎也是由系統決定的,設計者也無法做太多改變。

其實對于一般的應用,如果系統的時鐘頻率不太高,器件的特性還算可以(只是一些泛泛的說法,具體問題要具體分析),特權同學覺得上篇博文提出的握手信號同步方法就足以應付亞穩態問題。如果到高頻范疇來討論亞穩態,那將會是一項更有挑戰性的任務,只可惜特權同學目前接觸的最高頻也只不過100MHz而已。特權同學自覺才疏學淺,班門弄斧了。

無獨有偶,特權同學這篇博文即將收官之際,無意中看到船長的博客中《理解FPGAs中的亞穩態》一文也涉及到了altera的這篇筆記,也做了一下翻譯,似乎比特權同學翻譯的好。不過在此做個聲明,特權同學的博文一貫堅持原創,即便參考其它資料,也大都有所提及,并且有自己的評論和思考,這應該是每位電子工程師應該有的嚴謹和認真的態度。