文獻標識碼: A

文章編號: 0258-7998(2014)08-0038-03

隨著半導體工藝技術的不斷革新,功耗、存儲、頻率等技術瓶頸問題越來越突出,單核處理器已經很難繼續通過提高時鐘頻率的方式來提高自身的性能。單核處理器在提高主頻的同時也帶來了功耗和發熱量的問題。在這樣的背景下多核并行處理器應運而生并且得到了快速發展。在這個過程中,設計的復雜度和核間通信的線延遲[1]成為了當前多核并行處理器設計的核心問題。多核并行處理器的各個核獨立執行各自的程序,但各個核之間需要進行數據傳遞,路由器作為片上通信結構的核心部件,其設計性能直接影響整個片上網絡的處理效率。本文基于多態并行處理器功耗和結構復雜度要求設計了近鄰通信和遠程通信兩種通信機制,并對所設計的路由器進行了功能仿真和FPGA綜合。

1 多態并行處理機結構

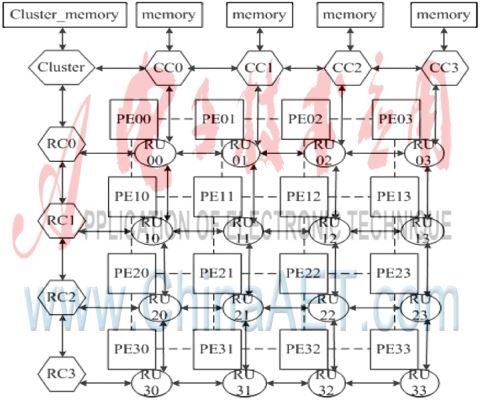

本文提出的多態并行處理器的處理單元具有單指令多數據(SIMD)和多指令多數據(MIMD)兩種運行模式[2-3]。該結構兼有硬件的多線程管理和高效的數據通信機制。多態并行處理機結構如圖1所示。

圖1 多態并行處理機結構框圖

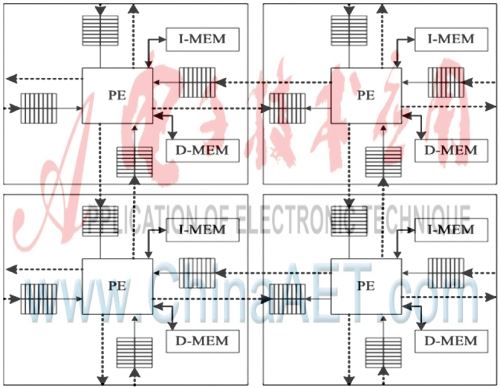

每個處理器核[4]由算術邏輯運算器ALU、線程管理器控制器TM、路由器RU(Router Unit)、鄰接共享存儲(Mn、Ms、Mw、Me)、數據存儲D-men(Data Memory)和指令存儲I-men(Instruction Memory)組成,每個基本處理單元如圖2所示。

圖2 基本處理器單元結構

2 設計與實現

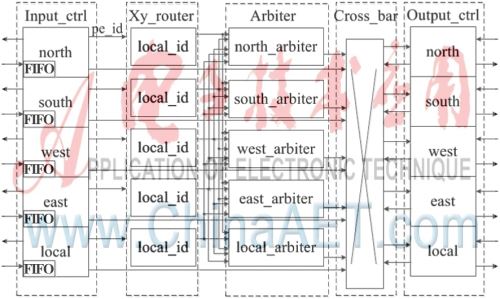

路由器的整體結構如圖3所示。路由器可連接東、西、南、北4個方向的路由器和本地PE。

圖3 路由器整體結構框圖

(1)Input_ctrl模塊:分別接收來自北、南、西、東、本地5個方向的數據請求,該模塊將5個方向的數據打包成固定的格式存儲在FIFO中。

(2)Xy_router模塊:該模塊采用XY路由算法實現,根據目標號和本地號判斷數據包的傳輸方向。

(3)Arbiter模塊:該模塊采用簡單的先來先到仲裁和設定固定優先級的仲裁機制實現。

(4)Cross_bar模塊:通過選擇完成數據和輸出的交叉對應,并根據輸出響應情況發送讀數據包使能信號。

(5)Output_ctrl模塊:該模塊完成東、西、南、北4個方向的輸出控制,以及本地輸出的數據包解包功能。

多態并行處理器的數據通信機制包括近鄰通信和遠程通信。

(1)近鄰通信機制

近鄰通信機制采用共享存儲的設計思想,每個處理單元(PE)都有北、南、西、東4個方向的共享存儲,每個方向有兩組存儲,每組存儲容量為8個字。近鄰通信機制結構框圖如圖4所示。

圖4 近鄰通信機制結構框圖

(2)遠程通信機制

遠程通信機制的結構如圖5所示。遠程通信完成遠程數據傳遞和函數調用兩種功能,遠程數據傳遞包括PE之間點對點傳送、PE與列控制器之間的數據傳遞兩種方式;遠程函數調用包括PE之間的遠程函數調用、PE與行(簇)控制器之間的遠程函數調用兩種方式。

圖5 遠程通信機制結構框圖

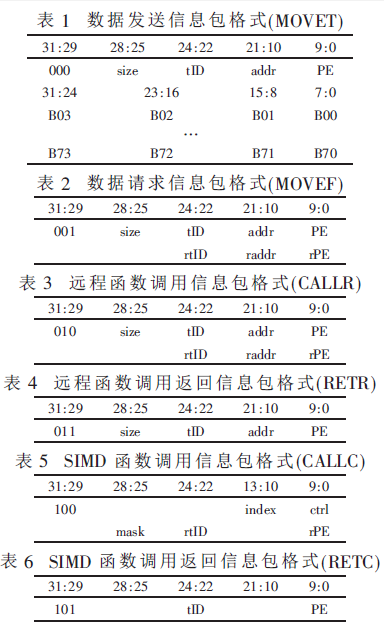

路由器處理的遠程數據傳輸請求包括:

①遠程處理器發送數據,來自遠程處理器的MOVET信息包;

②遠程處理器請求發送數據,來自遠程處理器的MOVEF信息包;

③列控制器發送數據請求,來自列控制器MVT信息包;

④遠程處理器發送多播請求,來自遠程處理器MVT信息包。

路由器處理的遠程函數調用請求包括:

①遠程處理器發送函數調用請求,來自遠程處理器CALLR信息包;

②遠程處理器返回函數調用,來自遠程處理器RETR信息包;

③行控制器和簇控制器返回函數調用,來自行控制器RETC信息包。

路由器相關數據包格式如表1~表6所示。

3 仿真驗證及結果分析

為了測試路由器數據通信機制,采用System Verilog搭建包含行控制器RC、列控制器CC、簇控制器CLC、處理單元PE、線程管理器TM、路由器RU的整體仿真平臺,使用ModelSim SE 10.1c進行仿真驗證。

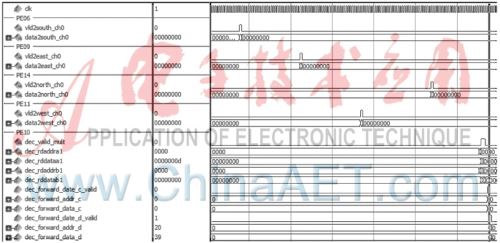

(1)近鄰通信測試方案:選用PE10作為本地,PE06、PE09、PE14、PE11作為鄰接,測試近鄰通信的數據通路,測試結果如圖6所示。

圖6 近鄰通信仿真時序圖

從圖6可以看出,PE06的vld2south_ch0有效,PE09的vld2west_ch0有效,PE14的vld2north_ch0有效,PE11的vld2east_ch0有效,表明與PE10相鄰的4個PE分別送了一個數據給PE10進行運算,PE10執行乘法運算,相乘的結果39和609分別寫回至地址20和22,近鄰通信的功能正確。

(2)遠程通信測試方案:選用PE00作為本地,測試調用遠程PE10函數執行的數據通路,測試結果如圖7所示。

圖7 遠程通信仿真時序圖

從圖7可以看出,本地PE00發出CALLR遠程函數調用數據包請求給PE10,當PE10執行完后返回給本地PE00一個RETR數據包。圖中只給出了CALLR數據包通路,CALLR/RETR數據通路正常。

綜上所述,路由器的近鄰通信和遠程通信的數據通路是正確的,達到了預期的功能要求。

4 路由器性能分析

在Xilinx ISE14.4中選用型號為Virtex7 XC7V2000T-

fht1761-2的芯片對路由器進行綜合。FPGA綜合結果表明,本文設計的5路32 bit數據寬度的路由器綜合頻率為314.287 MHz,高于參考文獻[5]中提出的5路16 bit數據寬度的路由器頻率128.8 MHz和參考文獻[6]提出的4路16 bit數據寬度的路由器頻率309.02 MHz。綜合報告如下:

Timing Summary:

Speed Grade: -2

Minimum period:3.182ns(Maximum Frequency: 314.287 MHz)

Minimum input arrival time before clock: 2.409 ns

Maximum output required time after clock: 1.126 ns

Maximum combinational path delay: 0.816 ns

圖8所示給出了路由器在FPGA上的具體資源消耗狀況以及資源利用率。綜上所述,本文所設計的路由器具有速度和面積上的優勢。

圖8 FPGA資源利用率

本文提出了一種適用于多態并行處理機的數據通信和路由器結構的設計,完成了ModelSim軟件功能仿真、Xilinx ISE14.4的綜合,并在Virtex7 XC7V2000Tfht1761-2開發板中實現了驗證。該設計結合并行處理機的需求設計了近鄰通信和遠程通信兩種通信機制,提高了整個并行處理機的性能和資源利用率。

參考文獻

[1] GRATZ P,SANKARALINGAM K,HANSON H,et al.Imple- mentation and evaluation of adynamically routed processor operand network[J].Proceedings of First International Sym posium on Networks-on-chip,IEEE Computer Society,2007,23(10):7-17.

[2] 李濤,肖靈芝.面向圖形和圖像處理的輕核陣列機結構[J].西安郵電學院學報,2012,17(3):43-46.

[3] 蒲林.多態并行處理器中的SIMD控制器設計與實現[J]. 電子技術應用,2013,33(11):53-59.

[4] 李濤,楊婷,易學淵.螢火蟲2:一種多態并行機的硬件體系結構[J].計算機工程與科學,2014(2):191-200.

[5] 周東紅.基于3x3NoC的路由器設計與網絡性能分析[D].西安:西安電子科技大學,2011.

[6] 林世俊,張凡,金德鵬.分布式同步的GALS片上網絡及 其接口設計[J].清華大學學報,2008,48(1):32-38.

(收稿日期:2014-05-10)

作者簡介:

海虎,男,1988年生,碩士,主要研究方向:專用集成電路設計與系統集成。

李濤,男,1954年生,博士,教授,主要研究方向:計算機體系結構、計算機圖形學。

楊婷,女,1989年生,碩士,主要研究方向:計算機系統結構與VLSI。