文獻標識碼: A

文章編號: 0258-7998(2015)03-0044-04

0 引言

由于基于ΣΔ調制技術的ΣΔ模數轉換器(ADC)易于與數字芯片集成,并且對于器件的失配不是很敏感,所以是目前高性能無線通信和傳感器微弱信號檢測電路的首選[1]。采用過采樣技術和噪聲整形技術的調制器是限制ΣΔ ADC性能的關鍵模塊,所以設計高性能的ΣΔ調制器是實現高精度的ΣΔ ADC的必經途徑。目前關于ΣΔ調制器的研究主要集中于兩階~四階結構,這是由于高階的調制器面臨穩定性問題。在設計低階的調制器時可以通過提高過采樣率來部分提高性能[2-3]。然而提高系統過采樣率會提高對運放帶寬的要求,增加系統的功耗。在消費電子領域,對于芯片的功耗有一定的限制,所以在較低的功耗下設計一種高性能的調制器很有意義。本文的目標是在較低的功耗下設計出一種適用于加速度傳感器的高性能ΣΔ調制器電路。通過參數優化和建模仿真,在較低的采樣頻率下實現一種五階單環一位結構的ΣΔ調制器電路。利用根軌跡法分析和驗證該高階系統的穩定性,通過版圖后仿真結果顯示提出的五階結構實現了較高的性能,滿足系統設計要求。

1 系統設計

圖1是設計的五階ΣΔ調制器原理框圖,該調制器采用前饋單環一位結構,該結構能夠減小積分器的輸出擺幅,降低對運放的性能和設計指標要求,提高了系統的線性度。同時采用前饋結構使得積分器輸出擺幅大大減小,能夠降低系統的功耗,有利于低功耗的設計目標。表1是經過優化的調制器的各級系數,包括前饋系數和各個積分器的增益因子。

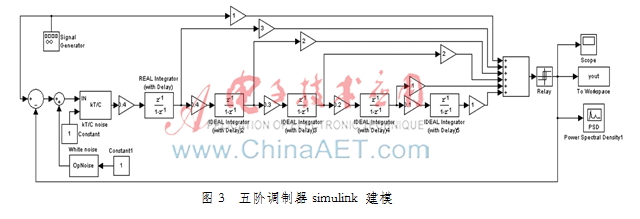

雖然提高階數能夠提高系統的性能,但是高階系統存在嚴重的穩定性問題。為了驗證系統的穩定性,可以在MATLAB中求解噪聲傳遞函數的根軌跡曲線來判斷系統的穩定性,結果如圖2所示。仿真結果顯示該高階系統是條件穩定的,當量化器的增益小于0.525時,極點進入單位圓外,系統出現穩定性問題,所以量化器的輸入存在一個穩定范圍,也即調制器的輸入信號不能太大,否則會導致系統不穩定。在MATLAB中搭建該五階調制器的行為級模型,如圖3所示。其中包含運放熱噪聲和第一級積分器的kT/C噪聲模型,而且在第一級積分器模型中引入了有限增益帶寬等非理想因素,以便更真實地模擬實際調制器電路的仿真結果。由于加速度計傳感器的應用頻帶較低,一般在幾百赫茲以內,所以在過采樣率為125的情況下,圖3中的調制器的采樣頻率可以大大降低。在輸入信號幅度為-1.94 dBFS,信號頻率488.24 Hz,采樣頻率為250 kHz的條件下,圖3中的65 536點輸出位流頻譜如圖4所示,實現了大于18位的精度,滿足了加速度計接口電路中關于后級高精調制器的帶寬和精度要求。

2 電路實現和版圖后仿

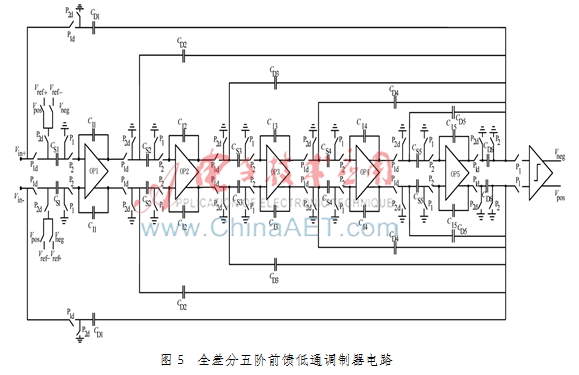

本設計的五階低通ΣΔ調制器電路采用開關電容電路實現,如圖5所示。在設計時采用全差分結構來消除電路的偶次諧波分量,從而提高整體電路的性能。整體電路由五級積分器電路、前饋求和電路以及動態鎖存比較器等組成,并由控制時序P1、P1d、P2、P2d控制開關的開啟和關斷。其中P1d和P2d分別是P1、P2的延遲時序,這樣設計的目的是減小開關關斷時的電荷注入引起的噪聲[4]。由于采用了高階調制結構,后級積分器的噪聲可以經過前級整形,所以第一級積分器決定著整體的性能,后級積分器的帶寬和增益等參數可以適當降低[5]。前饋求和電路采用簡單的無源開關電容電路,減小芯片面積和功耗。求和電路在P1相求和,比較器對輸入差分信號比較輸出;求和電路在P2相復位,比較器輸出鎖存。本設計的量化范圍Vpp=1.65 V,分辨率為N=18,OSR=125。根據建模仿真結果選取CS1=4 pF,第一級積分器的運放積分電容為10 pF。由于后級電路的噪聲可以通過前級抑制,后級積分器電路的采樣電容可以大大減小,故積分器的負載電容也等比例減小。

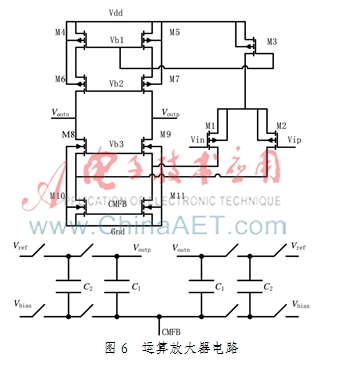

運放的有限增益會改變積分器的極點位置,產生積分泄露,也就改變了系統的噪聲傳遞函數的極點。通過行為級仿真掃描可以確定運放的直流增益需大于60 dB才能保證系統的精度。為了簡化設計,選擇一級折疊共源共柵放大器來實現積分器電路,運放的電路圖如圖6所示。在第一級積分器負載電容為10 pF時,仿真得到的運放電路直流增益為78 dB,單位增益帶寬約為12 MHz,相位裕度為66°,擺率為15.7 V/μs,功耗約為1.4 mW。后級積分器的負載電容等比例縮放,對運放的增益和帶寬要求也大大降低,因此可以降低功耗。后級4個運放在負載電容等比例縮小的情況下總體功耗小于1.5 mW。由于采用了一位量化,所以用比較器來實現調制器電容中的一位量化器,實現輸出數字信號。動態比較器具有電路簡單、速度較快、功耗低的特點。

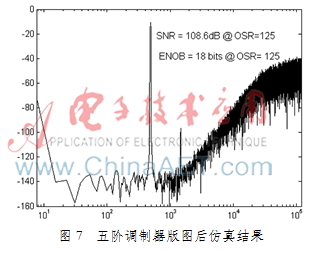

設計的五階低通ΣΔ調制器電路采用CHRT 0.35 μm CMOS工藝實現,系統工作在3.3 V的電源電壓下。通過提取出版圖寄生參數,在Spectre下進行后仿驗證,輸入信號幅度為500 mV的差分正弦信號,信號頻率488.28 Hz,系統的采樣頻率為250 kHz。將瞬態仿真的位流導出到MATLAB下進行頻率分析,65 536點的FFT結果如圖7所示。系統的信噪比達到108.6 dB,有效位數約為18位,總體功耗3.4 mW。由于開關和運放的非線性以及版圖的對稱性問題導致圖7中出現了3次諧波失真。

3 結束語

本文在CHRT 0.35 μm CMOS工藝下實現了一種用于加速度計信號檢測的高精度ΣΔ調制器。后仿真結果表明在1 kHz的信號帶寬內,實現了約18位的有效位數,整體功耗只有3.4 mW。通過后仿真結果和行為級建模的結果對比可以證明設計的五階單環調制器電路實現了設計目標,達到了性能要求。

參考文獻

[1] 范軍,黑勇,陳鋮穎.一種采用斬波——穩零技術的低功耗Σ-Δ調制器的設計[J].微電子學與計算機,2011,28(11):76-80.

[2] 劉燕娟,程東方.用于電池電量測量的Delta-Sigma調制器設計[J].微電子學與計算機,2013,30(7):82-85.

[3] Chen Hsinliang,Chen Po-sheng,Chiang Jen-shiun.A low-offset low-noise sigma-delta modulator with pseudorandom chopper-stabilization techniques[J].IEEE Transactions on circuits and systems-I:Regular Papers,2009,56(12):2533-2543.

[4] LEE K L,MEYER R G.Low-distortion switched-capacitor filter design techniques[J].IEEE Journal of Solid-State Circuits,1985,SC-20(6):1103-1112.

[5] 張永來.18位精度音頻Sigma-Delta ADC的設計[D].哈爾濱:哈爾濱工業大學,2013.