文獻標識碼: A

文章編號: 0258-7998(2015)04-0116-03

中文引用格式:彭海,高俊雄,王耘波.一種應用于生物識別領域的AES算法[J].電子技術應用,2015,41(04):116-118

0 引言

生物識別技術方便、快捷、安全可靠,已被廣泛應用于部隊、政府機關、高檔小區等對安全系數要求較高的場合,并且呈快速發展的趨勢。然而隨著生物識別技術的大量應用,人們對生物識別技術的安全性和隱私問題的關注也越來越多[1]。生物識別技術一般對生物特征(如指紋、虹膜等)進行取樣,提取其唯一特征并且轉化為特征模板,根據特征模板進行匹配。特征模板就像生物識別技術里的“鑰匙”,一旦被修改將直接影響其識別結果。因此,采集模板時利用AES加密算法對模板數據進行加密,進行識別時取出加密后的模板并將其解密。這種以AES算法實現對模板數據的加密可大大提高生物識別的安全性。生物識別系統在識別時往往要遍歷所有模板,而由于用戶基數龐大,數據庫中一般存在大量的特征模板,因此系統對解密的速度要求非常高。

AES加密算法由美國國家標準與技術研究所(NIST)在2002年建立,它可以使用128 bit、192 bit或256 bit密鑰,并用128 bit(16 B)分組加密和解密數據。現階段AES加密主要通過軟件編程或硬件邏輯實現。采用軟件編程實現的方法具有成本低、靈活的特點,但軟件實現的AES易被修改,且速度較慢;采用硬件邏輯實現的AES加密算法除了高效和安全外,還保證了很高的速度,所以在生物識別領域十分適用。本文主要論述了在FPGA硬件平臺下實現的一種大吞吐量256 bit密鑰的AES算法,因AES加密與解密的過程基本相同,故主要論述了AES算法的解密過程在FPGA上的實現。

1 AES算法簡介

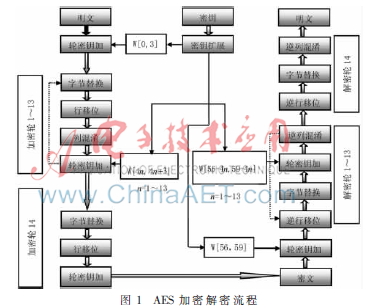

AES算法是基于置換和代替的。置換是指數據的重新排列,而代替是用一個單元數據替換另一個。圖1顯示了AES(256 bit)加密解密的完整流程。

AES加密算法把輸入的128 bit數據看成是一個名為State狀態矩陣的4×4的字節矩陣。加密過程就是對State狀態矩陣進行多輪操作[2]。算法開始前首先構造用于加密的兩個表,一個是用于字節替換的S-box表,另一個是用于產生輪密鑰的密鑰調度表。算法首先進行AddRoundKey(輪密鑰加),即用密鑰調度表中的前4行對State矩陣進行異或操作。然后是AES加密算法的主循環,循環的次數由輸入密鑰的長度決定,如密鑰位數為256 bit,則循環總輪數為14輪。AES算法的加密主循環每輪對State狀態矩陣執行4個不同的操作,分別是SubBytes(字節替換)、ShiftRows(行移位變換)、MixColums(列混淆變換)和AddRoundKey(輪密鑰加),其中最后一輪不進行ShiftRows(行移位變換)。字節替換是指通過S盒對狀態矩陣進行替換,行移位變換是指狀態矩陣的每一行進行循環移位,列混淆變換主要用到了GF28域上的乘法和加法運算,而輪密鑰加是簡單的異或運算。AES解密主循環是加密循環的逆過程,解密主循環中也有對應的逆變換:Inv_SubBytes(逆字節替換)、Inv_ShiftRows(逆行移位變換)、Inv_MixColumns(逆列混淆變換),這些變換均可看成加密主循環中4個變換的逆變換。

2 AES算法的FPGA實現

2.1 FPGA技術簡介

現場可編程門陣列FPGA(Field Programmable Gate Array)是美國Xilinx公司于1984年首次開發的一種通用型用戶可編程器件。FPGA既具有門陣列器件的高集成度和通用性,又有可編程邏輯器件的靈活性。

FPGA結構靈活,其邏輯單元、可編程內部連線和I/O單元都可由用戶編程,可實現任何邏輯功能,滿足各種設計需求。其速度快、功耗低、通用性強的特點適用于復雜系統的設計[3]。FPGA技術還可以實現動態配置、在線系統重構(可以在系統運行的不同時刻,按需要改變電路的功能,使系統具備多種空間相關或時間相關的任務)及硬件軟化、軟件硬化等功能。

2.2 使用FPGA實現AES算法

2.2.1 系統的總體結構

根據AES算法輪操作的特點,本文采取基本迭代與串行緩存相結合的方法,系統總體實現框圖如圖2所示。通過14個AES解密模塊并行使用,大大提高了吞吐率,其中每個AES解密模塊采用基本迭代的方法,即所有輪次復用一個輪函數,每個時鐘周期完成一次輪操作,14個時鐘周期完成一個分組運算。

解密數據時,首先讓密文數據依次進入串行緩存,串行緩存的深度與AES算法的輪數相同(為14),進入串行緩存的數據依次進入AES解密模塊進行解密。第一個時鐘周期,讓密文數據進入Data_buffer1,然后啟動第一個AES解密模塊AES1;第二個時鐘周期,讓新的密文數據進入Data_buffer2,然后啟動第二個AES解密模塊AES2;依此類推,往復循環。14個AES解密模塊的啟動順序如圖3所示。

每經過14個時鐘周期,將每個AES解密模塊的結果依次移位輸出。采用這種結構實現的AES解密算法雖然消耗了不少FPGA的內部資源,但數據無需等待,可以源源不斷地進入解密模塊,整個解密過程的速度僅僅取決于單個AES解密模塊的工作頻率與數據輸入的速率,使得系統的吞吐率大大提高。考慮到FPGA內部資源豐富,可以犧牲部分資源來換取速度。

2.2.2 AES解密模塊的實現

AES解密前,首先要進行密鑰擴展。密鑰擴展是將初始密鑰作為種子密鑰,經過字節代換、字節移位、輪常數計算、字節異或等過程,計算產生14輪迭代所需的輪密鑰。密鑰擴展實現框圖如圖4。有文獻提出計算密鑰時密鑰擴展和加密過程同步執行,這樣做會節約FPGA的存儲器資源。但考慮到密鑰不需要經常更換,而且FPGA存儲器資源豐富,有足夠的空間存放子密鑰,所以本文決定在解密前先進行密鑰擴展,然后將產生子密鑰存放在RAM中,根據使用需要從RAM中讀取密鑰。這種方法易于實現,且靈活性強,產生好的密鑰調度表在種子密鑰不變的情況下都可以供其他模塊使用。

密鑰擴展完成后,就可以開始進行解密。256 bit的AES解密過程總共需要14輪,除最后一輪外每輪需要進行字節替換、逆行移位、輪密鑰加、逆列混淆等4個操作,最后一輪不需要進行輪密鑰加。其實現框圖如圖5所示。

逆行移位(Inv_ShiftRow)采用簡單的組合邏輯即可實現;逆字節替換(Inv_SubBytes)利用FPGA內部的分布式RAM實現,將逆S_BOX的值預先存入到RAM中,在進行逆字節替換時,以字節的高4位和低4位作為地址即可讀出要替換的值,這樣既避免了復雜的組合邏輯,又提高了系統的運行頻率;輪密鑰加(AddKey)為簡單的異或運算;逆列混淆(Inv_MixCol)的實現采用了將復雜的GF28域乘法逐次分解為基礎的GF28域乘法的方法,使整個過程易于在FPGA中實現。

3 實驗結果

本設計在Xilinx公司的XC7A200T-2芯片上進行驗證,圖6給出了系統的在Isim仿真環境下的仿真圖。

輸入密文為16進制數8960494b9049fceabf456751cab-7a28e,密鑰為16進制數1f1e1d1c1b1a1918171615141312-

11100f0e0d0c0b0a09080706050403020100,14個周期后輸出解密后的明文為16進制數ffeeddccbbaa998877665544-33221100。經驗證,該解密過程完全正確。

在ISE13.6環境下代碼在綜合后頻率可達到236.9 MHz,由于采用串行緩存的方法,數據可以持續加密,無需等待上一個數據加密完。經計算理論吞吐量可以達到30.3 Gb/s,完全適用于各個應用場合的需要。

4 結論

采用FPGA實現AES算法可以大幅度提高加密解密速度,并且具有開發周期短、易于實現的特點;采用本方法實現的AES算法雖然占用了較多的FPGA資源,但加密解密速度得到大大的提高,吞吐量可達到30.3 Gb/s,完全滿足現行生物識別技術的要求,能廣泛應用于虹膜識別技術及指紋識別技術等領域,應用前景廣闊。

參考文獻

[1] 趙洋.生物識別系統中的模板安全分析[J].中國安防,2012,3(3):99-104.

[2] DANMEN J,RIIJMEN V.AES proposal:rijndael.AES algo-rithm submission.[EB/OL](1999-09-03)[2014-12-23].http://www.nist.gov/aes.

[3] Clive Max Maxfield.FPGA設計指南:器件、工具和流程[M].北京:人民郵電出版社,2007.