文獻標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2015.09.015

中文引用格式: 劉兵,吳虹,王琦琦,等. 硬件電路信號失真解析方法在便攜產(chǎn)品顯示電路的應(yīng)用[J].電子技術(shù)應(yīng)用,2015,41(9):55-59.

英文引用格式: Liu Bing,Wu Hong,Wang Qiqi,et al. Techniques in LCD module circuit design for reducing signal distortion[J].Application of Electronic Technique,2015,41(9):55-59.

0 引言

當(dāng)今TFT LCD液晶顯示屏在便攜類電子產(chǎn)品中的應(yīng)用非常普遍,隨著用戶對屏尺寸、顯示分辨率、響應(yīng)時間等參數(shù)要求的不斷提高,顯示模組要處理圖像信息的數(shù)據(jù)量和數(shù)據(jù)傳輸速率也在逐步增加。例如,很多大屏手機、PAD視頻數(shù)據(jù)接口中,傳統(tǒng)的RGB等數(shù)據(jù)傳輸協(xié)議正在被更高傳輸速率的數(shù)據(jù)傳輸協(xié)議(例如Mipi,等)所取代。單條Mipi數(shù)據(jù)通道的數(shù)據(jù)傳輸速率已接近1 Gb/s[1],因此,高速電路中經(jīng)常遇到的信號完整性問題如今也不斷在顯示模組的產(chǎn)品設(shè)計、測試中出現(xiàn)。

便攜類電子產(chǎn)品中顯示模組的屏尺寸與分辨率等參數(shù)指標(biāo)的不斷提升,也導(dǎo)致顯示模組的電路復(fù)雜度、工作耗電的相應(yīng)增加,而產(chǎn)品設(shè)計同時又受到低功耗設(shè)計的約束。盡管顯示驅(qū)動芯片廠家與面板廠家在優(yōu)化電路、提升工藝水平等方面不斷探索改善電源設(shè)計、降低模組功耗的方法,但仍有一些顯示模組在應(yīng)用中會因過大的浪涌電流導(dǎo)致電源電壓不穩(wěn)甚至影響模組的正常顯示。因此,電源完整性也是TFT LCD產(chǎn)品設(shè)計中應(yīng)該重點關(guān)注的問題。

1 問題描述

在高速電路、微弱信號處理和其他對信號畸變敏感的應(yīng)用場合,經(jīng)常要考察電路信號的完整性問題。對于TFT LCD液晶顯示模組,因容易發(fā)生信號畸變而要重點考察的電路模塊主要集中在:高速數(shù)據(jù)接口端,當(dāng)數(shù)據(jù)速率上升到接近1 Gb/s時,接口處的信號反射、信號線的阻抗失配、信號線與功能電路之間或者信號線與信號線之間的輻射與耦合都可能影響信號的正確接收;屏幕尺寸的增加使得面板上gate、source信號線的數(shù)量、長度的同步增加,接口的信號驅(qū)動能力、線上寄生參數(shù)、GIP(Gate In Panel)電路的信號傳遞、工藝誤差等因素都可能影響gate、source線上信號的波形質(zhì)量,導(dǎo)致模組的亂顯甚至無顯。

在TFT LCD液晶模組產(chǎn)品設(shè)計中,忽視電源設(shè)計可能導(dǎo)致嚴(yán)重的顯示故障,例如顯示模組內(nèi)部的多電源在上電時電壓上升速率不同,或者多電源之間的上電時間差,可能引起過沖電流與電源電壓的波動,在極端條件下甚至?xí)绊懩=M的正常顯示。因此,在電路設(shè)計中除了要遵循常規(guī)的電源、地設(shè)計規(guī)范[2],檢測顯示模組在工作電源(尤其是多電源)上電過程中工作的可靠性,也成為衡量顯示模組電源設(shè)計質(zhì)量的一項重要內(nèi)容。

2 TFT LCD顯示模組內(nèi)部電路信號完整性問題解析

2.1 高速數(shù)據(jù)接口及信號連接線

下面以Mipi DSI接口的液晶顯示模組為例來分析其內(nèi)部高速數(shù)據(jù)信號失真。參照Mipi協(xié)議,數(shù)據(jù)接口一般包含1~4組差分?jǐn)?shù)據(jù)信道,其中信道1既能工作于低功耗模式(傳輸指令信息)又能工作于高速數(shù)據(jù)傳輸模式(傳輸圖像數(shù)據(jù)),信道2~4工作于高速數(shù)據(jù)傳輸模式以傳送圖像數(shù)據(jù)。低功耗模式下數(shù)據(jù)傳輸速率小于10 Mb/s,差分信號的高、低電平的電位差約1.2 V,此時信號發(fā)生畸變的程度很輕微,信號出現(xiàn)誤判的可能性低。這里將重點討論的是當(dāng)數(shù)據(jù)信道工作于高速傳輸模式,每條差分信道的數(shù)據(jù)速率接近1 Gb/s,而差分信號的高、低電平之間的電位差只有0.2 V,容易由于端口失配、信號線阻抗控制不良、線間干擾等引起傳輸信號畸變而導(dǎo)致誤傳。

為避免出現(xiàn)上述信號失真,在產(chǎn)品設(shè)計中應(yīng)加強對工藝與電路設(shè)計參數(shù)的管控。例如:信號連接FPC軟板材料與層厚;關(guān)鍵信號線阻抗值,差分信號線的線寬、線距;版圖設(shè)計中接口pin腳的形狀、信號線拐角、差分信號線的等長控制。這些是電路設(shè)計中的常規(guī)項,本文不作贅述。

當(dāng)前模組中常采用的COG(Chip On Glass)工藝中,顯示模組的數(shù)據(jù)接口一般是通過一段FPC傳輸至玻璃基板上的顯示驅(qū)動芯片。高速數(shù)據(jù)信號由電子產(chǎn)品的核心處理器發(fā)出,在傳輸?shù)揭壕э@示模組的路徑中,會經(jīng)過PCB或FPC等傳輸介質(zhì),這里將討論數(shù)據(jù)信號在此傳輸過程中可能發(fā)生的干擾與失真。

這里用作分析的顯示模組測試電路中,中央處理器所在的PCB板上有四路Mipi數(shù)據(jù)信道,分析的手段是通過仿真其在高速傳輸時的性能,以提升其在高溫、EMI干擾等極端環(huán)境下的工作可靠性。采用Cadence信號完整性仿真軟件包[3],分析PCB板上Mipi高速數(shù)據(jù)信道的EMI與Crosstalk等性能。

軟件仿真前,先指定電路的直流網(wǎng)絡(luò)與差分對信號,再設(shè)置電路中元件的仿真模型。本次仿真中由于部分芯片的IBIS模型沒能從其供應(yīng)商獲得,仿真中對其在軟件中取默認設(shè)置,這會對仿真精度產(chǎn)生一定影響。考慮Mipi信號的特點,下面以考察兩條數(shù)據(jù)信道之間信號串?dāng)_為例,圖1所示為提取信道1中D1P信號線的電參數(shù)模型。

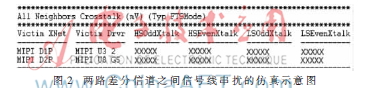

線間串?dāng)_與線之間的平行長度成正比,與線間距成反比。在設(shè)計PCB測試板的版圖時,應(yīng)注意降低幾條數(shù)據(jù)信道之間的信號串?dāng)_。MIPI DSI數(shù)據(jù)線之間的信號串?dāng)_,在一般情況下,相鄰數(shù)據(jù)線之間的串?dāng)_高于距離較遠數(shù)據(jù)線之間的串?dāng)_,高速數(shù)據(jù)傳輸模式下信號線之間串?dāng)_高于低功耗模式下的串?dāng)_。本次仿真為了簡化過程,只考慮兩條信號線之間的串?dāng)_。圖2是選取兩條相鄰差分信道的正極性信號線D1P、D2P之間在高速數(shù)據(jù)傳輸模式下的串?dāng)_值。(這里只是說明仿真步驟,數(shù)值用‘X’符號代替)圖2中參數(shù),例如HSOddXtalk表示當(dāng)Victim信號線維持高電平,附近信號線上的降脈沖對Victim信號線產(chǎn)生的干擾電壓,詳細介紹參看軟件幫助文檔[4]。

受干擾信號線(圖2中victim)上感應(yīng)到的干擾電壓值應(yīng)小于該信號的電平翻轉(zhuǎn)判決閾值,以免造成誤判。經(jīng)過對本實驗選取模組的實測,高速數(shù)據(jù)傳輸?shù)男诺乐胁罘謱€高、低電平差的典型值約180 mV;參看該模組內(nèi)液晶顯示驅(qū)動芯片的數(shù)據(jù)手冊,其規(guī)定了接收到高速差分信號高、低電平的判決閾值電壓,分別是70 mW、-70 mV;根據(jù)以上因素可適當(dāng)設(shè)定信號線能承受串?dāng)_的電壓容限值(假設(shè)在不考慮串?dāng)_以外的干擾因素的前提下),例如40 mV。如果仿真的結(jié)果顯示串?dāng)_值較大,可以采用以下措施來改進:在PCB板上空間足夠的情況下,適當(dāng)加大數(shù)據(jù)信道之間的距離以降低線間串?dāng)_;同時,在數(shù)據(jù)走線之間的位置擺放一些靜態(tài)元件,在增大線間距的同時也減小了平行走線長度。

另外,使用該軟件也可以得出高速數(shù)據(jù)信號線的遠場輻射仿真值用于驗證產(chǎn)品的EMI性能,限于篇幅這里不作討論。

下面對顯示模組內(nèi)部連接軟板FPC的信號傳輸損耗與端口阻抗匹配性能進行軟件分析。設(shè)FPC采用雙層銅工藝,兩層分別為top、bottom,其中top層用于數(shù)據(jù)信號、電源布線。在FPC的信號輸入與輸出端,信號線都要跨過一段無bottom金屬的區(qū)域,這也會對數(shù)據(jù)傳輸線的性能產(chǎn)生影響,下面用軟件驗證這種版圖布局的信號傳輸性能。

使用Allegro繪制顯示模組的FPC電路,然后導(dǎo)入Ansoft軟件,設(shè)置電源、地、信號線的頻率與電壓等參數(shù),如圖3所示。

繪制的版圖導(dǎo)入Ansoft軟件后,選擇要分析的一對差分信號線D0P、D0N(圖3中高亮顯示的兩條平行相鄰信號線,其輸入與輸出端分別為in_P與out_P、in_N與out_N),這里仿真其信號傳輸損耗與端口反射,仿真結(jié)果如圖4所示。

用軟件仿真FPC上一組差分對信號的S參數(shù),由仿真結(jié)果圖4可知,在100 MHz~1.5 GHz頻段,MIPI DSI數(shù)據(jù)線的傳輸損耗小于0.5 dB;數(shù)據(jù)線輸入端與輸出端的端口反射都小于-18.5 dB,對應(yīng)的端口反射波與入射波的電壓幅度比值約為0.11,反射波在入射波上疊加引起的信號幅值變化約10%,在可接受的范圍以內(nèi)。產(chǎn)品經(jīng)實測可正常工作,但在實際生產(chǎn)中應(yīng)當(dāng)注意控制數(shù)據(jù)線的端口阻抗值與匹配性能,同時,在以后的項目設(shè)計中還可以從FPC工藝改進的角度獲得進一步優(yōu)化。

2.2 行、列驅(qū)動信號

下面以DC VCOM(VCOM是直流電平)、8 phase GIP類型的TFT LCD面板作為考察對象,分別對source信號線、gate信號線進行討論。

2.2.1 Source信號線

液晶面板source線電壓對精度要求高,其電壓精度一方面受限于驅(qū)動芯片中source信號D/A轉(zhuǎn)換器的精度,另一方面也受到source信號線輸出端驅(qū)動能力的影響,這是因為驅(qū)動過強或者過弱導(dǎo)致source信號波形的過沖或信號電壓上升過緩,都延長了電壓穩(wěn)定時間。

TFT LCD面板電路具有一些不同于普通電子線路的特點:單元門電路多,晶體管總量龐大;單元電路重復(fù)度高;器件遷移率低,面板上一些器件尺寸較大,同時版圖中一些信號線長度可達幾十厘米,因此電路的寄生參數(shù)對性能影響大[5]。由于以上原因,在建立仿真模型時,保證仿真精度的同時降低軟件資源的占用就成為重點關(guān)注的問題。

對TFT LCD顯示模組的源信號仿真常采用的形式是:對LCD面板上幾條關(guān)鍵信號線、像素電容等提取等效參數(shù)模型,然后將其作為負載,與顯示驅(qū)動芯片的電路驅(qū)動模型作聯(lián)合仿真。

考慮以下應(yīng)用場景:當(dāng)掃描的行逐次遞進時,一條source線的驅(qū)動模型也會隨之產(chǎn)生變化。由于液晶電容在不同電壓下的容值會發(fā)生變化,為了統(tǒng)一標(biāo)準(zhǔn)進行比較,這里選取的液晶電容值分別是在最高偏壓、零偏壓的近似電容值。同時根據(jù)仿真經(jīng)驗值,將一條source線等分成20段傳輸線的仿真精度與等分成更多段的仿真精度上的差異可忽略不計,這里建立了簡化的仿真模型電路并進行仿真驗證。仿真結(jié)果顯示,掃描行遞進過程中負載模型變化產(chǎn)生的影響微弱,設(shè)計中可忽略考慮。

另外,當(dāng)前仿真中經(jīng)常將source線驅(qū)動模型簡化為少數(shù)幾段傳輸線與幾只負載電容的形式,這會輕微影響仿真的精度,在其他文獻中有詳細介紹[6],這里不作贅述。

2.2.2 柵電路信號失真

當(dāng)前LCD面板設(shè)計中GIP電路正得到越來越廣泛的應(yīng)用,這里以8 phase GIP電路為例,設(shè)TFT LCD產(chǎn)品的gate線掃描方向是從屏上邊緣依次掃描至下邊緣。而gate信號的產(chǎn)生與傳遞單元一般采用mTnC結(jié)構(gòu)(T: transistor;C: capacitor;m、n為正整數(shù))。設(shè)面板共K條gate線,那么面板的左右兩側(cè)分別有K/2個mTnC單元電路。每8條相鄰gate線構(gòu)成一組完整的gate信號變化周期。GIP電路一般包括以下信號線:分別位于面板左右兩側(cè)的左側(cè)開始信號/右側(cè)開始信號、左側(cè)終止信號/右側(cè)終止信號、左側(cè)時鐘信號/右側(cè)時鐘信號、柵高電平信號、柵低電平信號,上述信號線都是由顯示驅(qū)動芯片所驅(qū)動。其中開始、終止、時鐘信號線連接的是GIP電路中TFT晶體管的柵極;柵高電平、柵低電平信號連接GIP電路中TFT晶體管的源極/漏極[7]。

在設(shè)計TFT LCD面板的gate驅(qū)動電路時,可能遇到以下問題:TFT LCD面板載流子的低遷移率導(dǎo)致薄膜晶體管的低跨導(dǎo)特性,一些器件的幾何尺寸較大,其對應(yīng)較大的器件寄生參數(shù)可能引起GIP信號的失真;由于gate金屬的電阻率較source金屬的大,而且金屬厚度薄,其信號更容易產(chǎn)生畸變;當(dāng)前顯示屏普遍要求的窄邊框設(shè)計,進一步壓縮GIP電路所占面積與薄膜晶體管尺寸,導(dǎo)致設(shè)計余量預(yù)留不足,在生產(chǎn)與使用過程中出現(xiàn)gate信號線受ESD損傷、雜質(zhì)污染或水汽腐蝕的現(xiàn)象,這也使gate信號容易發(fā)生畸變。例如,圖5所示為某款顯示模組的面板邊框因受水汽入侵,箭頭指示的是水汽入侵方向,該區(qū)域的GIP電路被腐蝕而不能正常產(chǎn)生與傳遞GIP信號,導(dǎo)致顯示屏上此位置以下的部分出現(xiàn)隔行暗線。

因此,每一mTnC單元電路傳遞的一組邏輯信號要保證邏輯正確,同時還要避免出現(xiàn)由于信號在逐行傳遞過程中的能量衰減而導(dǎo)致邏輯錯判[8]。

3 TFT LCD顯示模組電源完整性分析

3.1 設(shè)計要求

顯示模組內(nèi)部一般有多個工作電源,多電源之間的上電斜率(指在“電壓/時間”二維平面中,電源電壓值上升的斜率)不同,或者多電源之間的上電時間差,都可能導(dǎo)致浪涌電流的發(fā)生。浪涌電流可直接影響電源電壓的穩(wěn)定時間、電壓紋波幅度,隨之引起相應(yīng)電源完整性問題,嚴(yán)重時甚至?xí)绊懩=M的正常顯示。這里要設(shè)計的測試電路,要求能夠產(chǎn)生可調(diào)的電源電壓上電斜率,同時要求能夠產(chǎn)生可調(diào)的多電源之間上電時間差。

實驗中所選顯示模組有兩個工作電源,分別是V1、V2,對其上電過程的要求如下:

V1與V2電壓上升斜率的典型值分別為0.1 V/s與0.2 V/s,且斜率可調(diào);

V1與V2電壓上電時間差的典型值100 ?滋s,且兩路上電時間差值可調(diào)。

下面提出一種簡易測試電路,可以方便地調(diào)整上述參數(shù)值。

3.2 電路設(shè)計與測試

由電阻分壓關(guān)系得到V1、V2電壓值,同時在電阻分壓點連接充電電容,近似得到上電過程所要求的上電斜率;利用驅(qū)動器電路的輸出跟隨輸入電壓變化的特性,可以將足夠電源負載能力的輸出電壓作為測試模組的工作電源,如圖6所示。圖中PCB板是借用自其他項目,在這里僅使用板上的驅(qū)動器電路,增加其他電子分立元件來組成所要求的測試電路。

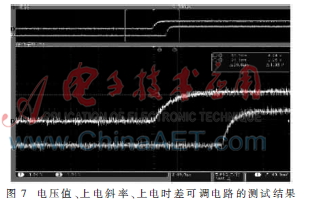

當(dāng)圖中黑色按鈕開關(guān)閉合,C12電壓從0 V~2.75 V上升斜率0.1 V/?滋s,得到要求的上電斜率;等比例調(diào)整分壓電阻值或改變電容值可獲得不同的電源上電斜率值。當(dāng)電源要求的電壓值固定且上電速率也固定時,可選用圖6(a)所示定值電阻、電容串,在要求電壓值、上電速率可調(diào)時,應(yīng)采用圖6(b)所示的數(shù)值可調(diào)電阻、電容串結(jié)構(gòu)。圖6(c)顯示了測試得到上電斜率為0.1 V/s的輸出電壓。

為了得到兩路延遲不同、兩電源上電時間差可調(diào)的測試電路,要采用兩組圖6(b)中所示的上電延遲電路;為得到兩路電源之間的上電時間差,同樣用電容與可調(diào)電阻構(gòu)成RC延時控制。第一路電源的上電開始時刻由手控開關(guān)控制,第二路電源的上電時刻由電源之間上電時間差調(diào)節(jié)電路搭配電控開關(guān)來控制。

兩電源之間的上電時間差對應(yīng)的延時控制信號用施密特觸發(fā)器進行反相與簡單的波形整形;手控開關(guān)采用的軟按鈕,防止簧片式硬按鍵開關(guān)的接觸抖動;電控開關(guān)采用響應(yīng)速度快、導(dǎo)通阻抗低(標(biāo)稱值1 Ω)的SPST(單刀單擲開關(guān))。

根據(jù)上面所述搭建所要求的電壓值、上電斜率、上電時差可調(diào)電路,再對電路測試驗證,得到如圖7所示測試曲線,基本能滿足設(shè)計要求。

4 總結(jié)

針對TFT LCD顯示電路中模塊信號失真問題與電源可靠性驗證的要求,本文介紹其解析方法與仿真步驟,經(jīng)軟件仿真與電路測試,結(jié)果表明所提出方案可以滿足設(shè)計要求。

但是隨著顯示模組的數(shù)據(jù)速率、分辨率等性能參數(shù)的進一步提升,將對產(chǎn)品設(shè)計提出更高要求;而且,當(dāng)前產(chǎn)品設(shè)計中仍存在著信號抗干擾能力不夠強,例如在ESD測試、高溫高濕等極端環(huán)境下容易顯示異常,這些有待對LCD面板、顯示驅(qū)動芯片的信號完整性問題作更深入分析,進一步降低產(chǎn)品的信號失真,提高工作可靠性。

參考文獻

[1] MIPI Alliance,Inc.MIPI DSI Specification_v1.02.00 Draft Version 1.02.00.2010.

[2] 周潤景,蘇良昱.Cadence高速電路板設(shè)計與仿真(第4版):信號與電源完整性分析[M].北京:電子工業(yè)出版社,2011.

[3] 陳蘭兵,鐘章民.Cadence高速電路設(shè)計:Allegro Sigrity SI/PI/EMI設(shè)計指南[M].北京:電子工業(yè)出版社,2014.

[4] Cadence Design Systems,Inc.Allegro PCB SI User Guide.Version 16.3,2009.

[5] Hitoshi Aoki.Dynamic characterization of a-Si TFT-LCD pixels[J].IEEE Transactions on Electron Devices,1996,43(1).

[6] 戴亞翔.TFT LCD面板的驅(qū)動與設(shè)計[M].北京:清華大學(xué)出版社,2008.

[7] Liao Congwei,He Changde.Design of integrated amorphous-silicon thin-film transistor gate driver[J].Journal of Display Technology,2013,9(1).

[8] Chiu Yingju,Lee Kuofu.Amorphous silicon thin-film tran-sistor gate driver circuit design optimization using a simula-tion based evolutionary technique[C].Melaka,Malaysia,ICSE2010 Proc.2010.