文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.10.005

中文引用格式: 陸振林,趙元富,蘭利東,等. 基于可重構技術的DSP任務動態加載方法研究[J].電子技術應用,2015,41(10):24-26,33.

英文引用格式: Lu Zhenlin,Zhao Yuanfu,Lan Lidong,et al. Research on dynamic loading method of DSP task based on reconfigurable technology[J].Application of Electronic Technique,2015,41(10):24-26,33.

0 引言

隨著微納衛星、片上衛星的快速發展,對其電子系統的微小型化、低功耗的需求日趨明顯。傳統的多模塊拼裝的設計模式需要多個分離電路才能夠構建完整的系統,顯然,不能滿足未來的發展需求。而集成微系統作為扁平化設計的新模式,將信息感知、數據處理、驅動控制等功能單元,采用MCM、SIP、TSV等封裝技術,集成在一個芯片大小的封裝體內,極大地提升了系統的集成度。

為了支撐微系統芯片對實時控制、高性能運算的要求。課題組提出了異構多核微系統的解決方案。其中,DSP作為協處理器,主要負責計算任務的執行。為了支撐運算任務類的靈活調度和映射的需求,DSP處理器的任務動態加載技術已成為急需突破的關鍵技術之一。

文獻[1]通過SN74LVT16245A(雙向三態收發器),將ARM總線和DSP處理器HPI接口進行互連,構建了ARM與DSP之間視頻數據可靠傳輸通道,實現了大數據量的搬移,文獻[2]面向實時圖像處理的運算需求,通過DSP HPI接口,構建PowerPC處理器與DSP處理器的通信;文獻[3]設計了ARM與DSP HPI的通信接口,通過162245總線隔離器進行數據總線的互連,完成了ARM對DSP程序的動態加載。還有其他的研究人員開展過相似的研究[4-7]。

以上的研究成果表明,通過HPI接口能夠實現ARM處理器與DSP的數據交互,但設計方案都需要額外增加總線隔離器件來解決處理器與DSP的總線干擾問題。針對微系統而言,該方法存在以下問題:首先,該方法增加了芯片設計、測試的復雜度,帶來系統體積和功耗的增加;其次,ARM處理器的總線時序與國產處理器并不相同;最后,研究中對數據總線進行了隔離,但是ARM的地址線、總線控制信號等與HPI直連的方式,在DSP處理器出現異常時,將有可能造成對主處理器總線信號的影響,導致主處理器無法正常工作。

因此,本課題提出了一種“基于可重構技術的DSP任務動態加載技術”的方法。該方案針對芯片級微系統對任務動態加載的需求,基于可編程邏輯器件自身資源,采用可重構技術,通過突破并行配置接口設計、數據動態加載等關鍵技術,解決異構多核芯片中DSP處理器的動態加載的問題。

1 基于可重構技術的注入通路設計

異構多核微系統芯片集成了國產SPARC V8處理器、FT-DSP處理器、FPGA、SDRAM、SRAM等器件。為了實現SPARC V8處理器向DSP處理器動態注入程序,并可控制其進行啟動。文中利用了FT-6713的HPI接口(Host Port Interface)。HPI是一個并行端口,是外部主機(host)與DSP系統進行數據交換以及host配置各個外設寄存器的接口,可實現高速、并行的數據通信。FT-6713的HPI是16位寬的并行接口,V8處理器可通過HPI直接訪問FT-6713的存儲空間和外圍設備。HPI接口信號如表1所示。

在通過HPI接口對DSP存儲空間的訪問時,需要解決如下問題:

(1)V8處理器與HPI接口互聯的設計:由于V8處理器不存在與HPI接口相匹配的接口,需要采取合適的互連方法,以滿足HPI操作的時序要求;

(2)HPI總線與V8總線串擾問題:在接口互連時,需要將總線信號、控制信號與HPI接口進行連接,當總線都進行操作時,將無法避免地帶來數據的串擾,甚至導致任務執行崩潰。

本文結合HPI接口時序和V8處理器的總線時序,提出了如下的互連方案:

(1)V8處理器具有獨立的地址和數據總線,因此,DSP的HPI接口的HAS由外部上拉至高電平。

(2)V8處理器的讀使能信號(OEN)、寫使能信號(Writen)、IO空間片選信號(CS)分別連接到DSP的HPI接口上3個觸發信號HDS1、HDS2和HCS,而HDS1、HDS1、HCS共同產生HPI使能觸發信號。

(3)V8處理器的地址線ADDR[7:6]與HPI的控制信號HCNTL[1:0]互連,以決定對HPI接口進行操作的目標寄存器,如HPIC、HPIA或HPID。

(4)V8處理器的地址線ADDR[4]與HPI的控制信號HHWIL互連,以此來指示當前數據總線傳輸的字節順序。

(5)V8處理器的地址線ADDR[5]與HPI的HR/W互連,用于控制當前操作是在對DSP的HPIA、HPIC、HPID寄存器執行何種操作。

(6)V8處理器的Brdyn信號上與HPI的HRDY互連,用于表明HPI是否已準備好傳輸數據。

(7)V8處理器的外部中斷與HPI的HINT信號互連,向主機發出中斷信號。

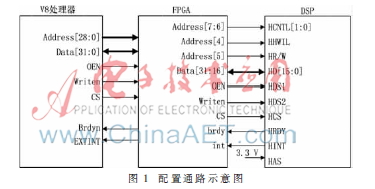

為了避免額外增加隔離芯片所帶來的各種弊端,本課題提出了基于芯片內部FPGA的可重構實現方案。在需要進行DSP加載時,通過動態重構技術,在FPGA中加載并實現DSP HPI互聯隔離邏輯,構建DSP的配置通路,當V8處理器完成對DSP程序加載后,V8處理器控制FPGA對隔離邏輯進行再次重構,斷開DSP HPI接口與V8處理器的總線互聯通路,以保證DSP處理器的異常不會對V8處理器造成影響。其連接示意圖和FPGA內部邏輯如圖1所示。

2 DSP任務的動態加載

2.1 動態啟動模式

通過HPI接口對FT-6713處理器的程序注入和啟動,需要持續對FT-6713處理器的3個寄存器進行操作,即HPI控制寄存器(HPIC)、HPI地址寄存器(HPIA)、HPI數據寄存器(HPID)。

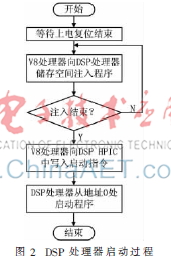

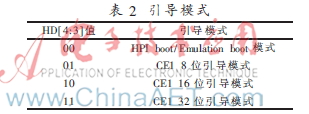

圖2顯示了HPI的啟動流程。系統上電復位后,首先采樣HPI接口的HD[4:3]的狀態確定啟動方式(即引導模式),如表2所示。為了能夠動態加載和啟動,本方法選擇HPI啟動模式,即HD[4:3]上電時默認為低電平。

FT-6713上電后,芯片外設控制器首先啟動,內核處于掛起狀態;此時外部主機通過HPI接口對DSP進行配置, 通過HPI初始化DSP的CPU core和EMIF,并向DSP加載程序和數據,將代碼和數據加載到DSP的內存中,在這期間DSP內核保持掛起狀態不變;當主機完成程序加載后,主機向HPIC寄存器中的DSPINT位寫1,向DSP發出中斷;DSP收到中斷后,DSP內核從掛起狀態喚醒,從0地址處啟動,開始執行程序。

2.2 基于軟件驅動的程序加載

V8處理器向DSP處理器注入程序,通過HPIC、HPIA、HPID和16位數據線與DSP進行數據交換和中斷控制。DSP處理器程序注入的實現流程如圖3所示。

(1)初始化HPIC

HPIC寄存器用于控制HPI的握手信號使能HRDY、字節傳輸順序控制等。初始化該配置寄存器后,使HPI控制器進入V8所需的工作模式。

(2)初始化HPIA

通過向該地址寄存器寫入待注入數據的地址,以便HPI控制器將相應的數據輸出到相應的存儲區。

(3)向HPID寫入數據

HPID用于暫存由V8處理器注入的配置信息,寫入方式具有自增寫入模式和固定寫入模式。由HCNTL[1:0]信號控制。本文選擇自增寫入模式。

(4)HPI啟動

當數據全部寫入DSP所屬存儲空間后,需要再次訪問HPIC,并向其DSPINT位寫入1來喚起DSP內核的啟動和程序的加載。

在程序啟動過程中,DSP會從0地址處開始執行。對于DSP的任務程序來說,是從c_int00處開始執行,需要使得程序跳轉到_c_int00處。

在生成和編譯DSP待注入程序,以及通過FPGA對HPI接口操作時,需要注意如下事項:

(1)由于項目中使用HPI16模式,因此對HPI任何一個寄存器的訪問,主機都需在HPI總線上進行2次半字存取。

(2)DSP的程序在下載的同時需要鏈接初始化的變量,因此需要在.cmd文件中使用-cr選項。

(3)FT-6713 DSP編譯器生成的文件為.out文件,構建動態加載數組時,對.out文件中有效配置信息進行提取。

3 測試

為了驗證所提出的動態加載方法的功能和性能,進行相關測試。V8處理器系統時鐘為80 MHz,DSP處理器內核運行時鐘為96 MHz。

3.1 功能測試

本文采用TEKtronix TLA7012邏輯分析儀對HPI接口的信號時序進行了跟蹤,采樣頻率為200 MHz。如圖4所示,左側兩個橢圓圈定的32 bit數據將寫入到HPIC寄存器,右側兩個橢圓圈定的第二個32 bit數據將寫入到HPIA寄存器中。從測試數據可知,在HPI接口獲取了正確加載的數據和時序。

3.2 性能測試

為了獲取V8處理器發起DSP任務數據注入至DSP處理器正確啟動的時間,設計了測試用例:V8發起程序注入后,拉高GPIO,DSP處理器在正確啟動后,所屬GPIO信號由低到高,兩個GPIO信號間的間隔即可認為DSP程序注入及啟動時間。如圖5所示為2個GPIO信號電平變化的情況。

V8處理器通過FPGA連接到DSP的HPI接口,并向其注入了大小為280 KB的程序數據,從圖中可見,整個動態加載和DSP運行時間僅為135 ms。

4 結論

針對系統級異構多核芯片的特點,協同工作的設計要求,提出了“基于可重構技術的”實現方法。該方法在無需增加總線隔離芯片和外部集成電路的情況下,通過構建的映射通路,V8處理器能夠將任務正確的注入到DSP處理器存儲空間,并啟動DSP處理器內核,完成任務的動態加載。

測試結果表明,對于一個大小為280 KB的代碼,從代碼注入到DSP內核啟動完成,所需時間僅為135 ms,能夠滿足系統的實時性要求。本文提出的方法滿足了系統級芯片任務動態映射的需求。

參考文獻

[1] 張力,劉正熙.ARM與DSP之間視頻數據可靠傳輸的設計與實現[J].計算機應用,2009(29);198-200.

[2] 余躍,孟慶東,李兆麟.一種面向實時圖像處理應用的基于非共享存儲的多DSP系統設計[J].電子技術應用,2009,35(3):29-32.

[3] 趙建波,胡文若,習勇,等.基于ARM的TMS320C6455-DSPHPI的動態程序加載設計與實現[J].電子技術應用,2013,39(6):14-16.

[4] OU S H,LIN T J,DENG X S,et al.Multithreaded copro-cessor interface for multi-core multimedia SoC[C].Design Automation Conference,2008.Asia and South Pacific,2008:115-116.

[5] Yao Yiyong,Zhao Liping,Li Xin,et al.Dual-core embeddedreal-time inspection and analysis platform for field quality control and application[M].Intelligent Robotics and Applica-tions.Springer Berlin Heidelberg,2008.

[6] FAN H,CHEN W,LIU J,et al.The application of HPI in laser scanning system based on dual-DSP[C].4th IEEE Conference on Industrial Electronics and Applications,2009:484-488.

[7] SHANG Q,DU C.A novel measurement system of electric power parameters based on DSP and ARM[C].2009 Inter-national Conference on Measuring Technology and Mecha-tronics Automation,2009:353-356.