文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.10.006

中文引用格式: 徐建松,俞拙非,侯凱,等. 一種基于FPGA的閥基電子設備的研制[J].電子技術應用,2015,41(10):27-29,33.

英文引用格式: Xu Jiansong,Yu Zhuofei,Hou Kai,et al. The development of VBE based on FPGA[J].Application of Electronic Technique,2015,41(10):27-29,33.

0 引言

隨著直流輸電技術和電力電子技術的迅速發展,晶閘管換流閥得到了廣泛的應用。在高壓直流輸電中,控制保護系統(Converter Control and Pprotection,CCP)、閥基電子設備(Valve Base Electronics,VBE)和門極驅動單元(Gate Driver Unit,發射、分配、解析控制保護系統產生的觸發命令并GDU)三部分構成晶閘管換流閥的二次觸發監控系統,其在高壓直流輸電工程中主要完成以下功能:發送到晶閘管級;監測保護晶閘管器件不受過高電壓的沖擊;在閥內發生過流短路時能即時停止觸發;對整個換流閥進行在線監測,上報設備與器件運行情況,并在出現故障時告警跳閘等。其穩定可靠性對換流閥系統的安全運行起著至關重要的作用[1,2]。

閥基電子設備主要由觸發回路和監測回路組成,是換流閥觸發監控系統的核心設備[1]。傳統閥基電子設備的核心控制一般是由微處理器或數字信號處理器完成[3],由于軟件執行的非實時性,加上控制通道數量越來越多,一些應用場合下VBE輸出的各路PWM脈沖之間出現不可控的相位延時差,甚至存在脈沖丟失的隱患[1],系統的可靠性和同步性難以保證。隨著電子技術的發展,具有并行高速處理能力的可編程邏輯器件被廣泛地應用到閥基電子設備中來[3,4]。

本文依托國家重大02專項,提出一種以FPGA為控制核心的閥基電子設備的研制方法,將傳統設備中處理器軟件完成的工作以硬件邏輯的形式實現,設計了一種同步性好、可靠性高、擴展能力強的新型閥基電子設備,提高了換流閥系統運行的穩定性。

1 換流閥觸發監控系統總體結構設計

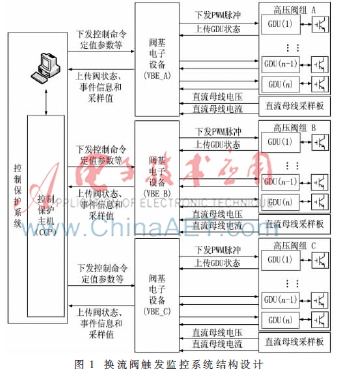

高壓大功率電壓源換流閥的子模塊比較多,采樣數據和觸發命令的實時性直接影響電壓源換流閥的控制性能,設計可靠高速的觸發監控系統非常重要。目前最常用的觸發監控系統方案是三級控制系統,包括控制保護系統、閥基電子設備和閥組驅動陣列。系統結構如圖1所示。

控制保護系統是換流閥觸發監控系統的控制核心,處于最上層,主要由PC上位機和控制保護主機CCP構成。上位機對整個系統進行監控,實現良好的人機界面,記錄和顯示試驗波形數據等功能;CCP完成整個系統的控制保護,主要工作包括一次電量的采集,控制算法的設計與實現,對整個系統運行狀態的檢測和保護,響應上位機的控制命令,并將系統電量上傳至上位機等。

閥基電子設備VBE是換流閥觸發和監控系統的重要部分,處于中間層,VBE系統承上啟下,接收上層CCP的控制要求,并通過光纖實時地下發觸發指令并監控下層閥組門極驅動單元GDU;同時也接收GDU側的狀態信息和直流電流電壓值,實時地進行分析處理,必要時下發保護關斷指令,并將狀態信息和電流電壓值上報給CCP[5]。VBE的數量可以根據應用需要進行配置,圖1系統所示每臺VBE裝置控制一相閥組,共需要3臺VBE裝置。

閥組門極驅動單元GDU是與一次側晶閘管或IGBT直接相連的驅動控制電路單元,負責接收VBE側的觸發指令,直接對晶閘管或IGBT執行PWM開關控制;同時采集電流、電壓、溫度等模擬量,實時判斷過流、過壓、過溫等狀態信息,并匯總上報給VBE側。

2 閥基電子設備的原理與設計

2.1 閥基電子設備系統結構設計

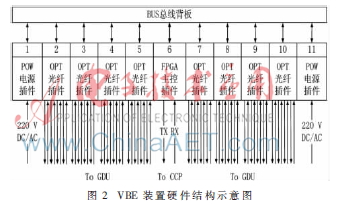

圖1所示,一般情況三相換流閥對應的VBE系統由3臺VBE裝置組成,每臺VBE可以實現對單相閥組上下橋臂多個晶閘管的獨立觸發監控。VBE裝置硬件結構如圖2所示,每臺裝置由主控插件(FPGA)、光纖插件(OPT)、電源插件(POW)、總線背板(BUS)4種板卡構成,裝置機箱尺寸大小為標準3U機箱,共11個卡槽。

FPGA主控插件是VBE的控制中心,它通過一對光纖與控制保護主機實現HDLC協議通信。一方面,主控插件接收CCP下行發出的對應相的控制命令,通過FPGA完成命令解析,PWM生成和調制編碼等邏輯處理流程,最終輸出PWM命令;另一方面,FPGA主控插件匯總由OPT光纖插件通過背板總線上傳的閥組狀態信息,檢測過流過溫等報警信號,將這些狀態信息通過光纖上報給CCP,必要時產生相應的中間層PWM保護動作命令。

OPT光纖插件是VBE與閥組驅動單元GDU的連接通道,每個OPT插件板配有4對收發光纖,可以控制4個GDU模塊,每臺VBE最多可以配置8塊插件,這樣最多可以控制32個GDU。OPT插件的主要工作是接收來自FPGA主控插件的PWM命令的差分電信號,將其轉換為光信號從光纖發出;同時接收GDU上送的狀態信息和告警信息光信號,將其轉換為差分電信號送給FPGA主控插件。

POW電源插件是VBE裝置的供電板卡,每個VBE配置兩塊相同的POW電源插件,安放在裝置的兩端,形成雙電源冗余備份供電,以此來提高裝置的運行穩定性。POW插件可以將外部的220 V交直流電經過開關電源的轉換輸出穩定的24 V直流電源,作為OPT插件和FPGA插件的工作電源。

BUS總線背板是VBE裝置的內部信號總線通道,主要是負責FPGA插件和OPT插件之間的星形總線通信,為保證信號傳輸的質量,背板為無源設計,總線信號都換轉為差分形式在背板傳輸,目前最大總線帶寬能達到50 Mb/s。

2.2 FPGA主控插件設計

2.2.1 硬件結構設計

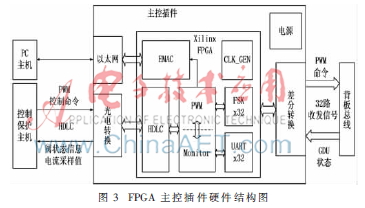

FPGA主控插件板卡主要包括一塊FPGA芯片、一對光電轉換器、以太網接口、差分驅動電路、與背板相連的高速接插件以及電源模塊等。其中FPGA選用Xilinx公司Spartan-6系列XC6SLX25-FTG256芯片,包含25 K的Logic Cells、936 Kb的Block RAM和186個用戶管腳等資源[6]。板卡的硬件結構設計如圖3所示。

2.2.2 軟件功能設計

軟件功能主要由FPGA程序執行完成,程序編寫采用Verilog HDL語言,片內的主要邏輯模塊如圖3所示,包括HDLC協議收發模塊、PWM脈沖控制器、GDU狀態監控模塊、FSK調制解調模塊、UART協議收發模塊、以太網MAC控制器以及時鐘復位模塊等。

HDLC協議收發器主要負責通過光口與上層CCP通信,通信協議采用高級數據鏈路控制HDLC協議,主要負責接收CCP下發的PWM控制命令報文,并實時解析獲取PWM的周期、占空比、死區時間、相位時延、開關使能等控制參數,同時匯總GDU監控模塊上送的閥組狀態及告警信息,組成數據報文上傳給CCP。點對點HDLC協議全雙工通信,數據報文透明傳輸,每幀數據均采用CRC校驗,并且在與CCP通信故障的情況下能立刻產生PWM關斷使能,保證了VBE與CCP之間報文傳輸的實時性和可靠性[7]。

PWM脈沖控制器接收邏輯解析得出的PWM的周期、占空比、死區時間、相位時延、開關使能等控制參數,通過計算和時序邏輯產生相應的上下橋臂互斥的PWM脈沖波形。GDU狀態監控模塊接收閥組中各路GDU上傳的狀態信息,主要包含光纖通斷狀態、工作模式、過流過溫等告警信息,并實時地反饋給PWM控制器作為保護邏輯判據,在中間層實現閥組過流過溫等情況下的快速保護功能。

傳統的VBE裝置一般都是將PWM脈沖直接以IO信號的方式通過光纖下發給閥組,以有光無光來表示PWM的打開和關閉,但當光纖通道出現問題或光電轉換器出現故障時,閥組側可能就會收到錯誤的PWM命令,從而導致閥組上晶閘管誤動作甚至器件燒毀;但如果以報文協議的形式下發PWM命令,由于解析報文需要多個時鐘周期,并且是異步時序邏輯,會給閥組上各晶閘管器件的PWM脈沖引入時延的不一致性,導致器件通斷不同步,也會導致閥組故障的產生。鑒于上述兩種命令下發方式的利弊,該VBE采用FSK頻率調制方式對PWM信號進行編碼后發送,也可以配置FPGA程序[8]使VBE采用IO信號或UART協議報文兩種方式發送PWM命令,作為與FSK方式對比的實驗方案。

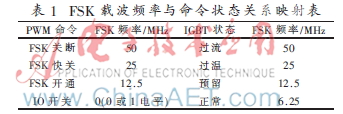

FSK調制解調模塊主要是將PWM信號進行頻率調制,利用載波的頻率變化來傳遞PWM的開關信息,這樣做的好處是可以區分PWM開通、正常關斷、故障關斷、無信號等多種控制命令,同樣接收不同頻率的載波也可以解析GDU正常運行、過流、過溫、光纖通信異常等多種狀態信息。FSK方式相比IO信號靈活很多,相比UART報文方式實時性要好,只是在調制解調過程中會引入極小的固定可預知延時。本VBE中采用的FSK載波頻率與命令狀態關系映射見表1。

3 運行實驗及結果分析

該VBE裝置用于10 kV電壓源型變換器(VSC)的逆變實驗。圖4是系統聯調過程的示波器波形截圖,其中通道1、2測量的是VBE與CCP之間通信的HDLC幀,通道3、4為GDU接收到VBE的FSK信號后解調產生的一對互斥的SPWM波形。

經過實驗測試,該VBE在CCP的管理下可以實現32路200 Hz~10 kHz的SPWM脈沖命令控制,占空比調節范圍在5%~95%,各路PWM信號之間的時延偏差能滿足應用要求,具體測試結果為:IO方式傳輸時延偏差在10 ns以內;FSK方式傳輸時延偏差在40 ns以內;UART協議傳輸時延偏差在100 ns左右,前兩者都在器件時延容忍范圍內。

4 結論

該VBE裝置以FPGA芯片為控制核心,通過其高效的并行處理技術,將傳統裝置中軟件程序實現的功能以電路邏輯硬件化實現,并采用FSK方式對PWM觸發脈沖進行編碼發送,使得裝置對換流閥的監控具有可靠性、可擴展性和高精度的同步一致性,滿足了實際工程的應用需求。

參考文獻

[1] 周亮,湯廣福,郝長城,等.換流閥閥基電子設備丟脈沖保護與控制的研究[J].電網技術,2011(7):222-226.

[2] 李宏.閥基電子設備的研究[J].科技成果管理與研究,2011(5):63-65.

[3] 鄭月賓,陳國聯,白云飛,等.一種冗余設計的直流輸電用閥基電子設備[J].電源學報,2012(9):63-66.

[4] 趙中原,邱毓昌,方志,等.現代HVDC換流閥設計特點及其技術動向[J].高電壓技術,2001,27(6):3-5.

[5] 袁清云.HVDC換流閥及其觸發與在線監測系統[M].北京:中國電力出版社,1999.

[6] Xilinx.Spartan-6 family overview datasheet[Z].DS160.Xilinx,June 24,2009.

[7] 徐建松,姚曉明,駱健,等.HDLC協議在閥基控制通信中的應用[J].電子技術應用,2014,40(6):23-26.

[8] 解婷,鄭健超,湯廣福.部分重配置技術用于智能電網換流閥控制系統[J].高電壓技術,2011,37(3):700-705.