摘 要: USB3.0幀同步電路設計的關鍵在于高速率下串行數據流的幀定位與數據對齊,需同時兼顧高效率和低功耗。使用Verilog HDL描述語言設計了一種基于多相位和并行檢測技術的幀同步電路,重點對并行檢測電路進行分析和優化。該電路在ISE中編譯和仿真,結合數據進行分析,并將仿真結果進行比較驗證,證明該電路能滿足幀同步的速率和時序要求。

關鍵詞: USB3.0;多相位技術;并行檢測;幀同步;Verilog HDL

0 引言

近年來,USB(通用串行總線)作為一種標準的傳輸接口[1],應用十分廣泛。從2008年11月首次發布USB3.0規范以來,在快速存儲、大數據高速傳輸等領域都出現了USB3.0[2]的身影,延續USB2.0時代的輝煌,繼續展現出強大的競爭力。與USB2.0高速版本的設計[3]相比,USB3.0的復雜度大大增加,尤其是5 Gb/s的差分傳輸速率成為設計者重點考慮的問題之一。高速率、低功耗是當前芯片設計的主流趨勢,在提高器件工作頻率的情況下,更需要有效地控制功耗。本文將介紹多相位技術在USB3.0幀同步系統設計中的應用,通過對并行檢測電路的優化,實現系統復雜度、實用性以及功耗方面的平衡。

1 接收電路的功能與分析

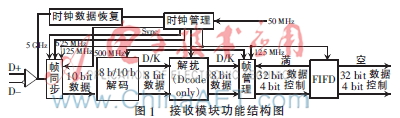

USB3.0接收部分的功能結構如圖1所示。

為了抑制共模干擾,USB3.0的數據采用差分輸入,經過雙端轉單端電路,分為兩路送入時鐘數據恢復(Clock Data Recovery,CDR)模塊和串轉并模塊。

CDR模塊完成從串行數據流中提取時鐘信號的功能,送至時鐘管理模塊,得到625 MHz、500 MHz和125 MHz時鐘信號供其他模塊使用。

幀同步模塊完成對高速串行數據流的并行低速化,通過并行檢測幀定界符得到幀同步信號,同時控制時鐘管理模塊的時鐘輸出,完成數據的對齊處理,經過彈性緩沖模塊得到500 MHz、10 bit的并行數據流。

幀同步模塊輸出的并行數據流先后通過8 b/10 b解碼模塊、解擾模塊得到500 MHz、8 bit數據流與控制信號;通過位寬拼接處理最終得到125 MHz、36 bit的數據流(其中包含32 bit數據和4 bit控制位)寫入數據FIFO,供LINK層讀取使用。

2 幀同步模塊的設計及要點

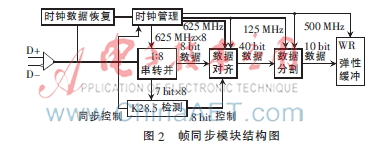

幀同步模塊是接收模塊的難點,主要由以下功能模塊組成:多相位串轉并模塊、并行幀定界符檢測模塊、并行數據流對齊模塊、彈性緩沖模塊。各大模塊及相關時鐘結構電路如圖2所示。其中,串轉并模塊和并行檢測模塊是本設計的優化重點。電路選用XLINX公司的Virtex-5芯片作為設計與測試平臺。

2.1 基于多相位技術的串轉并模塊設計

傳統的低速串轉并電路采用移位寄存器實現,電路的功耗與工作時鐘成線性關系。USB3.0的輸入信號高達5 Gb/s,移位寄存器產生的功耗很大,并且工藝要求很高,而0.15 m CMOS工藝條件只能達到3.0 Gb/s的頻率,繼續提升工作頻率極易引起電路的不穩定。因此,有效地降低器件工作時鐘頻率,在降低器件功耗和降低生產工藝要求方面具有重要意義,同時對相同工藝下提升器件的性能也非常有效。

多相位技術的原理為:利用PLL將CDR恢復得到的f頻率時鐘分成多個頻率為f/N,彼此相位間隔為360°/N的時鐘信號,利用這N個時鐘對串行數據流進行分時采樣,在相移為0°的f/N頻率時鐘同步下,合并為N bit的數據。這種技術的優勢在于:在不增加原有功能復雜度的情況下,利用PLL降低CMOS器件的運行時鐘,從而降低功耗。PLL的引入,能夠一定程度上改善恢復時鐘的抖動。在PLL設計中,當分頻值N取2的冪次方時,可有效簡化設計,在此N取2^3=8。

使用Verilog HDL[4]語言對1:8多相位串轉并模塊進行描述,部分關鍵代碼為:

always@(posedge clk_XXX or negedge rstn)begin

if(!rstn)pdata[n]<=1′b0;

else pdata[n]<=sdata_i;

end

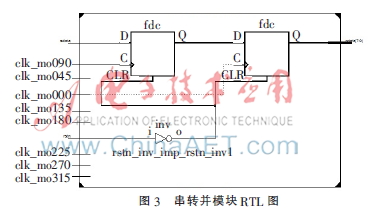

其中clk_XXX代表clk_000~clk_315這8個相位間隔為45°的時鐘。采樣得到的數據以8 bit為單位送入并行檢測模塊。

經過ISE綜合后模塊非常簡潔,RTL電路如圖3所示。

2.2 優化并行幀定界符檢測模塊設計

根據USB3.0規范,傳輸的數據采用控制碼K28.5作為幀定界符。它的特殊性在于:在所有選定使用的控制碼與數據碼中,有且只有K28.5存在5個連續的高電平信號‘1’。因此,許多采用8 b/10 b編碼的傳輸系統都將其作為幀定界符。在傳輸的數據流中,檢測到“001111010”就可以判定新一幀的開始。

USB3.0發送部分的數據經過8 b/10 b編碼后,數據塊由8 bit為單位轉換為10 bit為單位,常用的做法為:接收端在f/10的工作時鐘驅動下,并行檢測10個相鄰位置的10 bit數據。通過并行的方式,從而降低電路的運行速度要求,實際是以空間換時間的思想。雖然電路工作頻率降低,但整體功耗因電路規模的相應增大而沒有減小。

通過對并行檢測電路的分析可以發現:假定串轉并模塊采用1:N結構,并行檢測模塊對M bit數據塊進行檢測,檢測單元的規模為N×M bit。在并行度M bit相同條件下,N越大,需要的邏輯運算單元就越多。串轉并模塊選擇1:8的比例,不僅可以簡化PLL設計,同時也能降低邏輯運算單元的消耗。

其次,減少檢測數據塊的并行度M也是重要途徑。根據K28.5的特點,在數據正確傳輸的前提下只需檢測其中7 bit,即“0011111”或者“1111101”[5]就能判定為K28.5碼。取M=7 bit,則只需要8×7=56 bit邏輯運算單元,相比未優化前的10×10=100 bit邏輯運算單元減少44%,簡化了電路的結構,能夠一定程度地提升器件的運行效率。

2.3 并行數據流對齊模塊設計

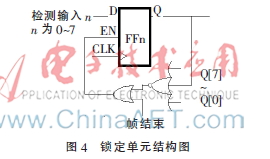

并行檢測模塊檢測到幀定界符后,需通過鎖定單元[6]鎖定當前的數據流分塊方式,鎖定單元結構設計如圖4所示。

鎖定機構的工作原理為:當某一檢測單元成功檢測到幀定界符K28.5的前7 bit,便可推斷數據流3 bit后即為實際所需數據流的起始位置,鎖定單元在下一時鐘沿鎖定當前檢測結果不再更改,并根據鎖定的結果在對應位置每次取出10 bit并行數據送至下級電路,直到檢測到當前幀結束或者復位解除鎖定。

鎖定單元關鍵代碼如下所示:

wire comma_detect[n]=detect_data_X==7′b1111100;

always@(posedge clk or negedge rstn)begin

if(!rstn)

comma_lock[n]<=1′b0;

else if((!(|comma_lock[7:0]))|fram_end)

comma_lock[n]<=comma_detect[n];

else

comma_lock[n]<=comma_lock[n];

end

其中,n為0~7,detect_data_X表示第0~7個檢測單元。

由于串轉并模塊輸出為8 bit并行數據,根據USB3.0規范,實際送入彈性緩沖須為10 bit,因此需要使用位寬轉換電路對數據流位寬進行轉換。方法為:將8 bit位寬拼接成40 bit位寬,通過判斷鎖定單元輸出的comma_lock信號,重新選取對齊后的40 bit,最后分割成實際需要的10 bit位寬輸出。

3 仿真及驗證

編寫test bench,改變串行數據流中K28.5的位置,模擬發送數據幀,在ISim中對設計的電路進行仿真驗證,仿真波形如圖5所示。

經過8組不同位置數據(在此只貼出2個結果)的對比可以看出,在不同的數據流中,幀定界符K28.5的位置總能夠被正確檢測,通過數據對齊模塊后成功分離出后續模塊所需10 bit并行數據,結果完全正確,且滿足運行500 MHz的運行速度要求。

4 結論

多相位技術能夠顯著降低器件的工作頻率,從而減少功耗,同時也可以降低制造器件的工藝難度;并行處理技術是當前高速電路發展的趨勢,合理地利用編碼自身特點,進行針對性的優化,能夠使電路更加簡潔,運行速度更快。這兩者對于提高器件的性能而言,都具有十分重要的現實意義。

參考文獻

[1] Don Anderson Dave Dzatko.USB系統體系(第二版)[M].北京:中國電力出版社,2003.

[2] Hewlett-Packard Company, Intel, et al. Universal serial bus 3.0 specification Revision1.0[R]. USA: Hewlett-Packard Company. 2008.

[3] 王永,白雪飛,方毅,等.基于UTMI協議的USB2.0收發器邏輯電路設計[J].微型機與應用,2014,33(10):13-15,19.

[4] 夏字聞.Verilog數字系統設計(第二版)[M].北京:北京航空航天大學出版社,2008.

[5] 楊卿.RapidIO高速互聯接口的設計研究與應用[D].成都:電子科技大學,2009.

[6] 劉昭,金德鵬,曾烈光.基于連續性判別的并行幀同步系統[J].電子學報,2005,33(7):1177-1182.