徐成強, 何小海, 卿粼波, 吳小強

(四川大學 電子信息學院 圖像信息研究所,四川 成都 610065)

摘要:設計并實現了一種基于FPGA硬件平臺的Bayer到RGB格式圖像數據轉換實時采集顯示系統。該系統能夠對前端Camera Link接口的CMOS相機采集的分辨率為1 920×1 080、幀率100 f/s以上的Bayer格式圖像進行實時處理,并且將處理得到的RGB彩色圖像數據通過DVI顯示器以60 f/s的幀率實時顯示。根據FPGA并行處理能力強的特點,采用像素矩陣模板實現了Bayer到RGB的彩色圖像插值算法,實現了高分辨率、高幀率彩色圖像的實時采集顯示。

關鍵詞:FPGA;Bayer濾波;DVI顯示;Camera Link

0引言

中央高校基本科研業務費(2015SCU04A11)高分辨率、高幀率圖像的實時處理在軍事、通信、航天航空、醫學等領域有著越來越廣泛的應用[1],RGB彩色圖像是計算機、攝像機等設備最常采用的色彩空間,并且彩色圖像更有利于進行觀察與分析。在圖像的實時處理過程中,圖像數據量大,要求的運算速率高[2],因此選用善于高速并行處理大量數據的FPGA作為處理器是非常合適的。本文選用自主設計的以Xilinx公司Virtex5系列的xc5vfx70t芯片為核心的14層硬件平臺。xc5vfx70t的最高運行頻率為550 MHz,片內時鐘、slice、存儲等可用資源非常豐富,因此用于實現分辨率為1 920×1 080、幀率為100 f/s以上的Bayer到RGB彩色圖像轉換的實時采集顯示是非常適合的。根據Bayer格式圖像中R、G、B分量與鄰近像素的R、G、B分量存在高度相關性的特點[3],本文設計的彩色圖像轉換算法是基于像素矩陣模板的插值算法,能夠很好地實現彩色圖像的恢復。

1CMOS圖像傳感器

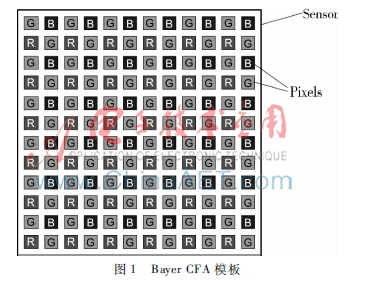

出于對成本及體積的考慮,目前大部分數字圖像采集系統都是采用一塊CCD/CMOS來作為接收圖像的傳感器,在傳感器表面會覆蓋CFA(Color Filter Array)顏色濾波矩陣以得到每個感光單元的分量灰度值[4]。基于FPGA的彩色圖像采集顯示系統一般由系統采集前端、FPGA內部各處理模塊以及顯示三個部分組成。本系統前端采用的CMOS相機為Basler公司的acA2000340kc,該相機支持的最大分辨率為2 046×1 086,最大幀率為340 f/s,其成像CFA模板如圖1所示。acA2000340kc為Camera Link接口,支持三種配置模式即Base、Medium和Full,三種模式的最大數據帶寬分別為255 MB/s、510 MB/s、680 MB/s[5],本文選用的是Full傳輸模式。

2Bayer插值算法

實現Bayer到RGB圖像格式轉換的算法有很多,比如鄰域插值法、線性插值法[67]、神經網絡插值法等,好的插值方法對高質量圖像的獲取非常重要。一般而言,選用的方法越復雜,產生的圖像質量越高,但是同時也需要付出更大的處理時間代價,在硬件中的實現也更困難。因此在處理速度與成像質量之間找到一種平衡是非常有必要的。文獻[3]采用的是基于自適應的局部去馬賽克算法,雖然處理效果好,但是算法復雜,難以在FPGA中實時實現;文獻[4]中采用的是基于像素矩陣模板的插值算法,處理圖像的分辨率為1 280×1 024;文獻[6]中采用的是基于像素矩陣模板的插值算法,能夠基本保證實時地處理分辨率為1 280×1 024的圖像。綜合考慮以上情況,本文采用基于像素矩陣模板的線性插值法,該方法運算量小,成像質量良好,易于在FPGA中實現。

由圖1可知Bayer CFA模板中可能出現的3×3像素矩陣有4種情況,如圖2所示,其中(a)和(b)的中心像素點為G分量,(c)為R分量,(d)為B分量。本文針對不同情況下的像素矩陣,具體設計了不同的插值方法。

2.1中心像素為G分量

中心像素為G分量的包含圖2中的(a)和(b)兩種情況。在這里為了方便說明,以(a)為例,用Glu、Gld、Gru、Grd分別代表左上、左下、右上、右下的4個G值,左右兩邊的R值用Rl和Rr表示,上下方向的兩個B值用Bu和Bd表示,當前中心點的G值為Gc,對中心點Gc進行插值之后得到的三個分量的值就用R、G、B來表示,之后的(b)、(c)、(d)中的像素點命名方式與此類似。本文在考慮了3×3像素矩陣相鄰像素之間的影響之后,針對圖(a)所示的情況,改進設計的插值方法如下:

G=1/2Gc+1/8(Glu+Gld+Gru+Grd)(1)

R=1/2Rl+1/2Rr(2)

B=1/2Bu+1/2Bd(3)

(b)與(a)的區別僅在于R和B分量的像素點位置剛好相反,改進方法與(a)的情況類似,這里就不再贅述。

2.2中心像素為R(B)分量

以圖2中的(c)為例進行說明,插值的方法如下:

G=1/4(Gu+Gd+Gl+Gr)(4)

R=1/4(Rlu+Rld+Rru+Rrd)(5)

B=Bc(6)

(d)和(c)的區別也僅在于R和B分量的像素點位置剛好相反,改進方法與(c)的類似,這里也不再贅述。

3FPGA硬件設計與實現

3.1硬件系統結構

本文綜合考慮所用FPGA的資源實現Bayer到RGB圖像轉換的硬件系統整體架構如圖3所示。系統前端由Camera Link相機將采集的視頻數據傳送至三片DS90CR288A進行差分信號的轉換,轉換后的64 bit RGB單色數據傳送至FPGA,FPGA利用兩組DDR2對圖像數據進行緩存、處理,最后控制DVI顯示芯片CH7301C進行實時顯示。

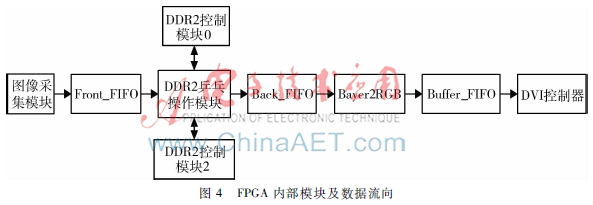

FPGA內部首先通過圖像采集模塊將圖像傳送至Front_FIFO中,然后由乒乓操作模塊將Front_FIFO中的數據讀出進行乒乓操作處理后暫存在DDR2中,實現前后速度的匹配,再將數據輸出至Back_FIFO中。Bayer2RGB模塊讀取Back_FIFO中的數據進行處理之后將生成的RGB彩色圖像數據傳送至Buffer_FIFO中,最后由DVI顯示模塊將數據讀出以進行顯示。FPGA內部各模塊及其數據流向如圖4所示。

3.2Bayer2RGB模塊

Bayer2RGB模塊的內部結構框圖如圖5所示,由Back_FIFO輸出的8 bit位寬的圖像數據shiftin首先傳送到一個三行線性移位寄存器組進行緩存,同時shiftin會進入一個行、列計算模塊對圖像的行、列進行計數,由row_cnt和col_cnt兩個變量輸出。由于本文的算法是基于像素矩陣塊的,因此在緩存完三行完整的圖像數據后才能夠開始進行Bayer到RGB的圖像插值算法處理。圖4FPGA內部模塊及數據流向

三行移位寄存器組的結構如圖6所示,輸入數據shiftin在時鐘上升沿傳送給line1[0],同時line1、line2和line3均要進行線性移位,line1[1919]移至line2[0],同樣地,line2[1919]移至line3[0],系統每次取出圖6中虛線框內的像素矩陣塊與行、列計算模塊的row_cnt和col_cnt一起傳送至插值算法模塊進行處理。

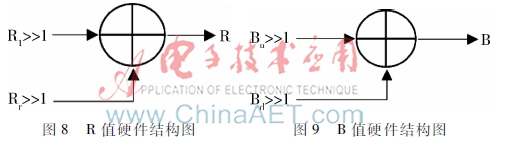

插值算法模塊根據中心點即line2[1918]的行、列值奇偶情況來選擇相應的運算處理,總共有4種情況,分別對應圖2所示的四種情況。本系統使用移位運算和加法運算對每種情況的插值算法設計了相應的硬件實圖7G值硬件結構圖現結構,這里以圖2中的(a)為例,硬件結構如圖7、8、9所示,分別對應公式(1)、(2)、(3)。

本文最終的實驗測試結果如圖10所示,圖(a)為整個系統的整體成像圖,圖(b)為Bayer2RGB模塊處理后的彩色圖像,圖(c)為實物圖,對比可知系統的實時彩色還原效果良好。

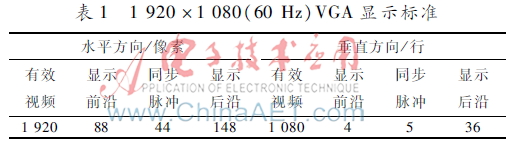

系統前端Camera Link接口的CMOS相機采集幀率為120 f/s,分辨率為1 920×1 080,DVI顯示幀率最大為60 f/s,視頻電子標準協會VESA制

定的顯示分辨率標準如表1所示,根據表中的數據可以計算出顯示時鐘頻率=2 200 (clk)1125(h)60(f/s)=148.5 MHz。

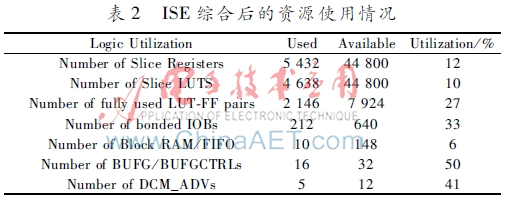

由于Bayer2RGB模塊需要緩存3行數據,處理時鐘與DVI時鐘頻率一致為148.5 MHz,因此可以通過公式(7)粗略算出總延時t約為38.8 ns,完全實現了真正的高分辨率高幀率實時彩色圖像采集顯示。由本文算法可知采用FPGA的并行流水線結構,運算速度快,時延小,完全可以對分辨率更高的視頻數據進行實時彩色圖像的采集顯示。本系統在Xilinx的FPGA開發工具ISE 10.1下綜合之后的資源使用情況如表2所示,本系統僅消耗了xc5vfx70t中12%的slice資源,6%的Block RAM資源。

![]()

5結論

本文利用FPGA邏輯資源豐富、并行處理能力強等特點,實現了高分辨率高幀率的實時彩色圖像采集顯示。FPGA現在發展越來越快,片內可用資源越來越豐富,不但可以很方便地實現系統前端的高分辨率高幀率的視頻采集,并且還能對圖像進行算法處理。本文提出的Bayer到RGB圖像轉換算法簡單,易于在FPGA中實現,移植性好,如果需要將本系統移植至其他FPGA硬件平臺,只要該FPGA的邏輯資源滿足表2中的資源需求,修改相應的管腳配置即可。本系統體積小、性能穩定、便于攜帶,目前已經穩定地應用在實驗室相關的研究項目中,具有較強的工程應用價值。

參考文獻

[1] 滕偉, 安博文. 基于 FPGA+ DSP 技術的 Bayer 格式圖像預處理[J]. 電子設計工程, 2010 (10): 145147.

[2] MA H, LIU S, ZHOU J, et al. The FPGA realization of a realtime Bayer image restoration algorithm with better performance[C].International Symposium on Optoelectronic Technology and Application 2014. International Society for Optics and Photonics, 2014: 93010C93010C4.

[3] TIAN Q, YANG X, ZHANG L, et al. Image reconstruction research on color filter array[J]. Procedia Engineering, 2012, 29(4): 22042208.