李傳輝,劉純武,黃芝平

(國防科學技術大學 機電工程與自動化學院,湖南 長沙 410073)

摘要:在100G以太網媒體接入控制器(Media Access Control,MAC)的設計中,需要采用高位寬的并行數據來降低對時鐘的要求。在使用并行循環冗余校驗(Cyclical Redundancy Check,CRC)時會有一個問題,即需要計算CRC的數據域長度不一定是數據通道位寬的整數倍,導致最后一組數據無法使用數據通道的位寬對其進行CRC計算。為了解決這個問題,本文提出了在幀前填充0的處理方法。仿真和測試結果都驗證了該方法的可行性。該處理方法也能應用到其他的通信系統中。

關鍵詞:100G以太網;并行CRC;高位寬

0引言

IEEE在2010年發布了40/100G以太網標準[1],其中MAC層仍然沿用以前的規定未作大的改變,只是100 Gb/s的高速率使得無法沿用以前的方法完成CRC值的計算,為此,本文提出了一種簡單有效的解決方法。

1循環冗余校驗

在數字通信系統中,為了確保接收到的數據與發送端的數據一致,需要引入差錯控制機制。循環冗余校驗碼由于其誤碼監測能力強,抗干擾能力優異,被廣泛應用于線路檢錯。循環冗余檢驗是一種系統的縮短循環碼,它采用多項式編碼方法[2]。設被檢驗的信息碼有n位,信息系列M={mn-1 mn-2…m0},用多項式M(x)可表示為:

M(x) = mn-1 xn-1 + mn-2 xn-2 + … + m1x1 +m0x0(1)

發送方和接收方使用同一個生成多項式G(x),其是一個k階的二進制多項式,而且G(x)的首位和最后一位的系數都必須是1,其通用表達式為:

G(x)=xk+gk-1xk-1+gk-2xk-2+…+g1x+1(2)

CRC的計算規則為發送方以xk·M(x)除以生成多項式G(x),將得到的余數R(x)作為校驗值,這里的計算規則都是使用二進制運算規則,R(x)可表示為:

R(x)=CRC(M(x))= xk·M(x)mod G(x)(3)

發送方將CRC值隨數據一起發送給接收方,接收方對接收到的數據進行CRC值的計算,并將它與發送方的CRC值進行比較。如果數據傳輸過程中沒有錯誤,兩者的校驗值就會是一致的,相反如果得到的校驗值不一致,就可以判斷出數據在傳輸過程中發生了錯誤,這時接收方就可以丟棄當前數據或要求發送方重傳數據。CRC校驗可以百分百地檢測出所有的奇數個的隨機錯誤和長度小于等于k的突發錯誤。

2100G以太網的CRC設計

在以太網通信中,CRC校驗具有重要作用。依據IEEE802.3以太網的幀格式(如圖1所示),CRC計算的數據區域包括目的地址、原地址、長度/類型和負載數據圖1以太網幀格式區域。得到的CRC值作為幀校驗序列(Frame Check Sequence,FCS)填充在數據幀尾。其中規定了以太網幀FCS字段的生成算法為CRC32,其生成的多項式表達式為:

G(x)=x32+x26+x22+x16+x12+x11+x10+x8+x7+x5+x4+x2+x+1(4)

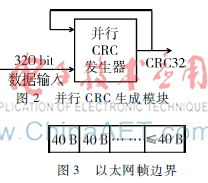

在吉比特以上速率的通信系統中,傳統的串行CRC校驗方法已無法滿足要求,所以現在有很多新型并行CRC計算方法[35]。因此在100G以太網中,其CRC也必須采用并行方法,CRC計算的并行位寬就是數據通道的位寬。提高數據位寬可以降低系統的時鐘頻率,但另一方面隨著并行數據位寬的增加會使得CRC電路的延遲時間增加,影響系統的時序性能。經過綜合考慮本文中設計的數據并行位寬為320。

使用320位的高并行位寬會使得數據的處理變得復雜。比如在MAC層的發送方,上層客戶每個時鐘就會有一組320位40 B的數據送給MAC處理,CRC模塊就會使用320位的并行算法對其計算。當前的CRC值只與上一次數據得到的CRC值及當前的數據有關,CRC值初始化為全0,如圖2所示。

問題是數據并不一定是40 B的整數倍關系,最后一組數據可能結束于任意位置,如圖3所示。

在10G以太網中,數據位寬為64 bit,在參考文獻[6]中對這種情況的處理方法為同時設計從8 bit到64 bit的CRC生成模塊,根據有效字節數選擇使用其中一個。這一方法無疑會占用大量資源,而且利用率低。在100G以太網中數據位寬如果按320設計,需要多達40個不同的CRC模塊,加上一個40路的多選一電路,這樣的電路在資源使用和時序性能方面都是很糟糕的。所以這一方法無法用于100G以太網中。文獻[7]中提到了一種級聯結構可以計算任意字節的CRC,但此結構有個很明顯的缺點,即級聯越大,電路延遲線性增加,320位就需要級聯40次,這樣的電路無法滿足時序要求。文獻[2]中利用了CRC校驗具有的Magic Number特性,在數據幀后面添加0,使得可以只用一個64 bit的CRC模塊完成接收方的CRC校驗,但無法在數據發送方完成CRC值的計算。

3幀前補0的并行CRC

上節提到的10G以太網CRC的處理方法都無法直接應用于100G以太網中。下面說明本文提出的方法:幀前補0后再進行CRC計算。

假設原始序列M有n位數據,n不是320位的整數倍。i是一個小于320的整數,且i+n為320的整數倍,在M前增加i個0構造為新序列M′:

M′(x)=0·xi+n-1+…+0·xn+M(x)=0+M(x)=M(x)(5)

可以看出新序列在數值上與原來的序列值是一樣的。這個很好理解,就像在十進制中在最前面添加任意位數的0并不會改變這個數的數值一樣,當然這在二進制數當中同樣適用。新序列的數據長度成為了320的整數倍。

由CRC的計算公式(3)來看,CRC的結果只與序列的數值有關,所以用新序列計算CRC會得到與用原始數列同樣的結果。所以依據此原理,只需要設計一個320位的并行CRC模塊,計算時使用新的序列送給CRC模塊,這個方法可以計算任意字節數據幀的CRC值。

假設有一幀數據負載字節長度為len,加上目的地址、源地址和數據/類型字段的長度14 B,則該幀需要參與CRC計算的數據總長為L=len+14。令n=ceil(L/40),ceil函數得到的是大于等于L/40的最小整數。令rem=mod(L,40)為L/40的余數,表示最后一組數據中有效數據的字節數,對應的com=40-rem表示無效的字節數,V=8*com則表示無效的比特數,也就是需要在幀前添加的0的比特個數。

在客戶端向MAC發送數據時,每個時鐘MAC層會收到一組數據Cur_data_in[319:0],設計一組初始化為全0的寄存器Last_data_in[319:0]用來保存上一時鐘的數據。根據V值的大小將Cur_data_in和Last_data_in組合成一組新的數據Data_to_crc[319:0],其組合關系為:

Data_to_crc[319:0]=Last_data_in[V-1:0]&Cur_data_in[319:V](6)

“&”表示并置連接,處理過程如圖4所示。新的序列就是送給CRC模塊的數據,從圖中可以看到在原始數據的前面添加了V個比特0。每組數據都可以使用320位的并行CRC進行處理,而且最后得到的結果與使用原始數據一樣。

4測試及分析

使用硬件描述語言VHDL實現上述的處理過程,并將程序下載到FPGA中進行測試,綜合出來的結果表明該方法在面積使用和運行速度方面的效果都很好。測試時客戶端給出了一些不同長度的以太網幀,使用Quartus II中的SignalTap工具對數據流進行采樣。圖5是rem值為18的一幀數據的第一組數據,可以看到data_to_crc在cur_data_in前面添加了22個比特0,這是符合設計預期結果的。圖6所示是該幀數據的最后一組數據,根據rem值,cur_data_in只有18 B的有效數據,所以data_to_crc也只取了其中的18 B有效數據,在CC處結束,此時的CRC值就是最終的FCS值為83ACF5C1。

為了驗證該值的正確性,使用8位并行CRC算法計算該幀的CRC值,在ModelSim平臺下進行了仿真。結果如圖7所示,可以看到計算完CC后CRC值為83ACF5C1,與前面的結果一致,說明了該方法得到的結果是正確的。

5結束語

由于100G以太網中會使用很高的并行數據位寬,但是數據幀中需要進行CRC計算的數據長度不一定是位寬的整數倍,本文針對這個問題提出了一種新的處理方法,并且通過了測試。該方法簡單有效,能夠克服傳統方法的缺陷,在性能上有很大的提升。雖然本文是以100G以太網的CRC32作說明,該方法也能很容易地應用于其他的高速通信系統。

參考文獻

[1] IEEE. IEEE Std. 802.3ba[S]. 2010.

[2] 彭建輝. 10G以太網接口并行CRC校驗的一種簡化算法[J].微計算機信息,2006,22(20):213215.

[3] STAVINOV E.A practical parallel CRC generation method [J]. Circuit Cellar, 2010(234):3845.

[4] 畢占坤,張羿猛,黃芝平,等.基于邏輯設計的高速CRC并行算法研究及其FPGA實現[J]. 儀器儀表學報, 2007,28(12):22442249.

[5] KENNEDY C E, MOZAFFARIKERMANI M.Generalized parallel CRC computation on FPGA[C]. Canadian Conference on Electrical and Computer Engineering (CCECE), 2015:107113.

[6] 張友亮,劉志軍,馬成海,等. 萬兆以太網MAC層控制器的FPGA設計與實現[J]. 計算機工程與應用, 2012,48(6):7779.

[7] 劉昭,蘇厲,金德鵬,等.10G以太網系統中的并行CRC編解碼器的設計[J]. 電子技術應用, 2004,30(4):4750.