王慧英1,曹志鋒2

(1.吉首大學(xué) 張家界學(xué)院,湖南 張家界 427000;2.國(guó)防科技大學(xué) 機(jī)電工程與自動(dòng)化學(xué)院儀器系,湖南 長(zhǎng)沙 410004)

摘要:設(shè)計(jì)了一個(gè)基于PCI-E總線的高速光纖數(shù)據(jù)采集系統(tǒng)。對(duì)高速光纖數(shù)據(jù)的處理、傳輸、存儲(chǔ)和WDM驅(qū)動(dòng)程序的開(kāi)發(fā)做了論述。經(jīng)測(cè)試表明,該系統(tǒng)能夠?qū)μ幚砗蟮?路2.5 Gb/s SDH光纖信號(hào)連續(xù)采集近3小時(shí)不丟幀,采集的數(shù)據(jù)量達(dá)6 TB,穩(wěn)定的存盤速率高達(dá)600 MB/s,具有很好的應(yīng)用價(jià)值。

關(guān)鍵詞:PCI-Express總線;高速采集;光纖數(shù)據(jù);磁盤陣列;DMA

0引言

高速采集系統(tǒng)中的數(shù)據(jù)具有數(shù)據(jù)速率高、數(shù)據(jù)量大的特點(diǎn),要對(duì)高速數(shù)據(jù)進(jìn)行實(shí)時(shí)長(zhǎng)時(shí)間存儲(chǔ),必須克服高速數(shù)據(jù)的傳輸與存儲(chǔ)的技術(shù)難題。本設(shè)計(jì)采用PCI Express總線技術(shù)對(duì)高速數(shù)據(jù)進(jìn)行傳輸,用高速磁盤陣列技術(shù)對(duì)高速數(shù)據(jù)進(jìn)行存儲(chǔ)。

PCI Express[12],簡(jiǎn)稱PCIE,是用來(lái)互聯(lián)諸如計(jì)算機(jī)和通信平臺(tái)應(yīng)用中外圍設(shè)備的第三代I/O總線。PCIE總線每個(gè)通道的單向速率不低于2.5 Gb/s,可以根據(jù)用戶的需要靈活配置成x1、x4、x8、x16的工作模式。

冗余磁盤陣列[3],簡(jiǎn)稱RAID,是一種由多塊廉價(jià)磁盤構(gòu)成的冗余陣列,主要由陣列控制卡和多個(gè)硬盤組成。數(shù)據(jù)分布在陣列的各個(gè)磁盤中, 磁盤數(shù)據(jù)的讀寫由多個(gè)磁盤并行完成,非常適用于高速大容量數(shù)據(jù)的存取。

1系統(tǒng)總體設(shè)計(jì)概述

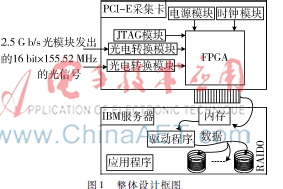

本高速采集系統(tǒng)由PCIE采集卡、上位機(jī)、PCIE驅(qū)動(dòng)和應(yīng)用程序組成,如圖1所示。PCIE采集卡以FPGA為核心,F(xiàn)PGA外圍有光電轉(zhuǎn)換模塊、電源模塊、時(shí)鐘模塊和JTAG模塊。

FPGA用于對(duì)高速數(shù)據(jù)的處理和PCI-E總線的控制,電源模塊為FPGA和光電轉(zhuǎn)換模塊供電,時(shí)鐘模塊為FPGA提供高精度的差分(LVDS)時(shí)鐘信號(hào),JTAG模塊用于FPGA的調(diào)試和程序下載。

驅(qū)動(dòng)程序負(fù)責(zé)把上位機(jī)數(shù)據(jù)緩存區(qū)內(nèi)的數(shù)據(jù)搬運(yùn)到磁盤陣列中,并對(duì)FPGA中的DMA寄存器賦初值[4];應(yīng)用程序用于人機(jī)交互,控制PCIE采集卡的采集與停止,并提供一些相關(guān)的狀態(tài)信息。

2PCI-E采集卡設(shè)計(jì)

PCI-E采集卡用于對(duì)高速光纖數(shù)據(jù)的處理和傳輸。

2.1硬件構(gòu)成及性能分析

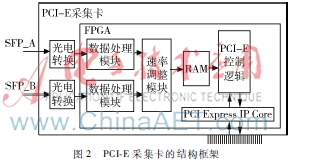

本設(shè)計(jì)選用Altera公司的Stratix II GX系列EP2SGX90FF1508C3N芯片來(lái)實(shí)現(xiàn)PCIE總線功能,并用其對(duì)數(shù)據(jù)進(jìn)行處理。該芯片內(nèi)部有4 520 448 bit的RAM資源,16對(duì)處理速度高達(dá)6.375 Gb/s的Transceiver通道,片內(nèi)的PCIE IP核(軟核)支持PCIE 1.0a和1.1規(guī)范,通道可配置成x1、x4或x8的類型。在本設(shè)計(jì)中,把PCIE的IP配置成x4模式。x4 IP除去8b/10b編碼的開(kāi)銷,有效數(shù)據(jù)帶寬為8 Gb/s,可以滿足接入2路2.5 Gb/s信號(hào)的傳輸。PCIE采集卡的光電轉(zhuǎn)換模塊選用武漢電信器件公司的RTXM192450,該器件的速率為2.488 32 Gb/s,輸出的信號(hào)可直接給FPGA處理。PCIE采集卡的結(jié)構(gòu)框架如圖2所示。

2.2數(shù)據(jù)處理機(jī)制

SDH信號(hào)[5]的一幀數(shù)據(jù)有9行270×N列,共9×270×N字節(jié),大體分為3個(gè)主要的區(qū)域:段開(kāi)銷(SOH),管理單元指針(AU PTR)和凈荷區(qū)域。其中段開(kāi)銷又可分為再生段開(kāi)銷(RSOH)和復(fù)用段開(kāi)銷(MSOH)。圖3為STM-N的幀結(jié)構(gòu)。

在本設(shè)計(jì)中,接入的SDH信號(hào)為STM16,且只對(duì)其凈荷進(jìn)行存盤。故接入的信號(hào)要進(jìn)行幀同步、解擾(解擾多項(xiàng)式為x7+x6+1)、凈荷提取等處理。

為了使采集卡能適應(yīng)2路不同源SDH信號(hào)的輸入,還需對(duì)接入的信號(hào)進(jìn)行速率調(diào)整。速率調(diào)整機(jī)制為:在片內(nèi)開(kāi)2個(gè)位寬為64 bit、容量為64 KB的FIFO,分別命名為FIFO_A、FIFO_B,F(xiàn)IFO_A和FIFO_B分別用于緩存SFP_A和SFP_B的接入數(shù)據(jù),當(dāng)有FIFO半滿時(shí),交替地從2個(gè)輸出位寬為64 bit的FIFO中讀出32 KB的數(shù)據(jù),另外加入64 bit的線路標(biāo)識(shí),以便存盤時(shí)進(jìn)行數(shù)據(jù)分離,這樣向RAM寫一次的數(shù)據(jù)量就為32 KB。

2.3DMA傳輸機(jī)制

對(duì)于高速數(shù)據(jù)流, 必須用DMA傳輸方式才能保證數(shù)據(jù)在采集卡和上位機(jī)之間通信時(shí)不丟失[6]。

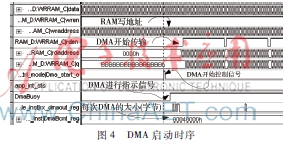

在本設(shè)計(jì)中,一次DMA傳輸?shù)拇笮殡p口RAM的容量。雙口RAM快寫滿時(shí)開(kāi)始DMA,每次DMA完成后,向上位機(jī)發(fā)中斷信號(hào)通知驅(qū)動(dòng)去上位機(jī)數(shù)據(jù)緩存區(qū)搬數(shù)據(jù)寫盤。為了克服Windows操作系統(tǒng)響應(yīng)PCIE中斷的非實(shí)時(shí)性和相對(duì)不確定性[7], 同時(shí)考慮FPGA存儲(chǔ)資源的限制, 雙口RAM 的容量選取256 KB,位寬為64 bit。

64位雙口RAM的地址范圍是0~7FFFh,且向雙口RAM寫一次的數(shù)據(jù)量為32 KB,為了保證每次啟動(dòng)DMA傳輸時(shí)雙口RAM中都有256 KB的數(shù)據(jù),且不引起讀寫沖突,設(shè)定RAM的寫地址等于7100h時(shí)啟動(dòng)DMA傳輸,即向RAM中寫入了226 KB的數(shù)據(jù),此時(shí)第8個(gè)32 KB的數(shù)據(jù)塊已經(jīng)向RAM中寫了2 KB。DMA的啟動(dòng)時(shí)序如圖4所示。

3系統(tǒng)存儲(chǔ)機(jī)制

該采集系統(tǒng)的存儲(chǔ)部分由上位機(jī)、PCI-E驅(qū)動(dòng)和應(yīng)用程序構(gòu)成。

3.1上位機(jī)配置

在本設(shè)計(jì)中,上位機(jī)選用IBM公司的System x3650 M3服務(wù)器。該服務(wù)器采用英特爾至強(qiáng)5600系列六核處理器,主頻為3.33 GHz,內(nèi)存配置為20 GB,內(nèi)部存儲(chǔ)由16塊型號(hào)為42D0752的硬盤組成RAID 0陣列,總存儲(chǔ)容量為8 TB。

3.2WDM驅(qū)動(dòng)程序開(kāi)發(fā)

本設(shè)計(jì)選用Visual C++ 6.0 、DriverStudio和DDK來(lái)進(jìn)行WDM驅(qū)動(dòng)程序開(kāi)發(fā)。

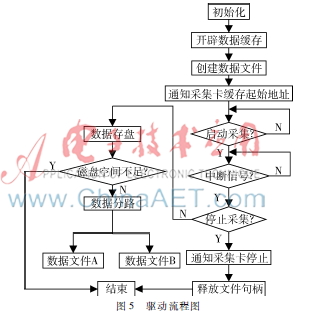

由于Windows操作系統(tǒng)的非實(shí)時(shí)性和寫磁盤陣列的瞬時(shí)速度的不穩(wěn)定性,有時(shí)不能實(shí)現(xiàn)將寫入內(nèi)存緩沖區(qū)的數(shù)據(jù)立即存儲(chǔ)在硬盤上,因此為了連續(xù)不斷地接收光纖數(shù)據(jù),必須在內(nèi)存中分配一塊大的連續(xù)內(nèi)存作為DMA的數(shù)據(jù)緩沖區(qū),這個(gè)緩沖區(qū)的大小一定要大于一次DMA傳輸?shù)臄?shù)據(jù)量,并采取環(huán)行存儲(chǔ)結(jié)構(gòu)[8]。經(jīng)在上位機(jī)上調(diào)試,在保證系統(tǒng)工作穩(wěn)定的前提下,數(shù)據(jù)緩存可開(kāi)到512 MB,即可緩存2 048次DMA的數(shù)據(jù)。采集數(shù)據(jù)時(shí),驅(qū)動(dòng)收到一次中斷就進(jìn)行一次256 KB的寫磁盤操作。驅(qū)動(dòng)程序的工作流程如圖5所示。

4性能測(cè)試與分析

為測(cè)試系統(tǒng)性能,設(shè)計(jì)一個(gè)已知格式的類STM16信號(hào)源:幀長(zhǎng)為16 bit×19 440=311 040 bit,幀頭為48個(gè)F6,48個(gè)28,其余段開(kāi)銷和管理單元指針全填充0;凈荷區(qū)域,第1行前4個(gè)字節(jié)為幀序號(hào),幀序號(hào)后為2個(gè)字節(jié)的數(shù)據(jù)標(biāo)識(shí),SFP_AS、FP_B的數(shù)據(jù)標(biāo)識(shí)分別為CCCC和DDDD,其余位置填充數(shù)據(jù)為0~18 788(0~4964h),第1行的前144個(gè)字節(jié)在發(fā)送時(shí)不加擾。

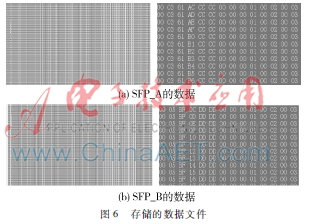

由于只存儲(chǔ)了STM16的凈荷數(shù)據(jù),因此在查看采集的數(shù)據(jù)時(shí),把每行數(shù)據(jù)大小設(shè)為16 bit×18 192 bit,這時(shí)看到的數(shù)據(jù)就如圖6所示。圖中左邊為數(shù)據(jù)文件的縮小圖,右邊為數(shù)據(jù)文件的放大圖。如果存儲(chǔ)文件的幀序號(hào)是連續(xù)的,且數(shù)據(jù)是對(duì)齊的,則證明數(shù)據(jù)沒(méi)有丟幀。

5結(jié)論

本系統(tǒng)能夠?qū)?路2.5 Gb/s的STM16信號(hào)進(jìn)行實(shí)時(shí)長(zhǎng)時(shí)間存儲(chǔ),保證連續(xù)存儲(chǔ)6 TB的光纖數(shù)據(jù)不丟幀,可連續(xù)存儲(chǔ)近3小時(shí),穩(wěn)定的存儲(chǔ)速率高達(dá)600 MB/s。該系統(tǒng)測(cè)試完后已移交給用戶使用。該系統(tǒng)還具有良好的適應(yīng)性并具有極大的升級(jí)空間,對(duì)FPGA代碼稍作修改并更換相應(yīng)速率的光電轉(zhuǎn)換模塊,該系統(tǒng)就可以采集STM1和STM4速率的SDH光纖數(shù)據(jù);如果把PCIE的IP配置成x8模式,并使用高性能的服務(wù)器和固態(tài)硬盤,該系統(tǒng)每秒的存儲(chǔ)速率可以達(dá)到GB級(jí)。該系統(tǒng)的研制,對(duì)于光通信設(shè)備的研發(fā)和光傳輸系統(tǒng)特性的測(cè)試具有重要的意義。

參考文獻(xiàn)

[1] BUDRUK R, ANDERSON D, SHANLE T.PCI Express系統(tǒng)體系結(jié)構(gòu)標(biāo)準(zhǔn)教材[M].田玉敏,王崧,張波,譯.北京:電子工業(yè)出版社,2005.

[2] PCISIG. PCI Express base specification revision 3.0[S].2010.

[3] 丁涇莉,朱春紅,成雪莉.RAID磁盤陣列技術(shù)及應(yīng)用[J].石油工業(yè)計(jì)算機(jī)應(yīng)用,2006,14(2):3941.

[4] 溫宇辰,李明偉,陳玉龍.PCIE總線光纖接口卡的設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2014,40(4)126129.

[5] ITUT. ITUT Recommendation G.707/Y.1322 Network node interface for the synchronous digital hierarchy (SDH) [S].2007.

[6] 楊阿鋒,吳帥,劉凱,等.PCIe接口高速數(shù)據(jù)傳輸卡的驅(qū)動(dòng)程序開(kāi)發(fā)[J].中國(guó)測(cè)試技術(shù),2008,34(2):6768.

[7] 呂喜在,張寶文,趙德鑫,等.基于PCI Express總線的高速海量光纖數(shù)據(jù)記錄儀的設(shè)計(jì)[J].計(jì)算機(jī)測(cè)量與控制,2010,18(9):22032206.

[8] 周立國(guó),梁淮寧,謝冬冬,等.基于PCI Express總線的數(shù)據(jù)傳輸卡的設(shè)計(jì)與實(shí)現(xiàn)[J].電子測(cè)量技術(shù),2007,30(11):2831.