在技術領域最著名的準則之一就是摩爾定律。在過去55年的時間里,“摩爾定律”已經描述并預測了晶體管的縮小,如一組稱為技術節點的數字在過去以大約每兩年一次的頻率更新。像一些基于物理學的世界末日時鐘一樣,幾十年來,節點數量一直在不停地下降,因為工程師設法使它們可以容納在同一塊硅片中的晶體管數量定期增加一倍。

其實在戈登·摩爾(Gordon Moore) 首次推出以他的名字命名的趨勢時,業界并沒有節點之類的東西,而且在一個IC上經濟上只能集成大約50個晶體管。

但是經過從業人員數十年的艱苦努力和數千億美元的投資,看看我們已經走了多遠!如果您有幸在高端智能手機上閱讀本文,那么它內部的處理器是使用稱為7納米節點的技術制造的。這意味著在一平方毫米的硅中大約有1億個晶體管。在5納米節點上制造的處理器現已投入生產,行業領導者期望在十年內致力于所謂的1納米節點。

然后呢?

畢竟1 nm已經幾乎是五個硅原子的寬度。因此,也許您會以為您很快就會想到摩爾定律將不再存在,半導體制造技術的發展將不會進一步提高處理能力,而固態設備工程是一條死路一條。

不過你會錯的。半導體技術節點系統繪制的前景圖是錯誤的。實際上,7納米晶體管的大多數關鍵特征都比7納米大得多,并且命名和物理現實之間的脫節已經存在了大約二十年。當然,這不是秘密,但這確實會帶來一些不幸的后果。

一是持續關注“節點”的事實掩蓋了這樣一個事實,即即使不再需要對CMOS晶體管的幾何結構進行進一步的微縮,但半導體技術實際上仍將有可能繼續推動計算向前發展;另一個問題是,以節點為中心的半導體發展觀未能以過去的產業振興方式指出前進的方向。最后,令人討厭的是,這么多的庫存投入到根本上毫無意義的數字中。

尋找更好的方法來標記行業里程碑的努力開始產生明顯更好的替代方法。但是,在一個聲名狼藉的競爭性行業中,專家是否會團結其中之一是個問題?讓我們希望他們這樣做,這樣我們就可以再次擁有一種有效的方法來衡量世界上最大,最重要,最有活力的行業之一的進步。

那么,我們將如何到達一個可以說是過去一百年中最重要的技術發展錯誤地出現了自然終點的地方?自1971年發布Intel 4004微處理器那年起,MOS晶體管的線性尺寸縮小了約1,000倍,單個芯片上的晶體管數量增加了約1500萬倍。用來衡量集成密度這種驚人進步的度量標準主要是尺寸,稱為金屬半節距(Metal half-pitch)和柵極長度(gate length)。這在一開始很方便,因為很長一段時間里,它們的數字幾乎相同。

金屬半節距是芯片上從一個金屬互連的起點到下一個金屬互連的起點的一半距離。在直到十年前一直占據主導地位的二維或“平面”晶體管設計中,柵極長度測量的是晶體管源極和漏極之間的空間。器件的柵極疊層位于該空間中,該柵極疊層控制著源極和漏極之間的電子流動。從歷史上看,它是決定晶體管性能的最重要尺寸,因為較短的柵極長度表明開關器件的速度更快。

在柵極長度和金屬半節距大致相等的時代,它們代表了芯片制造技術的基本特征,成為節點數。芯片上的這些功能通常每代縮小30%。這樣的減小使晶體管密度加倍,因為將矩形的x和y尺寸都減小30%意味著面積減半。

在整個19世紀70年代和80年代,使用柵極的長度和半節距作為節點一直達到其目的,但是在1990年代中期,這兩個功能開始脫鉤。為了繼續在速度和設備效率上取得歷史性的進步,芯片制造商比設備的其他功能更積極地縮短了柵極的長度。例如,使用所謂的130 nm節點制造的晶體管實際上具有70 nm的柵極。結果是摩爾定律密度加倍路徑的延續,但柵極長度不成比例地縮小。然而,在大多數情況下,行業仍然遵循舊的節點命名約定的節奏。

無意義的技術節點

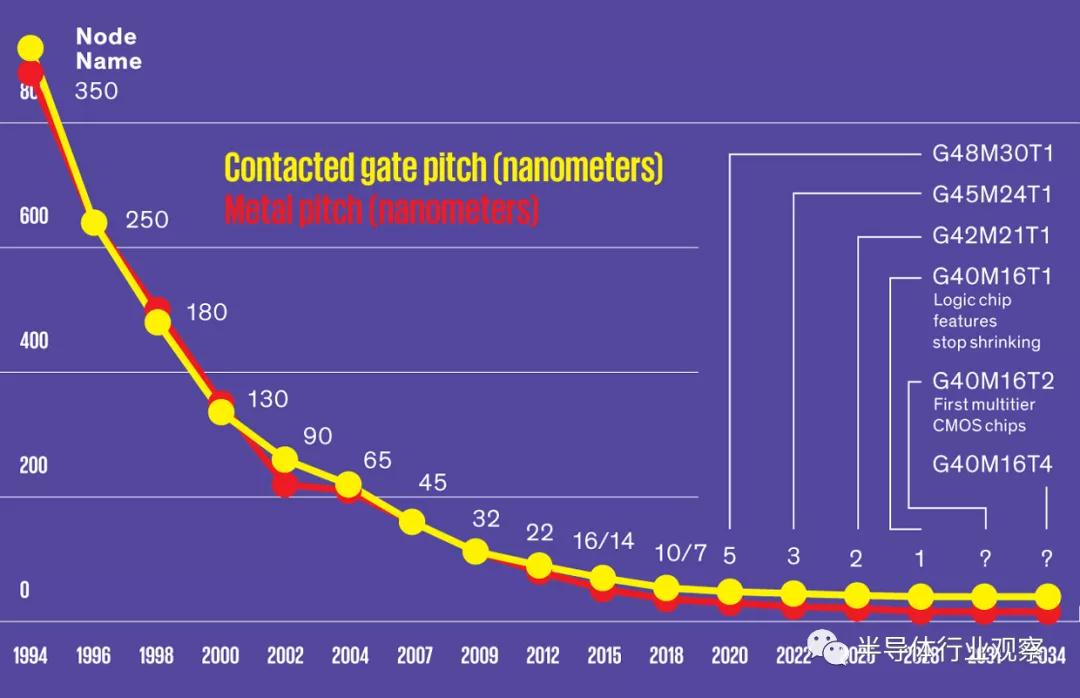

在19實際90年代中期之前,邏輯技術節點與其制造的CMOS晶體管的柵極長度同義。實際的柵極長度縮短了一會兒,然后停止微縮。

GMT方法

光刻技術的局限性:最先進的光刻技術,即極端紫外光刻技術,依賴于13.5納米波長的光。這意味著芯片功能將很快停止微縮。芯片制造商將不得不轉向單片3D集成,增加設備層次,以保持硅CMOS的密度增加。GMT方法通過說明兩個最關鍵的特征(接觸的柵極節距和金屬節距)的大小以及層數來對此進行跟蹤。

21世紀初的發展使事情變得更遙遠,因為處理器要克服功耗的限制。工程師們找到了保持設備改進的方法。例如,將晶體管的一部分硅置于源極(strain )下,可使電荷載流子在較低的電壓下更快地通過,從而提高了CMOS器件的速度和功率效率,而又不使柵極長度變得更短。

由于電流泄漏問題需要對CMOS晶體管進行結構更改,因此事情變得更加陌生。2011年,當英特爾在22納米節點上切換到FinFET時,這些設備的柵極長度為26納米,半間距為40納米,鰭片為8納米。

IEEE終身研究員和英特爾資深人士Paolo Gargini說,該行業的節點到那時絕對沒有意義,因為它與您可以在芯片上找到的與實際工作相關的任何尺寸都沒有關系“。誰領導著新的度量標準工作之一。

盡管半導體行業需要更好的東西,但已達成廣泛共識,盡管不是普遍的。一種解決方案是簡單地將術語與對晶體管重要的實際特征的大小重新對齊。這并不意味著要回到柵極長度,后者不再是最重要的功能。

相反,建議使用兩種方法來表示制造邏輯晶體管所需面積的實際限制。一種稱為接觸柵間距。此短語是指從一個晶體管的柵極到另一個晶體管的柵極的最小距離。另一個重要指標金屬間距測量兩個水平互連之間的最小距離。(由于柵極長度現在已不再重要,因此不再有任何理由將金屬間距分成兩半。)

Arm首席研究工程師Brian Cline解釋說,這兩個值是在新流程節點中創建邏輯的”最小公分母“。這兩個值的乘積很好地估計了晶體管的最小可能面積。其他每個設計步驟(形成邏輯或SRAM單元,電路塊)都增加了最低限度。他說:”具有深思熟慮的物理設計特征的良好邏輯過程將使該值的降級最小“。

IEEE國際設備和系統路線圖(IRDS)主席Gargini 在四月份提出,該行業采用結合接觸式柵極節距(G),金屬節距(M)的三位數指標來”回歸現實“。,對于未來的芯片來說,至關重要的是,芯片上的設備的層數或層數(T)。(IRDS是”國際半導體技術路線圖“(ITRS)的繼承者,ITRS是一項現已失效,數十年之久的全行業研究,旨在預測未來節點的各個方面,從而使該行業及其供應商有一個統一的目標。)

”這三個參數是評估晶體管密度所需的全部知識,“ ITRS的負責人Gargini說。

IRDS路線圖顯示,即將推出的5nm芯片的接觸柵距為48nm,金屬柵距為36nm,并且具有單層結構,即公制G48M36T1。它并不能完全解決問題,但是它確實傳達了比” 5-nm節點“有用的信息。

與節點命名法一樣,此GMT指標的柵極間距和金屬間距值在整個十年中將繼續減小。但是,它們的運行速度將越來越慢,以目前的速度,到現在大約10年后才能達到終點。到那時,金屬間距將接近極限紫外光刻可以解決的極限。盡管上一代光刻機能夠經濟高效地克服其193 nm波長的可感知極限,但沒有人期望極端紫外線會發生同樣的事情。

Gargini說:”到2029年左右,我們達到了光刻技術的極限。“ 之后,”前進的方向是堆疊……這是增加密度的唯一途徑。“

屆時,層數(T)項將變得非常重要。當今先進的硅CMOS是單層晶體管,通過十多個金屬互連層將它們鏈接到電路中。但是,如果您可以構建兩層晶體管,則可能使器件的密度幾乎翻倍。

對于硅CMOS,目前仍在實驗室中,但是時間不長。十多年來,工業研究人員一直在探索生產” 單片式3D IC “的方法,這些芯片中一層又一層地堆疊著晶體管。這并非易事,因為硅加工溫度通常很高,以至于建造一層會損壞另一層。盡管如此,一些工業研究工作(尤其是比利時納米技術研究公司Imec,法國的CEA-Leti和Intel正在開發可以在CMOS邏輯中構建兩種類型晶體管的技術-NMOS和PMOS-一種在另一種之上。

即將出現的非硅技術甚至可以更快地進入3D。例如,麻省理工學院教授馬克斯·舒拉克(Max Shulaker)和他的同事們參與了依賴于碳納米管晶體管層的3D芯片的開發。因為您可以在相對較低的溫度下處理這些設備,所以與使用硅設備相比,可以更輕松地將它們構建為多層。

其他公司正在研究可以在硅上方的金屬互連層內構建的邏輯或存儲設備。其中包括由原子稀薄的半導體(如二硫化鎢)制成的微機械繼電器和晶體管。

大約一年前,一群著名的學者聚集在加州大學伯克利分校的校園中,提出了自己的標準。

這種專家的組合尋求一種指標,該指標可以消除節點的世界末日時鐘氛圍。他們決定,至關重要的是,該指標不應有自然終點。換句話說,數字應該隨著進步而上升而不是下降。它還必須簡單,準確,并且與改進半導體技術的主要目的(功能更強大的計算系統)相關。

為此,他們需要做的事情不僅僅是IRDS的GMT指標所能描述的,用于制造處理器的技術。他們想要一個不僅考慮處理器而且還考慮整個計算機系統其他影響性能的關鍵因素的度量標準。這可能看起來過于雄心勃勃,也許是這樣,但是隨著方向計算的開始,它顯得格外刺眼。

破解Intel Stratix 10現場可編程門陣列的封裝,您將發現的不僅僅是FPGA處理器。在封裝內部,處理器芯片被一系列” 小芯片“ 包圍,其中包括兩個高帶寬DRAM芯片。用密集的互連陣列蝕刻的一小片硅片將處理器連接到內存。

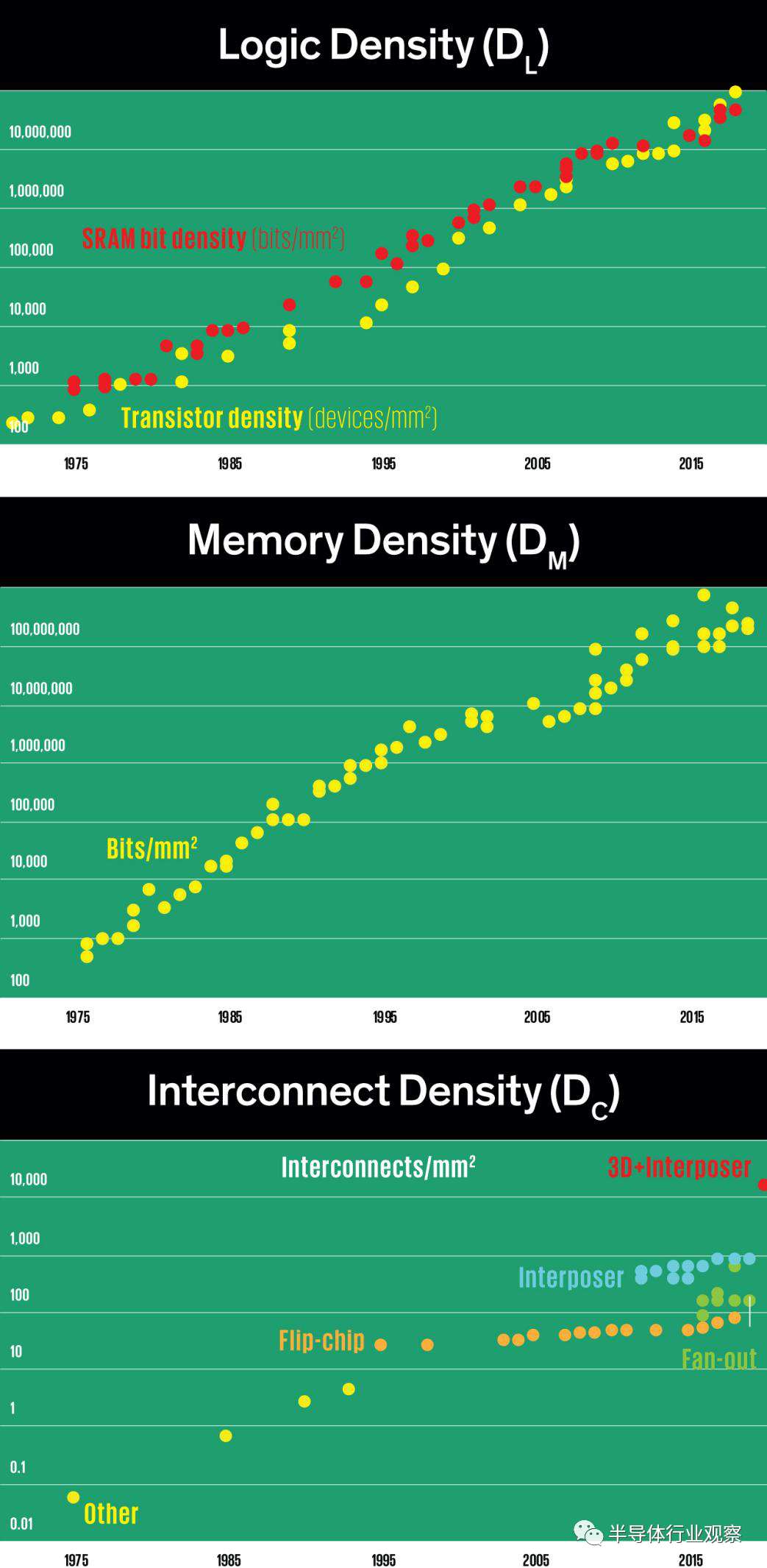

一臺計算機最基本的就是:邏輯,內存以及它們之間的連接。因此,要拿出自己的新的指標,為此該小組選擇的參數是DL, DM, 和 DC。這就是LMC度量。

根據LMC指標的發起者,在當今以數據為中心的時代,D L,D M和D C的改進共同為計算系統的整體速度和能源效率做出了重要貢獻。他們繪制了歷史數據,顯示了邏輯,內存和連接性增長之間的相關性,這表明D L,D M和D C的均衡增長已經持續了數十年。這種平衡在計算機體系結構中是隱含的他們認為,令人驚訝的是,它適用于各種復雜程度的計算系統,從移動和臺式機處理器一直到世界上最快的超級計算機。小組成員說,這種均衡的增長表明未來將需要類似的改進。

LMC方法

稱為LMC的節點度量標準的替代方法通過說明邏輯密度(D L),主存儲器的密度(D M)以及鏈接它們的互連的密度(D C)來獲取技術的價值。

在LMC度量標準中, D L是邏輯晶體管的密度,以每平方毫米的cell數量表示。D M是每平方毫米內存中系統主內存的密度。D C是邏輯與主存儲器之間的連接,以每平方毫米的互連數表示。如果存在多層設備或3D芯片堆疊,則超過該平方毫米的整個體積都非常重要。

D L可能是三者中歷史上最熟悉的一種,因為自從第一批IC以來人們一直在計算芯片上的晶體管數量。雖然聽起來很簡單,但事實并非如此。處理器上不同類型的電路在密度上有所不同,這在很大程度上是由于鏈接設備的互連。邏輯芯片中最密集的部分通常是構成處理器高速緩存的SRAM存儲器,數據被存儲在其中以便快速重復訪問。這些高速緩存是六晶體管單元的大型陣列,可以將它們緊密封裝在一起,部分原因是其規則性。通過這種測量,迄今為止報告的D L的最大值是使用TSMC 5納米工藝制造的135兆位SRAM陣列,每平方毫米封裝了2.86億個晶體管。在建議的命名法中,該名稱應為286M。

但是,邏輯塊比嵌入其中的SRAM更復雜,更不統一且密度更低。因此,僅根據SRAM判斷技術可能并不公平。2017年,當時的英特爾高級研究員Mark Bohr提出了一種使用某些常見邏輯單元的加權密度的公式。該公式著眼于一個簡單且普遍存在的兩輸入,四晶體管與非門以及一個常見但更復雜的電路(稱為掃描觸發器)的單位面積晶體管數。在典型設計中,它根據此類小柵極和大單元的比例對每個元素加權,以產生每平方毫米單個晶體管的結果。Bohr當時說SRAM的密度如此之大,應單獨測量。

據AMD高級研究員Kevin Gillespie稱,AMD在內部使用類似的東西。他說,如果一個度量標準不考慮設備的連接方式,那將是不準確的。

由幾位專家分別提出的另一種可能性是,在經過商定的,大面積的半導體知識產權中,例如在Arm廣泛使用的處理器設計中,測量平均密度。

實際上,根據Arm的Cline的說法,Arm放棄了單一指標的嘗試,而是希望從完整的處理器設計中提取電路功能塊的密度。他說:”我認為對于所有硬件應用來說,沒有一個適合所有人的邏輯密度指標“,因為不同類型的芯片和系統的差異太大。他指出,不同類型的處理器(CPU,GPU,神經網絡處理器,數字信號處理器)具有不同的邏輯和SRAM比率。

最后,LMC發起者選擇不指定特定的D L測量方法,而將其留給業界討論。

測量D M更加簡單。目前,主存儲器通常是指DRAM,因為它價格便宜,耐用性高并且讀寫速度相對較快。

DRAM單元由一個晶體管控制,該晶體管控制對將位存儲為電荷的電容器的訪問。由于電荷會隨時間泄漏,因此必須定期刷新cell。如今,電容器是建立在硅上方的互連層中的,因此密度不僅受晶體管尺寸的影響,還受互連幾何形狀的影響。LMC集團在已發表的文獻中可以找到的最高D M值來自三星。在2018年,該公司詳細介紹了DRAM技術,密度為每平方毫米(200M)2億個單元。

DRAM可能并不總是保持其作為主存儲器的位置。當今,諸如磁阻RAM,鐵電RAM,電阻性RAM和相變RAM之類的替代存儲技術已投入商業生產,其中一些作為嵌入處理器本身的存儲器,另一些作為獨立芯片。

在主內存和邏輯之間提供足夠的連接已經是當今計算系統的主要瓶頸。D C衡量的處理器和內存之間的互連歷史上是由封裝級技術而非芯片制造技術創建的。與邏輯密度和存儲器密度相比,DC已經在過去幾十年穩步少得多的改善。取而代之的是,隨著新封裝技術的引入和改進,出現了離散的跳躍。在過去的十年中,尤其是多事之秋,因為單芯片單片系統(SoC)已讓位給在硅中介層上緊密結合在一起的小芯片(所謂的2.5D系統)或堆疊成3D排列的小芯片。使用臺積電集成芯片系統的系統3D芯片堆疊技術具有最高的DC,在每平方毫米(12K)12000個互連。

但是,DC不一定需要將邏輯連接到單獨的存儲芯片。對于某些系統,主存儲器是完全嵌入式的。例如,Cerebras Systems的機器學習大型芯片完全依賴于嵌入在單個大規模硅片上的邏輯核附近的SRAM。

LMC發起者建議,將描述一個將所有三個參數(D L,D M和D C)中最好的一個組合的系統[260M,200M,12K]。

英特爾首席技術官邁克爾·梅伯里(Michael Mayberry)認為,用一個數字來描述半導體節點的先進性已經過去了很長時間。但是,他原則上喜歡具有全面的系統級度量的想法。他說:”即使是不完美的,也可以選擇達成共識的東西,而不是當前的節點品牌。“

他希望看到LMC擴展了更多詳細級別,以指定要測量的內容和方式。例如,關于D M值,Mayberry說,它可能需要專門與與其所服務的處理器位于同一芯片封裝內的存儲器相關。他補充說,歸類為”主內存“的內容可能也需要進行微調。將來,處理器和數據存儲設備之間可能會有多層存儲。例如,英特爾和美光制造的3D XPoint內存是一種非易失性系統,在DRAM和存儲之間占據一席之地。

進一步的批評是,基于密度的度量標準(如LMC)和基于光刻的度量標準(如GMT)均與代工廠和存儲芯片制造商的客戶所要求的相距甚遠。AMD的Gillespie說:”有[密度]區域,但也有性能,功能和成本。“ Mayberry補充說,每種芯片設計都圍繞這四個軸進行權衡,以至于”沒有一個單一的數字可以反映出節點的性能如何“。

”排名第三的內存和存儲最重要的指標仍然是單位成本,“ 全球第三大DRAM制造商美光科技公司高級研究員兼副總裁Gurtej Singh Sandhu說。”還密切考慮了其他幾個因素,包括基于特定市場應用的各種性能指標。“

還有一個派別認為,此時甚至不需要新的指標。GlobalFoundries負責工程和質量的高級副總裁Gregg Bartlett說,這些措施”實際上僅在以縮放為主導的應用中才有用“ ,該公司于2018年結束了對7納米工藝的追求。這個空間以及有限的客戶和應用程序數量,因此與絕大多數半導體行業的關系不大。” 僅剩下英特爾,三星和臺積電追求最后幾個CMOS邏輯節點,但它們幾乎沒有參與其中,在全球半導體制造收入中占了很大一部分。

Bartlett的公司不在該小組中,他認為CMOS邏輯與專用技術(例如嵌入式非易失性存儲器和毫米波無線電)的集成對行業的未來至關重要,而不是擴展規模。

但是,毫無疑問,持續擴展對許多半導體消費者而言很重要。盡管出于不同的原因,LMC指標和GMT指標的創建者都感到緊迫感。對于LMC支持者來說,在晶體管縮放的重要性不高的時代,業界需要明確其長期發展前景,以便他們能夠招募技術人才來實現這一未來。

對于Gargini和GMT支持者而言,這是為了使整個行業步入正軌。他認為,如果沒有指標的同步,該行業的效率就會降低。他說:“這增加了失敗的可能性。” “我們有10年的時間”,直到硅CMOS完全停止收縮。“僅勉強夠用”以產生將使計算不斷發展的必要突破。