更小、更高效的電源轉換器是過去幾十年來的發展方向,而這個趨勢也將持續下去。這是通過使用新拓撲、新型材料和新集成工藝來達到的。歐盟2020 項目的重點是集成新型材料,所以也資助了 GaNonCMOS 項目。該項目的目標是將 GaN 和 Si 在不同層級上進行高密度集成(PCB、堆棧和芯片),開發適用于高開關頻率和 PCB 嵌入的新型軟磁材料。與一般的主流不同,該項目的興趣不是將GaN 材料使用在常見的650V范圍內,而是運用在低于 100V 的 DC/DC 轉換,也就是服務器應用以及汽車和航空航天工業的低功率 PoL 轉換器。來自奧地利、比利時、德國、荷蘭和愛爾蘭的 11 家行業領導者和研究機構共同加入了這個項目。RECOM 集團也參與了這些新技術的開發,并遵循公司的目標在電源轉換領域上帶來創新、集成 (3DPP) 和更可靠的解決方案。

嵌入式

該項目的重點之一是將組件嵌入到 PCB 中。使用這種技術可以在 PCB 核心中隱藏一個或多個組件。嵌入的主要限制是組件的厚度及在各種環境條件下的行為和表現。嵌入式組件可以是 IC、開關或無源組件,使用何種組件取決于設計目標。厚銅層與嵌入式組件的引腳連接可以形成明確的熱路徑。IC 和 MOSFET 可以放得很近以降低寄生電感和實現更高的開關速度。電阻和電容等小型無源器件可以嵌入同一個空腔中,只有較大的器件留在外面,例如磁性器件、輸入或輸出電容。由于采用 FR4 耐燃材料,電容較不受到來自開關或 IC 熱壓力的影響。雖然 3D 結構讓整個布局變得更加復雜,但它具有更小的開關和控制回路的優勢。其他重要的優點包括較小的面積和防止逆向工程的保護。

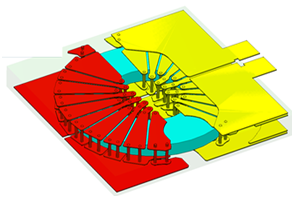

另一種方法是降低 PCB 的厚度。例如,在降壓轉換器的設計中電感通常是最高的器件。如果需要非常扁平的設計,有可能無法找到合適的薄型電感,而這個項目實現了嵌入式磁性器件的想法。但是當特定參數的芯片尺寸太大無法嵌入,要如何嵌入所需的電感?磁性片材為解決之道。具某些磁性特性且非常薄的材料(100-200 μm)可以切割成不同的形狀并放在 PCB 上。PCB的布線形成了繞線結構。與緊湊但較高的片式電感相比,這種電感有較大的面積,而且已經有好幾種采用這種技術的例子。減少空間的最佳方法是讓電感的面積與 PCB 上其他小器件的面積差不多一樣(請見圖 1)。下面的插圖描繪了內層使用有繞組的環形磁芯形狀來形成環形電感(請見圖 2)。其他形狀和繞組結構也可能可行,取決于可用空間、必要的耦合、電流容量等因素。圖 3 描繪了一個簡單的 1:1 變壓器設計,磁性材料采用相同的環形磁芯形狀。嵌入式變壓器的優點是增加了污染等級并降低了爬電距離和間隙要求。要滿足更高電感值和更高電流所需的面積明顯增加了。雖然磁片的嵌入過程已在更大的范圍上 (10x10 cm) 得到驗證,但最理想的是較低電流的應用,最高到2A。有些參數會造成影響,例如繞組數量會增加電感的直流電阻但降低整體效率。

材料及可靠性

在項目中測試了 10 多種不同的磁性片材以確定是否適合嵌入。就如片式電感一樣,片材也有不同的屬性。 片材是在高壓下嵌入然后封裝在 PCB 中。為了評估電氣參數的穩定性和機械一致性,根據汽車標準(AEC Q200)對大量樣品進行了長期可靠性測試,包括:溫度循環(2000 次)、溫濕度偏壓(85°C、85% RH 下 1000 小時)、高溫儲存(125°C下1000 小時)、低溫儲存(-55°C下1000小時),以及高度加速壓力測試(130°C、85% RH 下 96 小時)。只有少數材料不但通過了這些測試也沒有改變參數或造成 PCB分層。 這些知識有助于運用這個技術,在設計階段避開風險材料因為有些材料會在嵌入過程中破裂。

大多數片材適用于 1MHz 至 5MHz 之間的開關頻率。除了對磁性片材進行測試以外,該項目還開發適合20MHz左右開關頻率的新型磁性材料。在幾項試驗的過程中也成功產出了一種可以嵌入的新型化合物。

芯片級集成

正如項目名稱所示,目標之一是將 GaN 器件(開關)與 CMOS 驅動器集成在一起。為了符合集成過程的電氣和物理要求,GaN 和 Si 器件均在開發過程中歷經多次迭代的自行開發和制造。新開發的工藝稱為晶圓直接鍵合 (IBM),能在切割之前鍵合兩個晶圓。這個復雜的過程仍在測試階段,但當預期的障礙被克服后,這將是芯片集成的另一個里程碑,因為一個器件結合了兩種半導體材料的優點達到了兩全其美。實際上,驅動器和開關之間沒有寄生電感的話可以在數百 MHz 范圍內實現極高的開關頻率,結果是無源組件(磁性組件和電容器)的尺寸必須夠小,進而大幅降低功率轉換的體積。

圖 1 – 降壓轉換器的嵌入式環形電感器設計及繞組層(AT&S 和 RECOM)

圖 2 – 降壓轉換器的嵌入式環形電感器設計的側視圖,顯示了PCB 內的磁片(AT&S 和 RECOM)

圖 3 – 具有明顯分離繞組的環形變壓器設計示例 (AT&S)

圖 4 – 有分層(左)和無分層(右)的嵌入式磁片橫截面 (AT&S)