談及半導體設備,大家常常提起的光刻機。但實際上,在半導體領域還有一些非常重要的設備,如ATE(Automatic Test Equipment)就是其中一個重要類別。

據維基百科介紹,所謂ATE是指可以利用自動化技術,針對產品進行快速測試的設備。具體到半導體領域,是指在芯片制造過程中,用于CP(Chip Probe)和FT(Final Test)測試的設備。只有經歷了這兩個步驟,才能盡可能地保證交付給開發者芯片的可靠性。

隨著芯片(尤其是SoC)工藝的穩步推進,制造成本的持續增加,作為芯片生產流程重要一環,測試的被重視程度越來越高,這就給相應的ATE供應商帶來了巨大的挑戰。日前,全球領先ATE供應商泰瑞達的銷售副總經理黃飛鴻分享了市場對ATE需求的演變以及他們的應對之策。

漸變的SoC測試需求

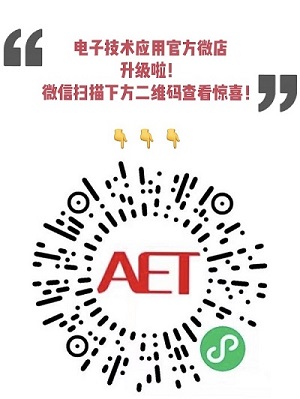

黃飛鴻表示,在1990到2025年這幾十年里,工藝在快速演進。與此同時,對ATE也提出了更多的需求。

據介紹,90年代是CMOS蓬勃發展的時代,當時半導體SoC芯片的功能越來越強,芯片上面也會集成模擬的能力,包括數據接口的傳輸率也在同步增加。這就給當時的ATE提出了挑戰。“原先老的測試平臺實際上不能夠覆蓋新集成的模擬和高速接口測試的需求,因此便需要增強ATE的功能性。也就是說當時的ATE設計研發要滿足日趨復雜的SoC芯片需求”,黃飛鴻告訴記者。

來到2000到2015年間,工藝越來越先進,芯片尺寸也越來越小,芯片上的晶體管集成度也越來越高。這個時候,芯片對于測試的專門設計、標準化接口和DFT設計能力也不斷地加強。因為只有這樣做,才能夠覆蓋到包括越來越深的SCAN掃描測試、BIST測試和標準化接口測試等在內的日趨復雜的芯片測試需求。

同時,因為芯片規模的變大,帶來了更高的測試成本,這就要求測試從以前的單工位,往前推出到多工位,進而帶來同測的要求。換個說法,就是說這個時代對測試的一個重要需求就是測試機板上面能夠集成越來越多的通道,能夠同時做2工位,4工位,8工位的測試。

進入2020年以后,芯片制造工藝微縮到了5nm,并持續往3nm推進,這個時代芯片晶體量增長速度又開始超出了設備的極限。再者,這個時代的芯片周期縮短、芯片復雜度提升幅度也極大,這就讓芯片的測試進入了復雜性時代。這就給其帶來了新一輪的挑戰。

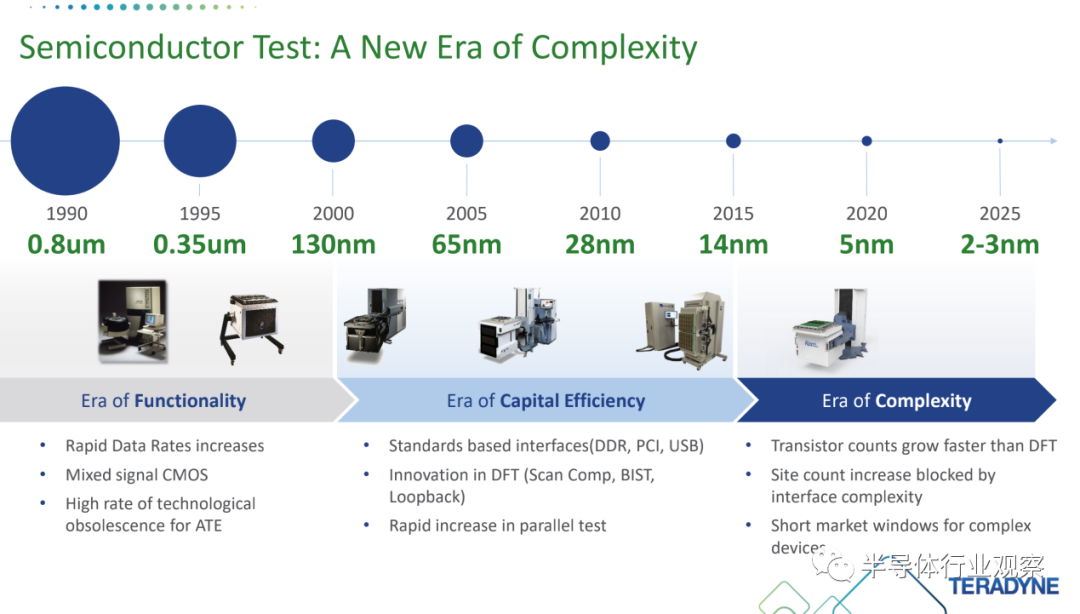

據黃飛鴻介紹,先進工藝演進首先帶來的是芯片測試時間的增加,這一部分是由給數量暴增的晶體管進行測試造成的。如下圖左所示,如果以2015年時間為測試基準,現在同樣測試所花的時間可以接近當年的2.5倍,未來甚至可以進一步增加到三倍;此外,對于類似模擬和射頻這樣的芯片,在做測試的時候需要先做Trim調整,然后再測試,這又帶來了測試時間的增加。“測試時間的增加,意味著更高的測試成本”,黃飛鴻強調。

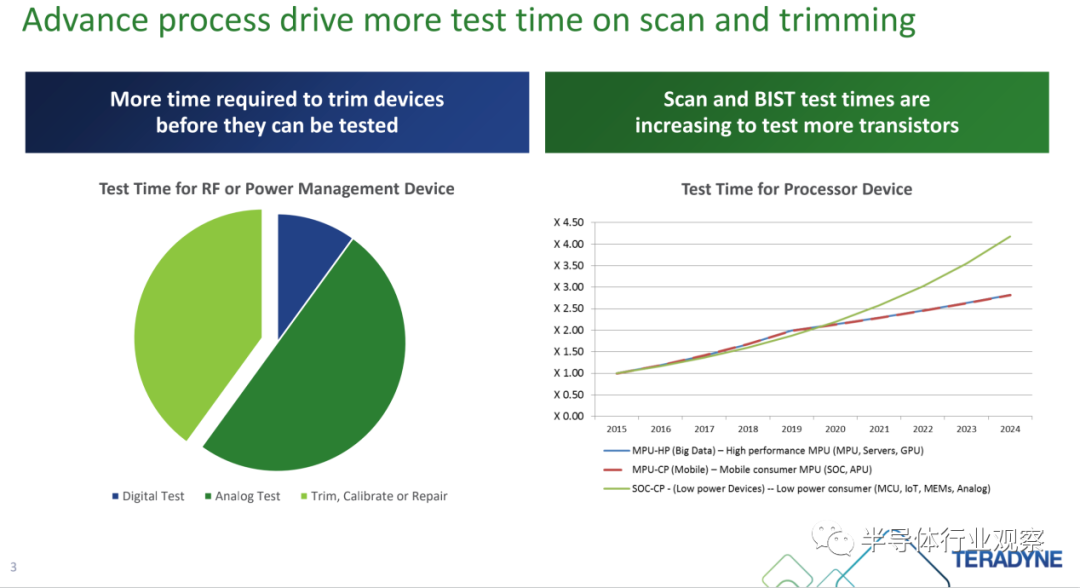

他進一步指出,Wafer yield是先進工藝帶來的另一個挑戰。

如上圖右所示,黃飛鴻告訴記者,隨著工藝尺寸的不斷縮減,wafer的初次yield不斷下降。越來越復雜的芯片也讓每顆芯片的die size不斷增加,進而增加芯片的失效概率。在這兩個因素的疊加下,800平方毫米的die size wafer的初次yield跌到不及10%。但與此同時,我們對芯片的需求卻越來越高。

“在過往,我們還能接受較高的消費電子芯片失效數,但隨著消費和移動芯片走向汽車,我們對芯片失效要求有了指數型的增長,這就讓芯片測試變得難上加難”,黃飛鴻舉例說。

泰瑞達的見招拆招

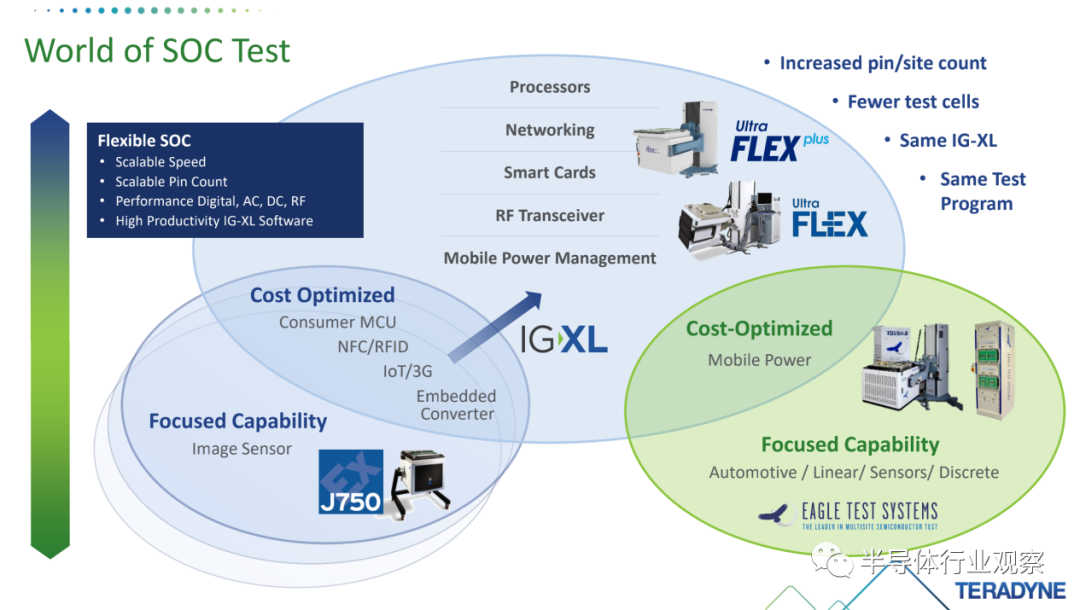

毫無疑問,泰瑞達是ATE領域的龍頭之一,在過去多年里,他們也針對SoC測試推出了多款領先設備,其中J750系列無疑是當中一個代表性產品。

資料顯示,泰瑞達J750系列提供了世界領先的汽車和消費應用類MCU產品測試解決方案,也是圖像傳感器測試的全球領導者。隨著低成本產品的集成度不斷增長,并已延伸到指紋傳感器,MEMS和帶有MCU無線功能的物聯網(IOT)產品,J750測試系統的可擴展性使其成為這類產品的理想選擇。

但正如黃飛鴻所說,J750是測試偏簡單的芯片,追求更多的是低成本解決方案。于是,泰瑞達推出了UltraFLEX系列,來應對更高級別的測試需求。據了解,UltraFLEX 測試系統采用業內領先的軟件,具有測試復雜的片上系統 (SoC) 芯片所需的性能和精度,可顯著降低測試成本并加快產品上市速度。

從官網介紹我們可以看到,UltraFLEX系列能夠為移動應用處理器、數字基帶處理器、高數據速率 RF Transceiver、RF Connectivity芯片、毫米波、5G、電源管理 芯片 (PMIC)、微處理器、網絡處理器、高速 SERDES(串行器/解串器)和背板收發器、存儲控制器、高端微控制器、音頻和視頻處理器等芯片的測試提供全方位的支持。

雖然有了UltraFLEX系列,但隨著芯片性能和種類的增加,又給測試提出了新的需求,于是泰瑞達又推出了新的UltraFLEXplus系列,聚焦解決人工智能和5G通信所帶來的新興數字測試需求。

據黃飛鴻介紹,UltraFLEXplus 系列首先增加了工位數,并通過提高并行測試效率來減少多工位測試時間開銷,從而滿足測試成本需求。減少測試單元的數量可以最大程度降低總制造成本,測試單元的減少可以轉化為更少的探針臺和分選器、更低的設備功率和更少的操作人員。

其次,UltraFLEXplus的芯片測試接口板設計做了完全革命性的改進,采用了Broadside技術,使接口板的應用區域更大,同時可以使接口板PCB層數做的更少。據官方資料介紹,與傳統的 ATE 相比,Broadside DIB 結構,將板卡較原先結構旋轉了 90 度,因此板卡的資源,能夠向芯片區域并行傳送。這意味著每個工位,都能夠獲得與之匹配的信號傳輸路徑。通過簡化原本復雜的 DIB布局,實現更快的上市時間、更多的工位數和更高的PCB良率。

第三,UltraFLEXplus還采用了全新的PACE架構,以最小的工程量創造出最高的測試單元產能。據了解,之所以PACE 取得這一成果,主要得益于其分布式多控制器 (DMC) 控制架構,以及板卡硬件數據帶寬的提高。多核系統控制器能夠保持板卡高效、協調工作,從而提高系統產能。增加工位數提高生產效率,以及改進并行測試效率,讓制造商能夠減少 15%-50% 的測試單元部署。

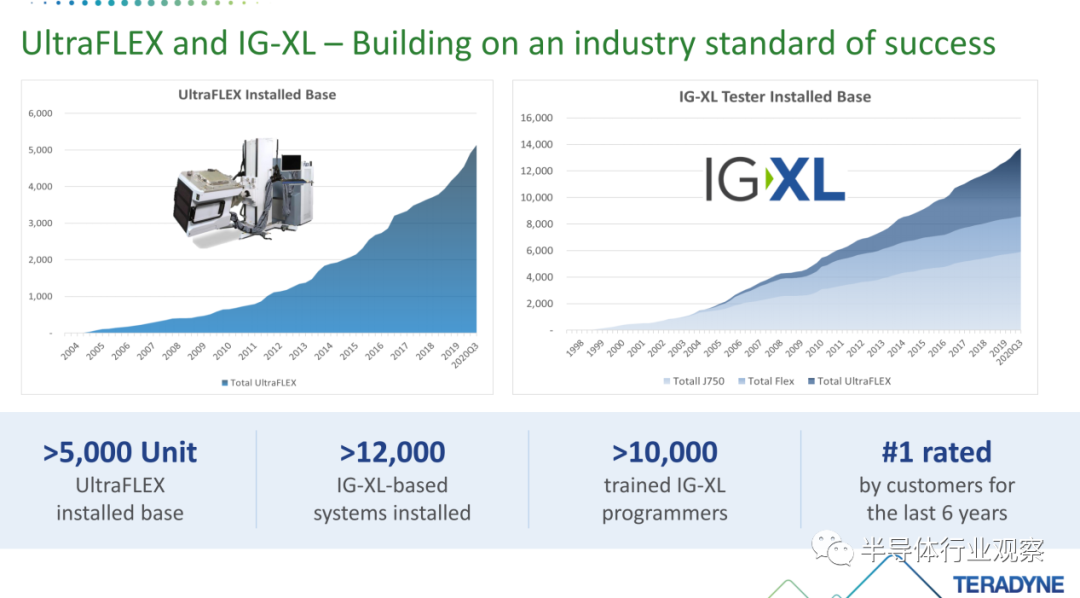

最后值得一提的是,泰瑞達讓公司的UltraFLEX和UltraFLEXplus系列都保持了對IG-XL 軟件的支持,那就意味著工程師開發的程序可以輕易在上述設備間可以無縫遷移,大大縮短開發工程師的開發時間。

黃飛鴻也指出,公司目前已經有接近6000套UltraFLEX裝機,UltraFLEXplus系列自2019年推出以來,截止現在全球的裝機量也已經接近600臺,IG-XL軟件裝機更是已經超過1.2萬套。公司同時還培訓了超過1萬名的IG-XL程序開發人員,為未來的測試需求爆發做好充分準備。

在問到隨著芯片制造工藝持續演進,會給未來的測試帶來什么樣的需求變化的時候,黃飛鴻回應道:

“這對測試設備帶來的要求是兩個:第一個是更高的數據率下面怎么樣保證測試的精度,這一定是隨著工藝的演進越來越嚴苛;第二個是隨著工藝不斷演進,芯片里面集成晶體管的密度是呈幾何增加。那這個掃描量要很長,甚至要超過1個G以上,這對我們帶來的挑戰就是如何滿足在每個通道下面漸增的存儲向量深度需求。這就是我們為什么在plus這代產品通過一些技術可以把掃描量深度最大可以容納19.2G的原因。從目前來看,即使到了2納米,3納米,甚至再往前走,這個向量深度也能夠滿足這樣的需求。”

黃飛鴻指出,隨著工藝不斷演進到往后有一個趨勢,wafer測試比重會增加,FT測試反而會減少。這主要是從芯片提升性能的方式引起的。

據他所說,未來工藝演進技術有兩條路,一條路是5納米,2納米,1納米不斷往前走,但其實演進難度越來越難了。另外一條是走Chiplet(芯粒)路線,也就是一顆芯片里面不同的模塊不一定每個模塊芯片都需要用到2納米,3納米,有些射頻、模擬、混合信號需要16納米就夠了。在這種情況下,把不同功能的芯片(Die)在片上再把它合封在一起,這就意味著封起來之后,你做不了相關測試。那對于芯片來說CP比重會增加,FT會減少。

“未來,可能還會有一個新趨勢,那就是合封之后也有通訊接口的標準,這個標準怎么樣通過外圍共用的通道access到每一個die去,目前還沒有特別好的統一的標準。如果這個標準出來,可能也會通過這個方式訪問到每個芯片(die)再進行測試。”黃飛鴻表示。

到了那時,我們又將能看到泰瑞達是如何“出招”應對。