1.

靜態(tài)時(shí)序分析

1.1 什么是靜態(tài)時(shí)序分析

靜態(tài)時(shí)序分析(簡(jiǎn)稱(chēng)STA)是用來(lái)驗(yàn)證數(shù)字設(shè)計(jì)時(shí)序的技術(shù)之一,另外一種驗(yàn)證時(shí)序的方法是時(shí)序仿真,時(shí)序仿真可以同時(shí)驗(yàn)證功能和時(shí)序。“時(shí)序分析”這個(gè)術(shù)語(yǔ)就是用來(lái)指代“靜態(tài)時(shí)序分析“或”時(shí)序仿真“這兩種方法之一,簡(jiǎn)單來(lái)說(shuō),時(shí)序分析的目的就是為了解決設(shè)計(jì)中的各種時(shí)序問(wèn)題。

靜態(tài)時(shí)序分析是基于同步電路設(shè)計(jì)模型的。主要目的就是為了提高系統(tǒng)工作主頻以及增加系統(tǒng)的穩(wěn)定性。通過(guò)靜態(tài)時(shí)序分析,一方面可以增加系統(tǒng)穩(wěn)定性,減少亞穩(wěn)態(tài)的發(fā)生,另一方面通過(guò)附加約束可以控制邏輯的綜合、映射、布局和布線,以減小邏輯和布線延時(shí),從而提高工作頻率。

1.2 靜態(tài)時(shí)序分析和時(shí)序仿真

靜態(tài)時(shí)序分析分析的是時(shí)序,檢查在一定頻率下,電路有無(wú)時(shí)序違例

時(shí)序仿真檢查的是功能,需要在設(shè)計(jì)的端口添加激勵(lì)

靜態(tài)時(shí)序分析的特點(diǎn):更快更簡(jiǎn)單,能不添加激勵(lì)的情況下檢查完所有的時(shí)序路徑

時(shí)序仿真的特點(diǎn):檢查電路的功能仿真,比較慢

時(shí)序分析:先用STA對(duì)電路進(jìn)行時(shí)序檢查,再進(jìn)行時(shí)序仿真

1.3 在設(shè)計(jì)的哪個(gè)階段使用STA以及如何使用靜態(tài)時(shí)序分析

RTL設(shè)計(jì)階段:此階段需要完成電路的功能設(shè)計(jì),而且此階段是行為級(jí)網(wǎng)表,無(wú)需STA;當(dāng)邏輯功能設(shè)計(jì)完成后,綜合成門(mén)級(jí)網(wǎng)表,此時(shí)需要使用STA分析時(shí)序最差或關(guān)鍵路徑,進(jìn)行設(shè)計(jì)的邏輯優(yōu)化(此時(shí)更改的都是邏輯單元)并生成時(shí)序約束文件(SDC)

1.4 在邏輯級(jí)(未進(jìn)行物理設(shè)計(jì)的門(mén)級(jí)),STA可采用哪些模型

理想的互連線或者基于線負(fù)載模型的互連線

帶有延遲和抖動(dòng)估計(jì)值的理想時(shí)鐘

在物理設(shè)計(jì)階段,除了上述模型,STA還可采用以下模型:

具有近似估計(jì)值的全局布線的互連線、具有近似寄生參數(shù)提取值的實(shí)際布線的互連線、具有可以簽收(signoff)精度寄生參數(shù)提取值的實(shí)際布線的互連線

實(shí)際的時(shí)鐘樹(shù)

包括串?dāng)_的影響或者不包括串?dāng)_的影響

1.5 靜態(tài)時(shí)序分析同樣具有局限性,在如下的常見(jiàn)情況下無(wú)法使用

對(duì)未知態(tài)X的處理

PLL未正確設(shè)置

分析IO接口時(shí)序

分析模擬模塊和數(shù)字模塊之間的接口時(shí)序

邏輯設(shè)計(jì)偽路徑(false path)

1.6 STA局限性

STA針對(duì)的是數(shù)字電路,和模擬電路相關(guān)的路徑無(wú)法通過(guò)STA驗(yàn)證

數(shù)字電路中產(chǎn)生的不定態(tài)在STA不會(huì)驗(yàn)證,這個(gè)需要通過(guò)仿真進(jìn)行仔細(xì)檢查確認(rèn)

電路中不同狀態(tài)機(jī)之間的同步需求不能通過(guò)STA來(lái)驗(yàn)證

對(duì)時(shí)鐘生成電路的驗(yàn)證無(wú)法通過(guò)STA完成

時(shí)序約束中會(huì)有例外情況,需要人工處理

2.

相關(guān)基礎(chǔ)概念

建立時(shí)間 setup time

是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以前,數(shù)據(jù)穩(wěn)定不變的最小時(shí)間Tsu

保持時(shí)間 hold up time

是指在觸發(fā)器的時(shí)鐘信號(hào)上升沿到來(lái)以后,數(shù)據(jù)穩(wěn)定不變的最小時(shí)間Th

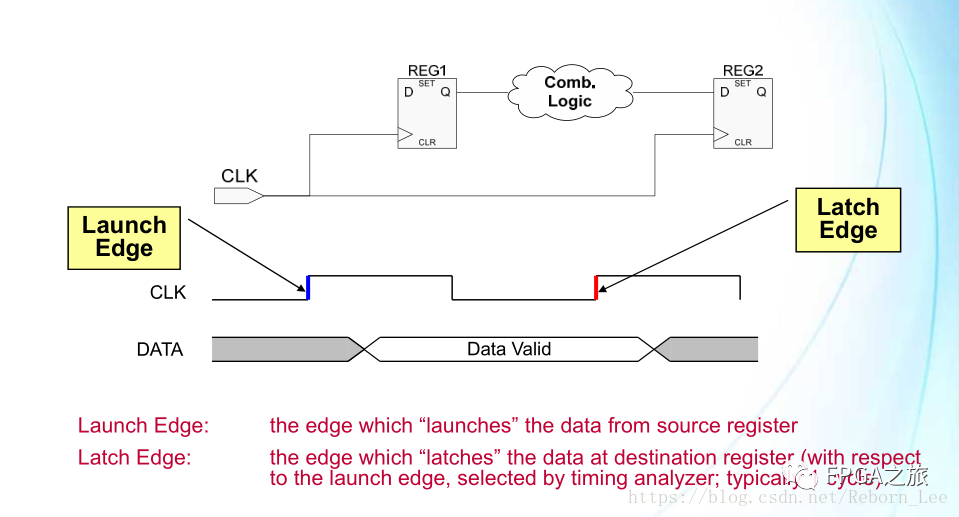

發(fā)射沿 Launch Edge

時(shí)序分析起點(diǎn),第一級(jí)寄存器數(shù)據(jù)變化的時(shí)鐘邊沿,也是靜態(tài)時(shí)序分析的起點(diǎn)

鎖存沿 Latch Edge

時(shí)序分析終點(diǎn),數(shù)據(jù)鎖存的時(shí)鐘邊沿,是靜態(tài)時(shí)序分析的終點(diǎn)

數(shù)據(jù)輸出延時(shí) Tco

數(shù)據(jù)輸出延時(shí)指的是當(dāng)時(shí)鐘觸發(fā)(一般可認(rèn)為是第一個(gè)寄存器的時(shí)鐘沿觸發(fā)時(shí)刻)開(kāi)始到有效數(shù)據(jù)輸出**(第一個(gè)寄存器的Q端數(shù)據(jù)開(kāi)始輸出(有可能變化,也有可能不變化))**的器件內(nèi)部所有延時(shí)的總和。

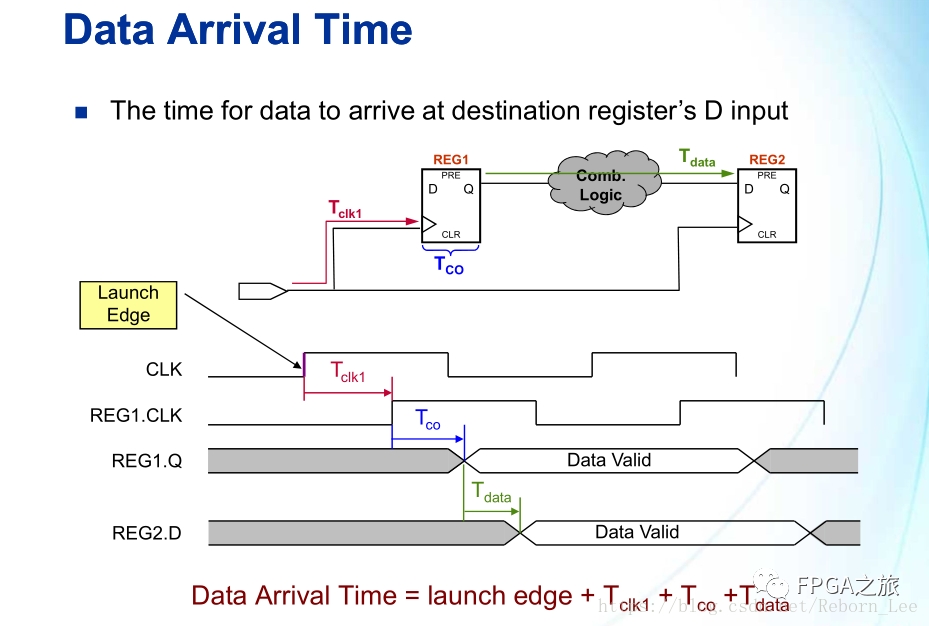

數(shù)據(jù)到達(dá)時(shí)間(數(shù)據(jù)路徑,Data Arrival Time)

輸入數(shù)據(jù)在有效時(shí)鐘沿后到達(dá)目的寄存器所需要的時(shí)間,可大致劃分為:時(shí)鐘沿到達(dá)第一級(jí)寄存器所需時(shí)間(Tclk1),寄存器內(nèi)部延遲時(shí)間(Tco),數(shù)據(jù)輸出后傳輸?shù)降诙?jí)寄存器所需時(shí)間(Tdata).

其中Tdata可細(xì)分為:

組合邏輯延時(shí)Tcomb_logic:數(shù)據(jù)經(jīng)過(guò)組合邏輯部分所需的時(shí)間;

線網(wǎng)延時(shí)Tnet:數(shù)據(jù)在線上傳輸所需的時(shí)間,一般較小可以忽略;

時(shí)鐘到達(dá)時(shí)間(時(shí)間路徑,Clock Arrival Time)

時(shí)鐘到達(dá)時(shí)間就是指時(shí)鐘從latch edge到達(dá)目的寄存器(destination register)輸入端所用的時(shí)間。

時(shí)鐘偏斜(Tskew)

指同一個(gè)時(shí)鐘沿(clk)和分別到達(dá)兩個(gè)寄存器所需的時(shí)間之間的差值(Tclk1和Tclk2的差值).

公式為:Tskew=Tclk2-Tclk1.

數(shù)據(jù)需求時(shí)間(Data Require Time)

細(xì)分為 (Setup-Data Require Time)( Hold-Data Require Time )

①Clock Arrival Time = Latch +Tclk2

因此 Data Required Time = Latch+Tclk2-Tsu (忽略建立不定態(tài))

②Clock Arrival Time = Latch +Tclk2.

因此 Data Required Time = Latch+Tclk2+Tsu (忽略保持不定態(tài))

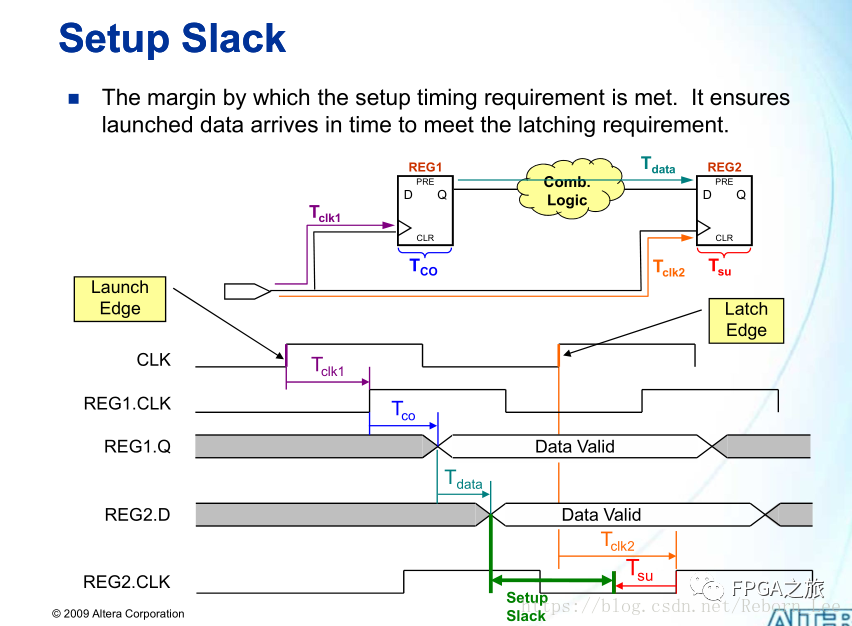

建立裕量(Setup Slack)

Setup Slack = (Latch Edge + Tclk2 - Tsu)-( Launch Edge + Tclk1 +Tco +Tdata)

(建立數(shù)據(jù)所需時(shí)間)Setup-Data Required Time = Latch Edge + Tclk2 - Tsu

(數(shù)據(jù)到達(dá)時(shí)間) Data Arrival Time = Lauch Edge + Tclk1 + Tco + Tdata

因此 Setup Slack = Setup-Data Required Time - Data Arrival Time

=(Latch Edge - Launch Edge)+(Tclk2-Tclk1)-(Tsu+Tco+Tdata)

= Tperiod +(Tclk2-Tclk1)-(Tsu + Tco+Tdata)

這個(gè)最終結(jié)果說(shuō)明了源寄存器與目的寄存器之間延遲 Tdata不能太長(zhǎng)的原因,延遲越長(zhǎng),slack越小。當(dāng)建立裕量為正時(shí),滿(mǎn)足時(shí)序要求,否則不滿(mǎn)足。

保持裕量(Hold Slack)

Hold Slack = Data Arrival Time - (Hold-Data Required Time)

同樣的可推導(dǎo):

(數(shù)據(jù)到達(dá)時(shí)間)Data Arrival Time = Launch Edge + Tclk1 + Tco + Tdata

(數(shù)據(jù)需求時(shí)間)Hold-Data Required Time = Latch Edge + Tclk2

Hold Slack = Launch Edge + Tclk1 + Tco + Tdata -(Latch Edge + Tclk2)

=-Tperiod +(Tclk1-Tclk2)+Tco+Tdata

從結(jié)果可以看出,當(dāng)源寄存器與目的寄存器之間延遲Tdata太短的話(huà),則保持裕量會(huì)很短,因此Hold Slack 越小。

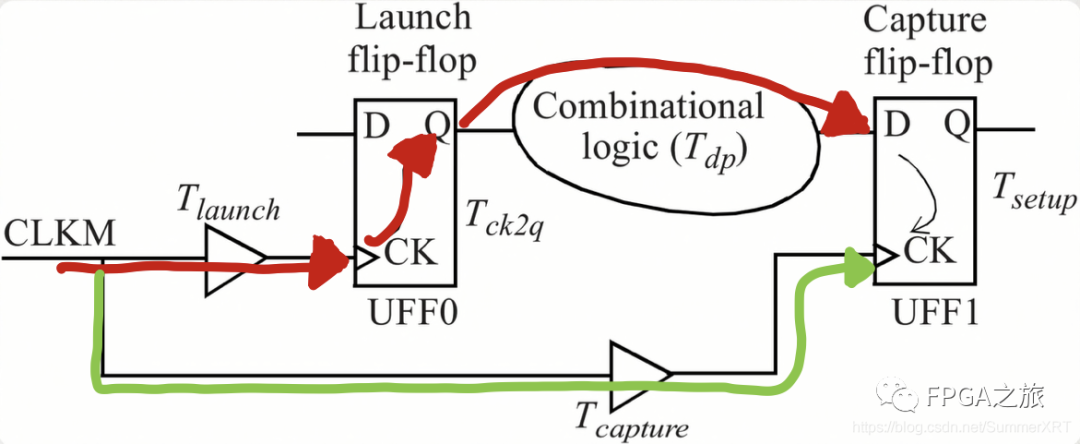

建立時(shí)間和保持時(shí)間的檢查

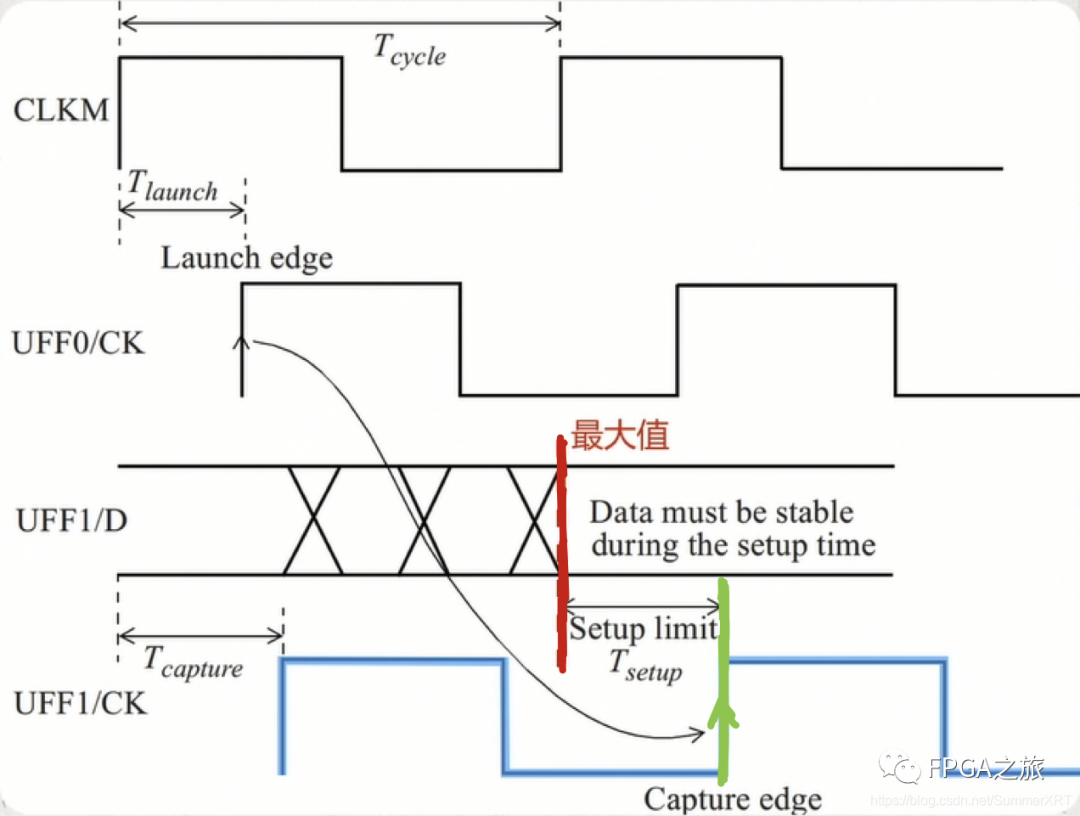

解釋圖中的符號(hào):

Tlaunch:時(shí)鐘源點(diǎn)到第一個(gè)觸發(fā)器的時(shí)鐘網(wǎng)絡(luò)延遲,也就是時(shí)鐘偏斜(skew);

Tcapture:為時(shí)鐘源點(diǎn)到第二個(gè)觸發(fā)器的時(shí)鐘網(wǎng)絡(luò)延遲,也就是時(shí)鐘偏斜(skew);

Tck2q:是觸發(fā)器的延遲,即D端到Q端的延遲,這是由觸發(fā)器本身的電氣特性所決定的;

Tcycle:是時(shí)鐘周期,即時(shí)鐘頻率 1\fclk;

Tdp:是第一個(gè)觸發(fā)器的輸出端到第二個(gè)觸發(fā)器的輸入端之間的組合邏輯電路部分的電路延遲;

解釋上圖,第二個(gè)觸發(fā)器要想滿(mǎn)足setup time,就必須要滿(mǎn)足:

上圖中綠色豎線為時(shí)鐘源點(diǎn)經(jīng)過(guò)延遲,到第二個(gè)觸發(fā)器的時(shí)間(對(duì)應(yīng)綠色路徑)

對(duì)應(yīng)紅色的路徑部分,經(jīng)過(guò)組合邏輯,到達(dá)第二觸發(fā)器的Q端,最晚只能到達(dá)上圖的紅色豎線部分,否則就沒(méi)辦法,滿(mǎn)足建立時(shí)間。

由此,我們可以推遲公式:

Tlaunch + Tck2q + Tdp ≤ Tcapture + Tcycle - Tsetup

因?yàn)門(mén)launch和Tcapture都表示為時(shí)鐘偏斜(clock skew),所以我們合并之后就可得:

建立時(shí)間約束:Tsetup ≤ Tcycle +Tskew - Tdp - Tck2q

保持時(shí)間約束:Thold ≤ Tdp + Tck2q

其中參數(shù)意義:

Tclock:也就是時(shí)鐘偏斜(clock skew);

Tck2q:是觸發(fā)器D端到Q端的延遲;

Tcycle:是時(shí)鐘周期,即時(shí)鐘頻率 1\fclk;

Tdp:是組合邏輯電路部分的電路延遲;

PS:這里可能你會(huì)覺(jué)得建立時(shí)間有點(diǎn)難記,我多啰嗦一句:

Tcycle + Tskew 是表示第二個(gè)觸發(fā)器的時(shí)鐘到達(dá)的時(shí)間;

Tdp + Tck2q是表示經(jīng)過(guò)第一個(gè)觸發(fā)器+組合邏輯到達(dá)的時(shí)間;

二者的差值就是建立時(shí)間最大的時(shí)間要求

解決建立時(shí)間與保持時(shí)間不滿(mǎn)足的問(wèn)題

1.建立時(shí)間不滿(mǎn)足

當(dāng)建立時(shí)間不滿(mǎn)足時(shí),即Tsetup值要大于實(shí)際的Tcycle +Tskew - Tdp - Tck2q,為了滿(mǎn)足建立時(shí)間:

可以通過(guò)改進(jìn)工藝,采取具有更小的Tsetup值的芯片;

采用延遲更低的觸發(fā)器,降低Tck2q;

增大時(shí)鐘周期Tcycle和時(shí)鐘偏斜Tskew,但這會(huì)降低電路的性能;

盡量減小兩個(gè)觸發(fā)器之間的組合邏輯電路的使用,從而降低Tck2q。

2.保持時(shí)間不滿(mǎn)足

當(dāng)保持時(shí)間不滿(mǎn)足時(shí),也就是Thold要小于Tdp + Tck2q,可以通過(guò):

理論上,可以增加Tdp和Tck2q來(lái)解決,也就是增加觸發(fā)器的D端到Q端的延時(shí),以及兩級(jí)觸發(fā)器之間的組合邏輯電路部分。

目前大部分芯片的Thold時(shí)間都可以做到0ns。所以當(dāng)保持時(shí)間不滿(mǎn)足時(shí),通常采用的做法是在傳輸路徑上插入buffer,在不影響邏輯功能前提下,只具有增加延遲的作用。

PS:尤其注意,保持時(shí)間Thold和時(shí)鐘頻率之間是沒(méi)有關(guān)系,故降低時(shí)鐘速度不能解決保持時(shí)間不滿(mǎn)足的問(wèn)題,很多面試題喜歡在這里挖坑。

恢復(fù)時(shí)間 Recovery time

是指異步控制信號(hào)(如寄存器的異步清除和置位控制信號(hào))在“下個(gè)時(shí)鐘沿”來(lái)臨之前變無(wú)效的最小時(shí)間長(zhǎng)度。

去除時(shí)間 Removal time

是指異步控制信號(hào)(如寄存器的異步清除和置位控制信號(hào))在“有效時(shí)鐘沿”之后變無(wú)效的最小時(shí)間長(zhǎng)度。

時(shí)序路徑

每個(gè)時(shí)序路徑都有一個(gè)起點(diǎn)和終點(diǎn)。一般起點(diǎn)是時(shí)序單元的時(shí)鐘引腳 或者設(shè)計(jì)的輸入端口;終點(diǎn)是時(shí)序單元的數(shù)據(jù)輸入引腳或者 設(shè)計(jì)的輸出端口。所以一共有四種時(shí)序路徑。

恢復(fù)時(shí)間 Recovery time

是指異步控制信號(hào)(如寄存器的異步清除和置位控制信號(hào))在“下個(gè)時(shí)鐘沿”來(lái)臨之前變無(wú)效的最小時(shí)間長(zhǎng)度。

去除時(shí)間 Removal time

是指異步控制信號(hào)(如寄存器的異步清除和置位控制信號(hào))在“有效時(shí)鐘沿”之后變無(wú)效的最小時(shí)間長(zhǎng)度。

時(shí)序路徑

每個(gè)時(shí)序路徑都有一個(gè)起點(diǎn)和終點(diǎn)。一般起點(diǎn)是時(shí)序單元的時(shí)鐘引腳 或者設(shè)計(jì)的輸入端口;終點(diǎn)是時(shí)序單元的數(shù)據(jù)輸入引腳或者 設(shè)計(jì)的輸出端口。所以一共有四種時(shí)序路徑。

名詞解釋?zhuān)?/p>

發(fā)射沿(launch edge):有效時(shí)鐘的第一個(gè)上升沿;

采樣沿(latch edge):有效時(shí)鐘的第二個(gè)上升沿;

采樣沿和發(fā)射沿差值可以粗略認(rèn)為是1個(gè)時(shí)鐘周期(不考慮時(shí)鐘抖動(dòng)jitter)。

Tclk1:時(shí)鐘源扇出信號(hào)到寄存器1(REG1)的時(shí)鐘端所需時(shí)間;

Tclk2:時(shí)鐘源扇出信號(hào)到寄存器2(REG2)的時(shí)鐘端所需時(shí)間;

所以時(shí)鐘源的布局布線很重要,這就是為什么FPGA中推薦用PLL輸出時(shí)鐘,而不是自己進(jìn)行時(shí)鐘分頻。

Tco:寄存器時(shí)鐘輸出延遲,即有效時(shí)鐘輸入到輸出之間的延遲。

Tdata:2個(gè)寄存器之間組合路徑延遲和布局布線延遲。

Tc:時(shí)鐘周期大小(Tclk)。

Ts:建立時(shí)間大小;

Th:保持時(shí)間大小;

Thold_slack:保持時(shí)間余量(也就是要大于0);

Tsetup_slack:建立時(shí)間余量(也就是大于0)。

建立時(shí)間:

采樣沿到達(dá)時(shí)間:Tlatch = Tc + Tclk2;

第一次數(shù)據(jù)到達(dá)時(shí)間:Tarrive = Tclk1 + Tco + Tdata;

建立時(shí)間大小:Ts = Tlatch - Tarrive = Tc + Tclk2 - Tclk1 - Tco - Tdata = Tc + Tdelta - T1.

其中,Tdelta代表Tskew,也就是2個(gè)寄存器之間時(shí)鐘到達(dá)差值,T1代表從REG1到REG2數(shù)據(jù)接收端的整個(gè)時(shí)間延遲,當(dāng)然,不化簡(jiǎn)也是可以的。

保持時(shí)間:

第一次采樣沿到達(dá)時(shí)間:Tlatch = Tc + Tclk2;

第二次數(shù)據(jù)到來(lái)時(shí)間:Tdata2 = Tclk1 + Tco + Tdata + Tc(Tdata_valid) ;

保持時(shí)間大小:Th = Tdata2 - Tlatch = Tclk1 + Tco + Tdata - Tclk2 = T1 - Tdelta。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<

電子技術(shù)應(yīng)用專(zhuān)欄作家 FPGA之旅

原文鏈接:https://mp.weixin.qq.com/s/PX9FAo4skTAOR7NQqiqvmA