筆者經歷過一個項目,整個系統的功耗達到了100w,而單片FPGA的功耗估計得到為20w左右,有點過高了,功耗過高則會造成發熱量增大,溫度高最常見的問題就是系統重啟,另外對FPGA內部的時序也不利,導致可靠性下降。其它硬件電路的功耗是固定的,只有FPGA的功耗有優化的余地,因此硬件團隊則極力要求筆者所在的FPGA團隊盡量多做些低功耗設計。筆者項目經歷尚淺,還是第一次正視功耗這碼事兒,由于項目時間比較緊,而且xilinx方面也比較重視這個項目,因此當時有xilinx的工程師過來對我們做了些培訓,并且專門請了美國總部的專家過來與我們協同進行設計功耗估計,還是比較給力的。

以下是筆者在這比較短的時間內學習到的一些關于功耗估計和如何進行低功耗設計的知識:

功耗分析

整個FPGA設計的總功耗由三部分功耗組成:1. 芯片靜態功耗;2. 設計靜態功耗;3. 設計動態功耗。

l芯片靜態功耗:FPGA在上電后還未配置時,主要由晶體管的泄露電流所消耗的功耗

l設計靜態功耗:當FPGA配置完成后,當設計還未啟動時,需要維持I/O的靜態電流,時鐘管理和其它部分電路的靜態功耗

l設計動態功耗:FPGA內設計正常啟動后,設計的功耗;這部分功耗的多少主要取決于芯片所用電平,以及FPGA內部邏輯和布線資源的占用

顯而易見,前兩部分的功耗取決于FPGA芯片及硬件設計本身,很難有較大的改善。可以優化是第3部分功耗:設計動態功耗,而且這部分功耗占總功耗的90%左右,因此所以降低設計動態功耗是降低整個系統功耗的關鍵因素。上面也提到過功耗較大會使FPGA發熱量升高,那有沒有一個定量的分析呢?答案當然是有,如下式:

Tjmax > θJA * PD + TA

其中Tjmax表示FPGA芯片的最高結溫(maximum juncTIon temperature);θJA表示FPGA與周圍大氣環境的結區熱阻抗(JuncTIon to ambient thermal resistance),單位是°C/W;PD表示FPGA總功耗(power dissipaTIon),單位是W;TA表示周圍環境溫度。

以XC7K410T-2FFG900I系列芯片為例,θJA = 8.2°C/W,在TA = 55°C的環境中,想要結溫Tjmax不超過100°C的情況下,可以推算FPGA的總功耗:PD < (Tjmax – TA)/θJA=(100 - 55)/8.2=5.488W,之前估算的20W與之相差太遠,因此優化是必不可少的:

1.降低θJA:熱阻抗取決于芯片與環境的熱傳導效率,可通過加散熱片或者風扇減小熱阻抗

功耗估計

在講解低功耗設計之前,介紹一下xilinx的功耗估計工具XPE(Xilinx Power EsTImator),XPE主要是在項目初期,處于系統設計,RTL代碼并未完善階段功耗估計時使用。大家可以在xilinx官網上下載到:http://www.xilinx.com/power,它是一個基于EXCEL的工具,如圖2所示,功能做的十分豐富,感嘆EXCEL也未免太強大了吧。

在設計完成綜合實現后,則可以使用vivado自帶的功耗分析工具進行精確計算功耗。打開綜合實現后的設計,點擊report power即可得到功耗分析的結果,如圖3,4所示。

低功耗設計

關于FPGA低功耗設計,可從兩方面著手:1. 算法優化;2. FPGA資源使用效率優化。

1.算法優化

算法優化可分為兩個層次說明:實現結構和實現方法

首先肯定需要設計一種最優化的算法實現結構,設計一種最優化的結構,使資源占用達到最少,當然功耗也能降到最低,但是還需要保證性能,是FPGA設計在面積和速度上都能兼顧。比如在選擇采用流水線結構還是狀態機結構時,流水線結構同一時間所有的狀態都在持續工作,而狀態機結構只有一個狀態是使能的,顯而易見流水線結構的功耗更多,但其數據吞吐率和系統性能更優,因此需要合理選其一,使系統能在面積和速度之間得到平衡;

另一個層面是具體的實現方法,設計中所有吸收功耗的信號當中,時鐘是罪魁禍首。雖然時鐘可能運行在?100?MHz,但從該時鐘派生出的信號卻通常運行在主時鐘頻率的較小分量(通常為?12%~15%)。此外,時鐘的扇出一般也比較高。這兩個因素顯示,為了降低功耗,應當認真研究時鐘。?首先,如果設計的某個部分可以處于非活動狀態,則可以考慮禁止時鐘樹翻轉,而不是使用時鐘使能。時鐘使能將阻止寄存器不必要的翻轉,但時鐘樹仍然會翻轉,消耗功率。其次,隔離時鐘以使用最少數量的信號區。不使用的時鐘樹信號區不會翻轉,從而減輕該時鐘網絡的負載。

2.資源使用效率優化

資源使用效率優化是介紹一些在使用FPGA內部的一些資源如BRAM,DSP48E1時,可以優化功耗的方法。FPGA動態功耗主要體現為存儲器、內部邏輯、時鐘、I/O消耗的功耗。

其中存儲器是功耗大戶,如xilinx FPGA中的存儲器單元Block RAM,因此在這邊主要介紹對BRAM的一些功耗優化方法。

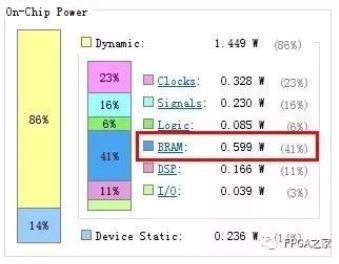

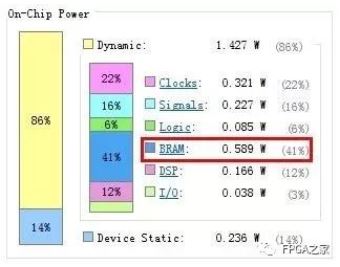

如圖5中實例,雖然BRAM只使用了7%,但是其功耗0.601W占了總設計的42%,因此優化BRAM的功耗能有效地減小FPGA的動態功耗。

下面介紹一下優化BRAM功耗的方法:

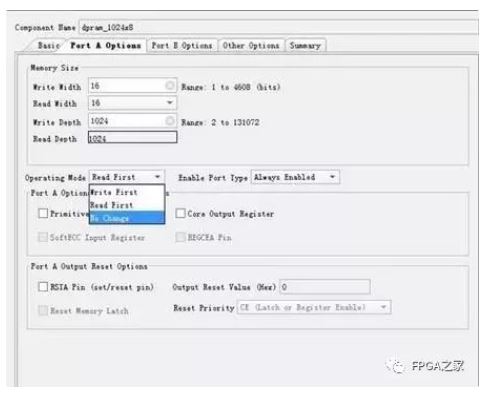

(1) 使用“NO CHANGE”模式:在BRAM配置成True Dual Port時,需要選擇端口的操作模式:“Write First”,“Read First” or “NO CHANGE”,避免讀操作和寫操作產生沖突,如圖6所示;其中“NO CHANGE”表示BRAM不添加額外的邏輯防止讀寫沖突,因此能減少功耗,但是設計者需要保證程序運行時不會發生讀寫沖突。

圖5中的功耗是設置成“Write First”時的,圖7中是設置成“NO CHANGE”后的功耗,BRAM的功耗從0.614W降到了0.599W,因為只使用了7%的BRAM,如果設計中使用了大量的BRAM,效果能更加明顯。

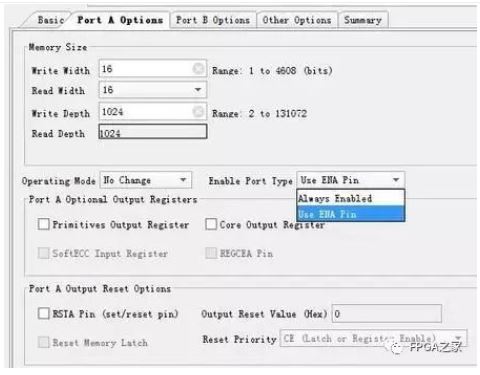

(2)控制“EN”信號:BRAM的端口中有clock enable信號,如圖8所示,在端口設置中可以將其使能,模塊例化時將其與讀/寫信號連接在一起,如此優化可以使BRAM在沒有讀/寫操作時停止工作,節省不必要的功耗。

如圖9所示為控制“EN”信號優化后的功耗情況,BRAM功耗降到了0.589W

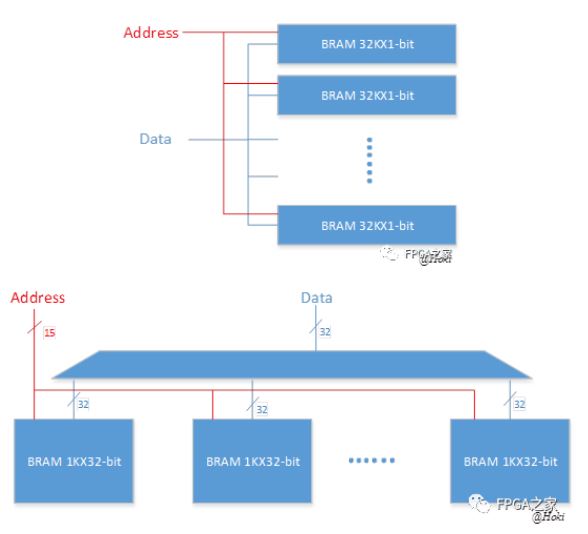

(3)拼深度:當設計中使用了大量的存儲器時,需要多塊BRAM拼接而成,如需要深度32K,寬度32-bit,32K32Bit的存儲量,但是單塊BRAM如何配置是個問題?7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K1-bit或者1K*32-bit,多塊BRAM拼接時,前者是“拼寬度”(見圖10),后者是“拼深度”(見圖11)。兩種結構在工作時,“拼寬度”結構所有的BRAM需要同時進行讀寫操作;而“拼深度”結構只需要其中一塊BRAM進行讀寫,因此在需要低功耗的情況下采用“拼深度”結構,

注:“拼深度”結構需要額外的數據選擇邏輯,增加了邏輯層數,為了降低功耗即犧牲了面積又犧牲了性能。

更多信息可以來這里獲取==>>電子技術應用-AET<<