3月5日消息,日立當地時間2月27日稱該企業已開發出了一種高靈敏度半導體缺陷檢測技術,可通過機器學習的輔助檢出10nm及更小尺寸的微缺陷。這項技術已在二月末的SPIE先進光刻與圖案化2025學術會議上展出。

隨著對高性能芯片的需求不斷增加,半導體制造商對生產中的質量控制愈發重視;而制程的微縮也意味著能直接影響性能的缺陷尺寸門檻逐漸降低,對缺陷檢測靈敏度的要求進一步提升。日立的這一技術就是在該背景下應運而生的。

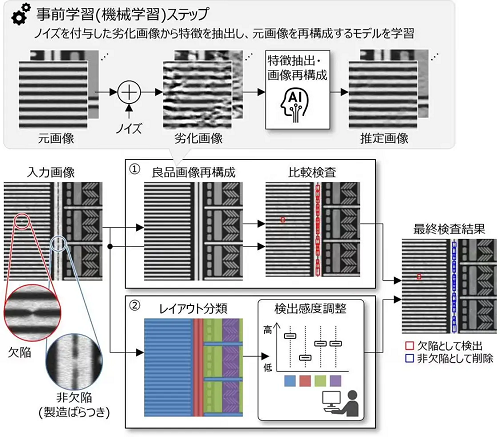

日立的機器學習缺陷檢測技術主要包含兩大部分,即圖像重建對比和過度檢測抑制:

圖像重建對比:檢測系統首先通過大量添加噪點的“人造”缺陷圖像學習微缺陷的數據特征;實際使用時對掃描電鏡照片盡量進行無缺陷版本重建,并對原始圖像和重建圖像進行對比,從而檢出缺陷。

過度檢測抑制:由于先進半導體制程的微縮,差異化功能電路和缺陷在圖像上的區別逐漸模糊,而機器學習檢測系統可對電路布局進行分類,并根據電路特征調整靈敏度,可減少90%的過度檢測。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。