3 月 20 日消息,中國科學技術大學于 3 月 10 日發布博文,宣布其微電子學院程林教授團隊聯合澳門大學羅文基教授團隊,在超低溫量子接口基準電路研究中取得重大進展。

該研究首次提出了無需修調的超低溫低功耗 CMOS 電壓基準,可在極端溫度范圍內實現高精度穩定輸出,相關成果發表于固態電路領域頂級期刊《Journal of Solid-State Circuits》(JSSC)。該技術為量子計算的規模化應用提供了關鍵支撐。

技術背景

援引博文介紹,大多數量子計算機(如超導量子計算機)為了減少熱噪聲對量子比特的影響,需在接近絕對零度的環境下運行,因此量子計算機需要大量高保真量子位和控制接口電路,以在室溫的經典域和低溫的量子域之間傳遞信號。

在各類接口電路模塊中,基準電路至關重要。為了確保在初始測試、熱過渡和系統異常等工作條件下的可靠性,電壓基準必須在稀釋制冷機到外界環境的溫度范圍內(從 300K 到 4K)保持穩定輸出特性,這要求其對溫度波動和工藝偏差具有極低的敏感性。

然而,標準 CMOS 器件在超低溫下會表現出閾值電壓漂移、非線性效應加劇、扭結效應等問題,這使得量子接口基準電路的極端低溫環境適應性面臨嚴峻挑戰。因此,設計高魯棒性、適用于超低溫環境的量子接口基準電路,將有助于解決量子計算大規模應用中的關鍵技術難題。

項目突破

研究團隊提出了一種創新性解決方案,設計了一種無需修調的超低溫低功耗 CMOS 電壓基準量子接口電路,提出了同時實現溫度和工藝的自補償的技術。

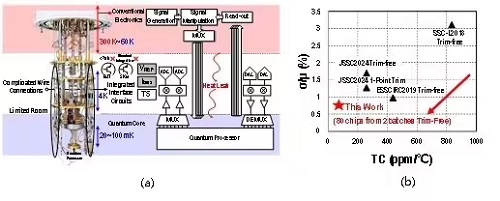

圖 (a) 量子接口芯片的工作環境;圖 (b) 溫度與工藝精度相較于前沿研究展現出顯著優勢。

該基準電路能在 300 K 至 4 K 的超寬溫度范圍內實現高精度電壓輸出,并展現出優異的魯棒性。

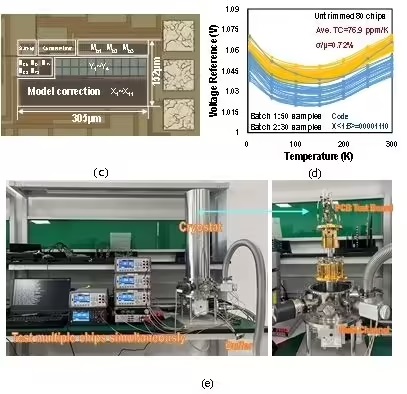

該設計采用標準 CMOS 180 nm 工藝,共測試了兩個批次的 80 枚芯片(圖(c))。測試結果如圖 (d) 所示,僅需單次模型校準,即可實現跨批次免修調操作,基準的平均溫度系數(TC)為 76.9 ppm / K,并且電壓波動僅為 0.72%,具有很高的溫度與工藝精度。

圖 (c) 芯片顯微鏡照片;圖 (d) 測試的兩批次共 80 顆未修調芯片的溫度曲線;圖 (e) 稀釋制冷機和自動計數系統的測量環境。

在 300 K 到 4 K 工作范圍內僅消耗 195-304 nW 功耗,輸出電壓的均值為 1.045 V。該電壓基準在標準 CMOS 工藝下實現了納瓦級的超低功耗,并且對工藝、電壓和溫度變化(PVT)具有出色的穩定性。

它能夠以較低的成本被集成到量子接口電路以及用于超低溫環境下的宇航探測等芯片中,為這些超低溫應用提供了可靠的解決方案。