光纖陀螺是激光陀螺的一種,是慣性技術(shù)和光電子技術(shù)緊密結(jié)合的產(chǎn)物。它利用Sagnac干涉效應(yīng),用光纖構(gòu)成環(huán)形光路,并檢測(cè)出隨光纖環(huán)的轉(zhuǎn)動(dòng)而產(chǎn)生的兩路超輻射光束之間的相位差,由此計(jì)算出光纖環(huán)旋轉(zhuǎn)的角速度。光纖陀螺儀" title="光纖陀螺儀">光纖陀螺儀主要由兩個(gè)部分組成。伺服于表頭的調(diào)制解調(diào)電路根據(jù)輸入的電信號(hào),經(jīng)過(guò)相應(yīng)的變換后形成反饋信號(hào)送至表頭的相位調(diào)制器中。在實(shí)際的應(yīng)用過(guò)程中,相應(yīng)的調(diào)制解調(diào)電路應(yīng)該根據(jù)溫度、振動(dòng)等情況做出相應(yīng)的改變,才能最大限度地保證陀螺的精度要求。本文設(shè)計(jì)了一種基于FPGA" title="FPGA">FPGA的測(cè)試系統(tǒng),模擬光纖陀螺儀的表頭,并檢測(cè)調(diào)制解調(diào)電路的性能。

模擬表頭" title="模擬表頭">模擬表頭的基本原理及結(jié)構(gòu)

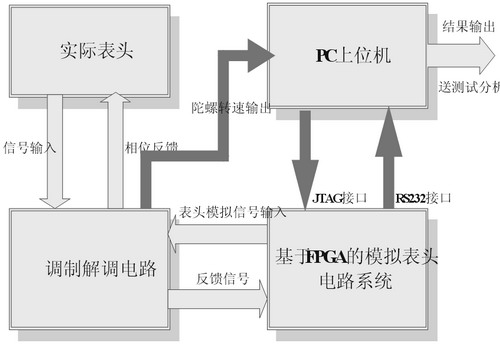

表頭的主要功能是將Sagnac效應(yīng)產(chǎn)生的光程差所引起的相位變化通過(guò)回路耦合器轉(zhuǎn)換為光功率的變化,再通過(guò)探測(cè)器探測(cè)后以電信號(hào)的形式輸出至調(diào)制解調(diào)電路中。數(shù)字閉環(huán)光纖陀螺儀系統(tǒng)結(jié)構(gòu)見(jiàn)圖1。從調(diào)制解調(diào)電路中采樣來(lái)的原始參數(shù)值,經(jīng)過(guò)模擬表頭內(nèi)數(shù)字信號(hào)處理,可將輸入調(diào)制解調(diào)電路的實(shí)際表頭信號(hào)還原出來(lái)。得到初始還原值之后,通過(guò)在模擬表頭中進(jìn)行修改、加載不同類型的參數(shù)值,從而檢測(cè)調(diào)制解調(diào)電路中相應(yīng)的性能指標(biāo)。

圖1 數(shù)字閉環(huán)光纖陀螺儀系統(tǒng)結(jié)構(gòu)圖

本文所設(shè)計(jì)的模擬表頭系統(tǒng)遵循了一般數(shù)字閉環(huán)光纖陀螺系統(tǒng)的基本原理,在系統(tǒng)結(jié)構(gòu)上發(fā)生了變化。調(diào)制解調(diào)電路在本系統(tǒng)中處于被動(dòng)地位,而表頭作為系統(tǒng)的主體。同時(shí),用一個(gè)自主設(shè)計(jì)的電路系統(tǒng)代替了光纖陀螺儀的表頭部分。模擬表頭及其測(cè)試系統(tǒng)的結(jié)構(gòu)如圖2所示。

圖2 模擬表頭及其測(cè)試系統(tǒng)框圖

圖中,PC上位機(jī)的工作十分重要,它不僅控制調(diào)制解調(diào)電路和模擬表頭系統(tǒng)的協(xié)同工作,而且要將所采集來(lái)的數(shù)據(jù)進(jìn)行分析整理,并完成關(guān)鍵的軟件編寫和植入工作。

模擬表頭系統(tǒng)的硬件設(shè)計(jì)

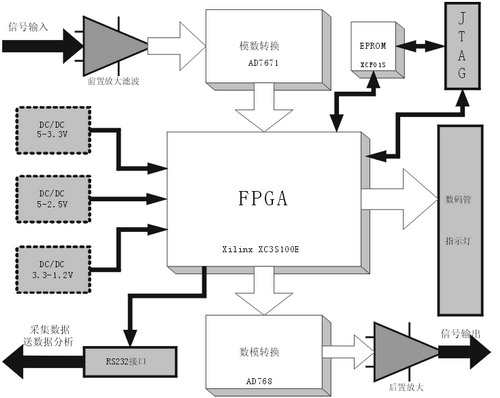

根據(jù)理論分析,本文設(shè)計(jì)出基于FPGA的模擬表頭硬件系統(tǒng),如圖3所示。

圖3 基于FPGA的光纖陀螺模擬表頭硬件連接圖

在這個(gè)閉環(huán)系統(tǒng)中,需要采集的主要信號(hào)是調(diào)制解調(diào)電路中的相位反饋信號(hào)。根據(jù)反饋信號(hào)的特點(diǎn),選用運(yùn)算量不大

但處理速度快的FPGA作為信號(hào)處理的主要器件。在本方案中,考慮到成本和實(shí)際運(yùn)算量,選取XC3S100E" title="XC3S100E">XC3S100E FPGA芯片。

本系統(tǒng)采用±5V穩(wěn)壓直流電源供電。經(jīng)過(guò)計(jì)算,本系統(tǒng)的功耗在5W以下,故直流電源的輸出電流需達(dá)到1A。根據(jù)FPGA及其外圍電路的供電要求,需要設(shè)置三個(gè)DC/DC模塊:分別是5V轉(zhuǎn)3.3V,5V轉(zhuǎn)2.5V和3.3V轉(zhuǎn)1.2V。分別選擇了MAX651、ADP3333和LTC3406用于電壓轉(zhuǎn)換。另外,3.3V電源還用作驅(qū)動(dòng)ADC、數(shù)碼管、運(yùn)算放大器等器件。

XC3S100E芯片具有較好的性價(jià)比,它具有2160個(gè)邏輯單元,100000個(gè)系統(tǒng)門資源,最大的I/O口數(shù)目是108。對(duì)本系統(tǒng)來(lái)說(shuō),完全能滿足16位輸入/輸出、數(shù)碼管指示燈等顯示模塊、與上位機(jī)通訊以及其他控制信號(hào)的接口需要。系統(tǒng)中另外配置了一塊和FPGA相匹配的EPROM-XCF01S,用來(lái)提供邏輯芯片在開機(jī)后目標(biāo)程序的加載。

A/D和D/A轉(zhuǎn)換分別采用AD7671和AD768兩款芯片。AD7671具有最高可達(dá)1MSPS的采樣速率,逐次逼近型高速高精度,并行傳輸?shù)哪?shù)轉(zhuǎn)換器,并能達(dá)到16bit的分辨率,而且無(wú)失碼,最大積分非線性誤差(INL)僅為±2.5LSB,能夠很好地滿足本系統(tǒng)要求。AD768是一款具有16位精度,最高可達(dá)40MSPS采樣速率的高速DAC。它的響應(yīng)時(shí)間非常短,轉(zhuǎn)換速度快并與高速的ADC有很強(qiáng)的適配能力。

在提取初始參數(shù)時(shí),考慮到陀螺信號(hào)比較弱,在A/D轉(zhuǎn)換之前的設(shè)計(jì)采用了弱信號(hào)檢測(cè)方法,對(duì)信號(hào)進(jìn)行濾波、整形并放大,在最大限度保證無(wú)失真的前提下將原始信號(hào)提取出來(lái),并轉(zhuǎn)換為ADC可以分辨的信號(hào)輸出。

模擬表頭系統(tǒng)的軟件設(shè)計(jì)

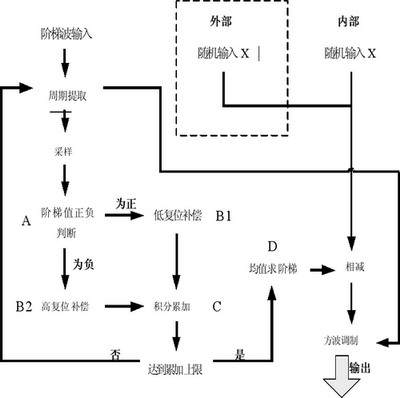

根據(jù)閉環(huán)光纖陀螺儀表頭的基本原理,實(shí)際表頭輸出的信號(hào)為周期恒定的梳狀波。波形中奇偶周期的電壓差值表示表頭光纖環(huán)中兩束光的光程差所對(duì)應(yīng)的電信號(hào)量。調(diào)制解調(diào)電路產(chǎn)生的用于反饋的階梯波作為實(shí)際表頭的輸入。因此,模擬表頭軟件要解決的問(wèn)題有兩個(gè):一個(gè)是產(chǎn)生一個(gè)象征光程差(根據(jù)光程差就能計(jì)算出角速度ω)的隨機(jī)數(shù)X,一個(gè)是利用調(diào)制解調(diào)電路送來(lái)的階梯波進(jìn)行計(jì)算,提取階梯值S及其周期。

核心算法的軟件設(shè)計(jì)流程如圖4所示。

圖4 模擬表頭核心算法的軟件流程圖

在流程圖中,模塊A用于判斷階梯值的正負(fù)。根據(jù)實(shí)際解調(diào)電路特性,反饋信號(hào)是通過(guò)對(duì)解調(diào)電路產(chǎn)生的階梯值累加,再經(jīng)方波調(diào)制得到的,累加過(guò)程中采用了高低復(fù)位操作。因此,在對(duì)階梯波采樣值作進(jìn)一步處理前,有必要判斷階梯值正負(fù)。這里通過(guò)設(shè)置計(jì)數(shù)器,對(duì)同周期相鄰采樣值進(jìn)行多次作差比較來(lái)判斷其正負(fù),避免了高低復(fù)位操作引起的前后采樣值突變對(duì)判斷結(jié)果的影響。

模塊B是高低復(fù)位判斷和補(bǔ)償模塊。該模塊通過(guò)比較同周期前后采樣值的大小來(lái)實(shí)現(xiàn)復(fù)位點(diǎn)判斷,然后對(duì)經(jīng)過(guò)復(fù)位的采樣值進(jìn)行相應(yīng)的補(bǔ)償操作。

在Xilinx ISE" title="ISE">ISE8.2的平臺(tái)上,對(duì)Verilog HDL編寫的模擬表頭作了功能仿真。采用常用的ModelSim SE 6.2對(duì)Testbench模塊進(jìn)行仿真,用以檢測(cè)程序設(shè)計(jì)中計(jì)算和邏輯的正確性。仿真模塊設(shè)置主時(shí)鐘MCLK周期為10ns,高低電平持續(xù)時(shí)間相同。每隔50個(gè)時(shí)鐘周期進(jìn)行一次采樣,累加16個(gè)采樣值求一次階梯。仿真時(shí)間設(shè)置為35000ns,RSTB為主復(fù)位信號(hào),ADBUSY與ADCNVST為ADC控制信號(hào),CLOCK為DAC控制信號(hào)。

本方案對(duì)隨機(jī)數(shù)X和輸入INDATA在幾種極限情況下的仿真結(jié)果進(jìn)行了驗(yàn)證,用以檢測(cè)表頭程序設(shè)計(jì)的正確性。

結(jié)語(yǔ)

根據(jù)以上的軟硬件設(shè)計(jì),可設(shè)計(jì)出能夠模擬光纖陀螺儀表頭行為的模擬表頭系統(tǒng)。測(cè)試時(shí),將實(shí)際的光纖陀螺儀表頭和調(diào)制解調(diào)電路與設(shè)計(jì)電路系統(tǒng)對(duì)接,就能得到所期望的波形和數(shù)據(jù)。將模擬表頭的隨機(jī)輸入數(shù)(代表角速度ω)與被檢測(cè)的調(diào)制解調(diào)電路輸出作對(duì)比,可有效檢驗(yàn)出被測(cè)調(diào)制解調(diào)電路的性能。

參考文獻(xiàn):

1.Heckman, D.W.; Baretela,M.; Interferometric Fiber Optic Gyro Technology (IFOG), Aerospace and Electronic

Systems Magazine, IEEE, Volume 15,? Issue 12,? Dec. 2000 Page(s):23 -28

2.王威, 基于DSP、FPGA閉環(huán)光纖陀螺儀的研究與實(shí)現(xiàn).[碩士學(xué)位論文]. 哈爾濱: 哈爾濱工程大學(xué), 2005

3.王新國(guó), 許化龍. 全數(shù)字閉環(huán)光纖陀螺測(cè)試系統(tǒng)的軟硬件設(shè)計(jì)[J]. 戰(zhàn)術(shù)導(dǎo)彈控制技術(shù), 2005,2: 63~66

4.張忠鋼. 基于FPGA的光纖陀螺檢測(cè)技術(shù)研究. [碩士學(xué)位論文]. 北京: 北京航空航天大學(xué), 2003

5.張明. Verilog-HDL實(shí)用教程[M]. 成都: 電子科技大學(xué)出版社, 1999