1 并行流水結構FIR的原理

在用FPGA或專用集成電路實現數字信號處理算法時,計算速度和芯片面積是兩個相互制約的主要問題。實際應用FIR濾波器時,要獲得良好的濾波效果,濾波器的階數可能會顯著增加,有時可能會多達幾百階。因此,有必要在性能和實現復雜性之間做出選擇,也就是選擇不同的濾波器實現結構。這里運用

在關鍵路徑插入寄存器的流水線結構是提高系統吞吐率的一項強大的實現技術,并且不需要大量重復設置硬件。流水線的類型主要分為兩種:算術流水線和指令流水線。對FPGA設計,邏輯功能是面向特定應用的,因此,采用需要較少額外控制邏輯的算術流水結構。 流水線結構就意味著將數字處理算法分割成時間上前后相連的多個處理片段.并且在段與段之間加信號寄存器來緩沖。這些段和段之間的緩沖就構成了流水線。系統原來的運算量被分割成k個部分,分別由流水線的k個段來外理。一旦前面的任務通過了流水線的第一段,新的任務就可以進入流水線。設系統不加流水時的延時是D,則加上流水后,每隔D/k個時間單位就可以啟動新的任務。要實現流水線的性能提升應滿足3個條件:

①運算量均勻分成延時一致的k個部分;

②輸人數據有大量重復的運算;

③重復的運算前后沒有相關性。

并行結構就是以重復相同的結構,對同時滿足并行運算條件的并行算法在硬件上進行實現的結構。并行結構運用起來的主要難點如下:一,并行結構占用更多的面積。二,相互并行的各計算部分在相互交換數據時,需要額外的控制和互聯結構。但是,在芯片工藝尺寸不斷減小的今天,并行結構成為設計高速、低延時數據處理系統的首選。控制和互聯結構的復雜性取決于算法和對算法的劃分方法。FIR濾波器本身就適合并行處理,但是對于占用時間和芯片面積都很大的乘法器來說,用全并行來實現FIR濾波器是不經濟的。

FIR濾波器以其設計簡單、穩定性好、方便實現、線性相位等優點往往成為首選,甚至是唯一的選擇。FIR濾波器用差分方程表示為:

![]()

FIR濾波器直接型結構如圖1。

2 實現方法

現場可編程門陣列(FPGA)具有體系結構和邏輯單元配置靈活、集成度高以及設計開發周期短等優點,因此,選用FPGA來驗證并實現本濾波器結構。VHDL是一種硬件描述語言,主要用于描述數字系統的結構、行為、功能和接口,與FPGA相結合后,表現出更加強大與靈活的數字系統設計能力。用VHDL完成數字系統的功能描述,用FPGA來實現是一種實用方便的軟、硬件結合方式。從硬件描述語言到FPGA配置數據文件是由綜合工具以及布局、布線工具來完成的。數字系統的功能最終能否實現以及性能如何,取決于數字系統的算法結構,也取決于綜合工具、布局和布線工具,還有器件性能。但是,如果數字系統的算法設計不好,就會有更多的設計反復。這里對FIR濾波器提出一種處理時間和所用芯片面積可以互換的結構,在最初的設計時,就能對其處理能力有所估計,減少了設計的反復。

對于FIR濾波器,Xilinx提供了兩個軟核,一個是基于分布式運算的,另一個是基于單路的乘加運算。對于大階數、高采樣率的濾波器,這兩種濾波器結構都不太適合。

為了提高FIR濾波器的吞吐量,可用并行加流水線的結構來實現FIR濾波器,如圖2所示。流水結構用于提高吞吐量率,并行結構可以減小處理延時。利用流水和并行結構調整濾波器性能使其滿足實際應用要求。這里實現三級流水和二路并行的FIR濾波器。三級流水分別對應取數、乘法和累加。主要由雙口RAM、乘法器、累加器、控制邏輯和流水線間的寄存器組成,還有數據寫入模塊(圖中未畫)。

并行流水線結構的FIR濾波器" src="http://files.chinaaet.com/images/20100812/bc9be4bc-f041-4d16-8d96-e5c58f777c5d.jpg" />

用兩塊RAM分別存放FIR系數和數據的前N個樣值點,這兩個RAM要求有一個寫數據和一個讀數據的雙端口RAM。數據寫入模塊負責把所要濾波的數據輪換地寫入兩個雙口RAM;FIR的系數也按偶數下標和奇數下標分別寫入兩個系數RAM,實現時是預先配置的。在實現濾波時,如圖1所示對數據移位是不現實的。因此,用交聯網絡結合控制模塊實現第一級流水--取數,完成給下一級流水線正確送數的目的。第二級流水是兩個并行的乘法器,完成乘法運算。第三級流水是一個累加器;在控制邏輯的控制下,對乘法器輸出結果進行正確的累加運算。

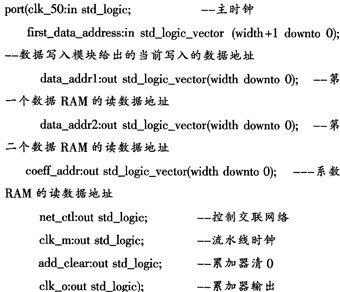

完成結構設計后要進行時序設計。數據寫入模塊的時鐘是根據數據源產生數據的速率而定的。而流水線的工作時鐘頻率要求大于數據產生時鐘頻率的N/2倍,N是濾濾器階數,2是并行度。也就是要求流水線在數據產生的一個周期內能完成一次FIR濾波器輸出的計算。其中的控制邏輯是流水線正常運行的關鍵。數據流水線上的各種時序要求都要由其產生,包括讀數據地址、讀系數的地址、交聯網絡的控制和流水線結構的輸出。其VHDL的端口描述如下:

系數地址由計數器產生,計數器周期是濾波器的階數除以并行度,由first_data_address的第0位的邊沿觸發,以重新從0開始計數。數據RAM的地址加上計數器的值。兩個RAM地址因當前輸入濾波數據的存放位置,可能相同也可能相差1。交聯網絡的控制信號是計數器的最低位。累加器輸出的使能信號是在計數到濾波器的階數時產生的,而后經過延時給到累加器。累加器清零信號在這里產生要比累加器中用其他方法方便得多。

交聯網絡也是設計的重點。對于并行處理結構,各單元之間數據的共享和通信是限制并行度的主要原因。在并行度為2的結構中,只要輪流交換系數就可以了。但是對更高的并行度,這一通信網絡的延時是相當大的,這也是把它單獨列為濾波器的流水線的一級的主要原因。

還要注意的是:有符號數常用補碼表示。在對有符號數進行擴展時,要擴展最高位。對乘法器的輸出一般要進行擴展,以避免累加器溢出。

對于乘加運算,有一種分布式計算方法,也就是把乘法進一步分解為部分和(二進制系數的每一位和輸入數據相與的結果)。當乘加運算的一個乘數是已知常數時,分布式乘加運算會很節省資源。因為系數固定,與運算的結果是在運算前可知的,這樣零位與數據相與的結

果是不參與加運算的,從而實現無乘法器的濾波器。這里不選用這種方法,原因有二:其一,分布式運算將使濾波器難以重配:其二,基于FPGA的硬件乘法器較綜合得來的乘法器性能更佳。

3 仿真及測試

用VHDL語言描述全部電路模塊后,輸入系數1、2、3、4、5和數據-l、-2、3、4等進行測試.用Mod-elsim進行仿真,其結果如圖3所示。

可以看出,模塊能正確進行計算,從數據輸入到數據輸出約延時2個數據時鐘.這主要是前面的數據輸入模塊的延時。乘加部分采用數據時鐘的N/2倍,其延時與濾波器的階數成比例,但不會超過一個數據時鐘周期。

然后,對VHDL描述就Xilinx的Spartan-3進行綜合和測試。可以得出表1所示的測試結果,其中第一行為并行流水結構所設計的濾波器,第二行是采用Xilinx提供的軟核設計的濾波器。

可以看出,除了增加一個乘法器外,邏輯塊和觸發器都增加了一倍多。用這種結構設計的濾波器面積增加了一倍,速度性能也提高了一倍。以上兩種濾波器可以應用在語音信號處理中--讓語音信號通過低通濾波器以獲取語音的低頻分量。相對而言,并行流水結構能實現比Xilinx軟核更高階數的濾波器。在聽覺上,經過兩種濾波器(相同階數)的語音信號沒有太大差別。

4 結束語

本文在運算層次上,依據流水和并行運算結構實現直接型FIR濾波器。如果在設計濾波器時,結合級聯型和直接型兩種濾波器結構,那么也能實現同樣的并行和流水的效果。實際上,還可在更低層次的乘法運算時,對部分和也用并行和流水結構來實現。這些結構的選擇都依據性能要求和實現的復雜性來具體確定。

作為實現現代高性能處理器的方法,并行和流水結構各有特點。并行是以面積換速度。流水是以延時換速度,采用這兩種結構,就能在面積、速度、延時之間靈活互換。