1 引 言

由于雷達所處的環境的復雜性,除了地物、云雨、鳥群等干擾外,還可能來自臨近的雷達異步干擾、電臺干擾等。所有的干擾,經過接收機進入信號處理機,雖然經過了中頻信號的處理,但還可能有殘余。因此,為了得到更好的檢測性能,在檢測前進行一次視頻積累是非常必要的。

雖然視頻積累的效果不如相參積累,但是視頻積累的工程實現比較簡單,對雷達的收發系統沒有嚴格的相參性要求,且對大多數運動目標來講其回波的起伏將明顯破壞相鄰回波信號的相位相參性,因此在許多實際工程應用場合還是采用視頻積累。

在雷達視頻積累算法的工程實現過程中,需要雷達信號處理器具有較快的實時性,并且對信號處理器的穩定性、體積、功耗等也有嚴格的要求。近年來隨著FPGA技術的快速發展,為我們提供了一種更好的解決這一問題的途徑。由于FPGA本身所具備的并行結構的算術結構,使得FPGA特別適合用作高性能的數據通路處理器。利用FPGA實現雷達視頻積累算法具有實時強,硬件系統體積小結構靈活,適于模塊化設計,開發期短,并且支持在線可編程,使系統具有較強的通用性可擴展性等優點。本文以此為出發點,提出并討論一種利用FPGA技術實現雷達視頻積累的方法。

2 系統的硬件結構

在具體實現過程中主要采用一塊基于FPGA的芯達信號處理卡,既可以采集來自雷達接收機的中頻、視頻信號并對其進行數字信號處理,又可以自身模擬產生雷達中頻、視頻信號進行數字信號處理或不處理直接送往雷達信號處理機。雷達信號處理卡的硬件電路結構框圖如圖1所示。

FPGA采用的是Xilinx公司的100萬門FPGA芯片XC3S1000,其配置芯片為Xilinx公司的1 Mb容量PROM芯片XC18V01,以主動串行方式對FPGA進行上電配置。AD,DA分別為ADI公司12位高速模數轉換芯片AD9432與14位高速數模轉換芯片AD9764SRAM采用Cypress公司的256 k×16 b SRAM芯片CYTC1041。

設計中利用FPGA實現32 b/33 MHz的PCI接口邏輯,進行實時信號采集和傳輸控制。由于FPGA具有層次化的存儲器系統,其基本邏輯功能塊可以配置成16×1,16×2或32×1的同步RAM,或16×1的雙端口同步RAM,因此可以在FPGA內部配置高速雙口RAM用來作為信號傳輸的數據緩沖器。同時,為了節省FPGA的內部邏輯資源,在FPGA外圍配置了適當的SRAM用來存儲數據。

3 視頻積累算法在FPGA上的實現

通常視頻積累的工程實現有多種方法。從時域上來說,視頻積累是將連續N個重復周期同一距離單元的視頻回波信號進行疊加,因此實現脈沖串積累離不開延遲線。在使用FPGA實現數字延遲線時,需要將前面N-1個周期的信號量化后存儲起來,這樣做需要較大的存儲量和運算量。所以在實際工程中,常采用滑窗檢測器用于天線波束掃過目標時收到回波脈沖數N較少的場合,但是若N值仍然較大,則滑窗檢測器仍需要有很大的存儲量。因此,在采用FPGA實現視頻積累時,采用小滑窗檢測器更適合于FPGA的特點。

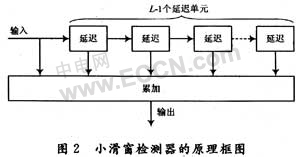

小滑窗檢測器是一種窗孔長度L(累加的脈沖數為L)小于天線波束掃過目標時收到回波脈沖數N的檢測器。L一般比N小很多,例如N在10~20以上,而L取5~7。小滑窗檢測方法進行視頻積累的原理框圖如圖2所示。

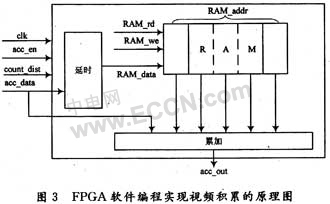

在本設計中,通過FPGA軟件編程采用FPGA+SRAM的方式來實現視頻積累。小滑窗檢測器的延時主要通過將信號量化后存儲在高速SRAM的方式完成。FPGA軟件編程實現視頻積累的原理圖如圖3所示。

圖3中的clk為系統主時鐘;count_dist為距離計數器;acc_en為視頻積累的使能信號,acc_en為高電平時有效;count_dist,clk與acc_en為控制時序關系的主要系統變量;acc_data為求模后輸入的非相參信號,系統的視頻信號實時不斷地輸入到FPGA中。