集成電路的發展經歷了從小規模、中規模、大規模和超大規模集成的過程,但隨著科學技術的發展,許多特定功能的專用集成電路(ASIC)應用日益廣泛,用戶迫切希望根據自身設計要求自行構造邏輯功能的數字電路。復雜可編程邏輯器件CPLD(Complex Programmable Logic Devices)順應了這一新的需要。它能將大量邏輯功能集成于1個芯片中,其規模可達幾十萬或上百門以上。用CPLD開發的數字系統個有容量大、速率快、成本低的特點,且開發靈活、開發周期短。

1 器件結構和開發軟件

1.1FLEX10K簡介

FLEX系列可編程邏輯器件是美國Altera公司主力推出的產品。FLEX10K是該系統器件中的典型代表。與許多PLD器件一樣,它有在線可配置(ISR)功能和高密度、高速度的優點;作為工業界第1個嵌入式PLD,它還采用重復可構造的CMOSSRAM工藝,把連續的快速通道互連與獨特嵌入式陣列結構相結合,來完成普通門陣列的宏功能。每個FLEX10K器件還1包括個嵌入式陣列和1個邏輯陣列,能讓設計人員輕松地開發集成存儲器、數字信號處理器及特殊邏輯功能等強大的功能于一身的芯片。圖1為其結構圖。FLEX10K主要由邏輯陣列(logicarray)、嵌入式陣列(EAB)構成。其中,邏輯陣列是由多個邏輯陣列塊(LAB)組成的,而每個邏輯陣列塊(LAB)又包含8個邏輯單元(logicelement),在每行、列互連通道的兩端都有輸入/輸出單元(IOE)。

1.2 MAX+PLUSII開發軟件特點和設計流

用CPLD實現數字系統設計電路,關鍵技術是必須有一個優秀的開發軟件。Altera公司的開發軟件MAX+PLUS

II界面豐富,使設計靈活、方便、高效。

(1)開放的界面

MAX+PLUS II軟件可與其它工業標準設計輸入、綜合與校驗工具相連接。設計人員可以使用Altera或標準EDA設計輸入工具來建立邏輯設計,對器件設計進行編譯,并能使用Altera或其EDASF校驗工具進行器件仿真。

(2)完全集成化的環境

它是一個完全集成化、易學易用的可編程邏輯設計環境,設計輸入方式有圖形輸入、文本輸入、波形輸入、狀態機設計輸入。其編譯及設計處理寫仿真、定時分析、邏輯綜合與適配均為Windows圖形界面。

(3)支持各種硬件描述語言

支持各種HDL設計輸入選項,包括VHDL、VerilogHDL、ABEL、AHDL等硬件描述語言。

(4)豐富的設計庫

提供豐富的庫單元設計調用,包括74系列的全部器件和多種特殊的邏輯宏功能、新型的參數化兆功能。對于復雜的大系統,設計者需調用宏單元庫,并對其修改某些參數,而無需自己用基本邏輯單元來構成某種功能,以大大減輕設計人員的工作量,縮短設計周期。

電路的設計流程如圖2所示。將所設計的電路用原理圖輸入和硬件描述語言輸入,應用EDA軟件平臺(MAX+PLUS II)編譯通過后,再進行邏輯功能仿零點,生成目標文件,下載到FLEX10K芯片,完成系統設計。

2 交通控制系統設計

2.1 系統介紹

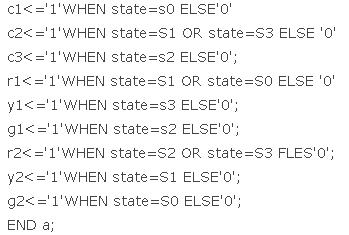

圖3為一十字路口交通管理器,控制甲、乙2道的紅、黃、綠3色燈。計數顯示部分為2個倒計時器,顯示甲、乙車道允許通車時間,指揮車輛和行人安全通行。其R1、Y1、G1為甲道紅、黃、綠燈;R2、Y2、G2為乙道紅、黃、綠燈。

甲道通告時間為t3,乙道通行時間為t2,黃燈亮(停車)時間為t1,C1、C2、C3為定時器工作使能信號,為1時定時器計數;W1、W2、W3為定時器的指示信號,計數時信號為0,計數結束時信號為1。

2.2 FLEX10K內部邏輯功能設計

交通控制系統芯片內部邏輯功能設計采用自頂向下的設計方法,系統頂層電路如圖4所示。它分為5個次級模塊:控制器(traffic_control)、定時器1、定時器2、定時器3、(其定時時間為t3、t2和t1)、計數顯示(含減法計數器和動態掃描電路)。

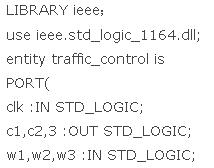

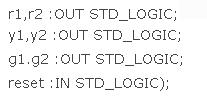

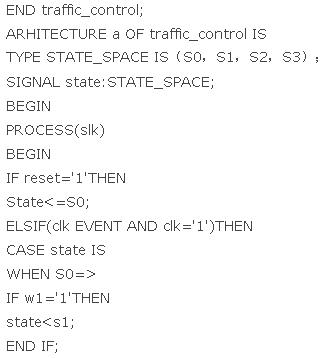

頂層電路圖中減法計數器和動態掃描電路用圖形輸入描述,其它次級模塊控制器、定時器1、定時器2、定時器3用VHDL硬件語言描述。核心模塊控制器的VHDL源文件如下:

3 功能編譯、設計仿真與硬件下載

本系統采用Altera公司生產的FLEX10K系列的CPLD芯片,應用該公司的MAX+PLUS II開發軟件完成設計后,需對各種源文件從低層到頂層逐個編譯,再進行邏輯仿真。選擇器件后,打開檢查項目中所有設計文件,通過檢測發發現在編程器件中可能存在的可靠性不好的邏輯器件引腳分配。

Altera公司推薦的編譯器可自動為項目進行引腳分配,也可人工調整引腳。在編譯器窗口選擇Start按鈕,將對所有設計的項目進行處理,出現錯誤將給出具體錯誤提示。為了保證設計的正確性,在編譯通過后,還需進行邏輯仿真。仿真通過后再應用MAX+PLUS II的編程器對所選可編程邏輯器件下載編程,便完成了交通控制系統的ASIC芯片設計和硬件固化。若在芯片外圍接入必要電源、脈沖信號、顯示器和指示燈,便構成了一個完整交通控制系統。它具有工作穩定、體積小、在線修改方便等特點。