目前國內數控機床中的伺服電機一般都是配套增量式編碼器,而增量式編碼器的精度并不太高且輸出的是并行信號,欲提高其精度就必然要增大編碼器的設計難度和增多并行信號的輸出,這樣就不利于伺服單元與編碼器的長距離通信,而采用絕對式編碼器,除了其精度比增量式編碼器高幾倍以外,其信號的輸入輸出都采用高速串行通信,節省了通信線路便于長距離的通信,在編碼器的另一端,采用CPLD與絕對式編碼器進行高速串行通信,CPLD再把收到的編碼器信息轉變為并行數據傳送給伺服單元中的DSP進行運算控制,本文將給出CPLD與絕對式編碼器高速串行通信的軟硬件設計方案。

硬件設計

硬件主要由電源、CPLD及其外圍電路和絕對式編碼器接口電路三個模塊組成。

電源模塊

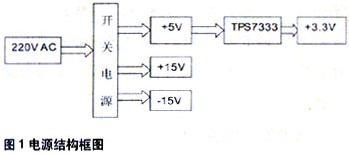

電源模塊由開關電源電路和DC/DC電源芯片組成,如圖1所示。

圖中的開關電源將220V交流電網電壓轉變成+5V,+15V,-15V,開關電源可濾除電網中存在的各種干擾,并且開關電源中的變壓器將220V AC與輸出的+5V,+15V,-15V隔離開,內部電路還采用了TL431調節開關管的導通脈沖寬度,因此開關電源的抗干擾、安全性、穩定性及穩壓程度都比較好,TPS7333是DC/DC芯片,它將+5V的直流電壓轉變成+3.3V的穩定直流電壓供給CPLD使用,TPS7333轉換效率、可靠性和穩壓性都比較好,它在輸入電壓為+3.77V-+10V的電壓范圍內都能轉換出+3.3V,使CPLD不受輸入電壓過高導致其燒壞。

CPLD及其外圍電路模塊

CPLD及其外圍電路模塊主要由CPLD、CPLD編程下載接口電路(JTAG接口),DSP接口電路、有源晶振、電平轉換電路和ADM485及其外圍電路(負責與編碼器通信的接口電路)組成(圖2)。

本設計CPLD采用Altera公司的EPM570T144C5,此芯片屬于Altera公司的MAX II,MAX II相對MAX I成本更加低,功耗更加小,而器件的宏單元數更加多,且器件延時控制在6ns以內,具有很高的性價比,EPM570T144C5有570個宏單元數,芯片的引腳數目為144個,其中可用的I/O口有116個,因此此芯片的資源已經足夠用。CPLD主要負責與絕對式編碼器的高速串行通信,并受控于DSP的命令把接收到編碼器數據和其他信息并行的轉送給DSP。

JTAG接口主要用于下載可執行文件到CPLD,在PC機安裝Altera公司的開發環境-QUARTUS II,并在此開發環境中將編寫好的VHDL程序進行編譯,保證編譯不出錯并且保證功能已實現后,連接好下載電纜到JTAG接口,通過QUARTUS II提供的編程下載工具,對CPLD電路板進行下載。

DSP接口就是由8根數據線,3根地址線和1根控制線組成的,8根數據線負責轉送編碼器數據及其其他信息,3根地址線負責傳送DSP命令,在CPLD終端進行譯碼,CPLD根據譯碼得出的命令將編碼器數據或其他信息通過8根數據線傳送到DSP,控制線主要是完成CPLD與DSP同步控制。

20M有源晶振主要是為CPLD提供基準時鐘,在時鐘信號的驅動下,供CPLD產生2.5Mb/s的波特率與編碼器進行通信,和產生10M赫茲時鐘供一些邏輯控制信號使用,此晶振提供20M赫茲的時鐘頻率,需要電源提供3.3V的直流電壓。

電平轉換電路主要負責將3.3V電壓轉換成5V或將5V電壓轉換成3.3V,因為CPLD的核和I/O口需要的供電電壓都是3.3V,而ADM485和絕對式編碼器所需的供電電壓和I/O口驅動電路都為5V,所以需要用電平轉換芯片LVC4245A將3.3V轉換成5V電壓或將5V轉換成3.3V。

ADM485及其外圍電路是CPLD與絕對式編碼器高速通信的硬件銜接。ADM485工作電壓為5V,其最大通信速率為5Mb/s,采用2個ADM485芯片進行對接通信可提高通信線路上的抗干擾能力,最長的傳輸距離可達1.2km。其外圍電路如圖3所示,虛線的右半部屬于絕對式編碼器的外圍電路,上拉和下拉電阻都是1K歐姆,限流電阻則是220歐姆,ADM485的SDAT是數據輸出引腳,ADM485是SRQ是數據輸入引腳,ADM485的DE是外部控制引腳,該腳受CPLD控制,由于RS-485通信協議屬于半雙工,所以ADM485只能處在發送數據或接收數據的狀態,當ADM485得DE為高電平時,ADM485處于數據輸出狀態(即CPLD接收數據),當ADM485的DE為低電平時,ADM485處于數據輸入狀態(即CPLD發送數據)。

絕對式編碼器接口模塊

絕對式編碼器接口模塊是指絕對式編碼器內部的電源及信號輸入輸出接口電路,其電路與上述的ADM485及其外圍電路是一致的,同樣是采用ADM485芯片及一些上拉、下拉及限流電阻,如圖3所示,虛線的左半部就是絕對式編碼器內部接口電路,它負責與外部ADM485(虛線的右半部)銜接,ADM485受編碼器內部的控制芯片所控制,當編碼器受到CPLD發來的命令之后,控制芯片做出判斷后發送出相應的數據,同時控制ADM485的DE為高電平,即使ADM485處于發送狀態,當發送完數據之后,控制芯片又使ADM485的DE處于低電平狀態,便于隨時接收CPLD發來的命令。

軟件設計

軟件是指CPLD的VHDL程序,其主要由分頻器、接收DSP控制命令、CPLD邏輯控制、波特率發生器、接收及發送數據和串并轉換及發送數據六個軟件子模塊組成(圖4)。

- 分頻器模塊

分頻器模塊主要是把20M赫茲的輸入時鐘頻率分頻為10M赫茲和2.5M赫茲的時鐘頻率,其中10M赫茲時鐘主要是供給CPLD邏輯控制模塊工作,2.5M赫茲時鐘主要是供給波特率發生器模塊工作。

- 接收DSP控制命令模塊

接收DSP控制命令模塊實際上是實時的采集DSP發來的控制信號并及時的將控制信號進行譯碼,譯碼完成后立即轉送給CPLD邏輯控制模塊。

- CPLD邏輯控制模塊

CPLD邏輯控制模塊是整個CPLD軟件的核心,其接收到譯碼數據后,立即作出邏輯控制運算,并快速的控制接收及發送數據模塊和控制串行轉換及發送數據模塊。

- 波特率發生器模塊

波特率發生器模塊主要是為接收及發送數據模塊提供2.5Mb/s波特率。

- 接收及發送數據模塊

接收及發送數據模塊是整個CPLD軟件的重要組成部分,其主要負責與絕對式編碼器高速通信,由于其通信方式是異步串行通信方式,因此其波特率、通信的數據格式及RS-485通信協議都要與絕對式編碼器相同。

- 串并轉換及發送數據模塊

串并轉換及發送數據模塊主要是將接收到的編碼器串行數據轉換成并行數據,并將數據鎖存在CPLD鎖存器內,當CPLD邏輯控制模塊控制其發送數據時,就將鎖存在CPLD鎖存器內的數據以并行的方式放送給DSP,供DSP進行運算控制用。

結語

本設計已經完成了硬件及軟件的全部設計,讀取帶有絕對式編碼器的電動機轉子的任何一個位置數據只需31μs,通信速率可達2.5Mb/s,將本設計集成在伺服驅動單元中,驅動和控制電動機轉數可達6000轉/分,控制電動機轉子的位置精度可達μM級。