引言

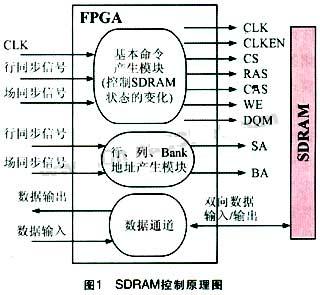

在信息處理中,特別是實時視頻圖像處理中,通常都要對實現視頻圖像進行處理,而這首先必須設計大容量的存儲器,同步動態隨機存儲器SDRAM雖然有價格低廉、容量大等優點,但因SDRAM的控制結構復雜,常用的方法是設計SDRAM通用控制器,這使得很多人不得不放棄使用SDRAM而使用價格昂貴的SRAM。為此,筆者在研究有關文獻的基礎上,根據具體情況提出一種獨特的方法,實現了對SDRAM的控制,并通過利用FPGA控制數據存取的順序來實現對數字視頻圖像的旋轉,截取、平移等實時處理。SDRAM的控制原理,如圖1所示。

SDRAM基本操作原理

本文以三星公司的SDRAM器件K4S561632C[4]為例來是說明SDRAM的工作原理。

SDRAM的結構特點

存儲器的最初結構為線性,它在任何時刻,地址線中都只能有一位有效。設容量為N×M的存儲器有S0-Sn-1條地址線;當容量增大時,地址選擇線的條數也要線性增多,利用地址譯碼雖然可有效地減少地址選擇線的條數,但這種存儲器的長寬比太大,顯然,這在工業上是無法實現的。而且由于連線的延時與連線的長度成正比,這樣的設計會使存儲器的存取速度很慢。為了解決這個問題,現在常用的存儲器都是將存儲單元設計成陣列形狀,使其長寬比接近1:1。這樣,電路就必須增加一個列地址譯碼器,才能選出正確的存儲單元。這樣,整個存儲器的地址線被分為行地址線和列地址線,行地址線要將要選擇執行讀或寫操作的行,而列地址線則可從被選中的一行中再選出一個用于真正執行讀或寫操作的存儲單元。

SDRAM的行地址線和列地址線是分時復用的,即地址線要分兩次送出,先送行地址線,再送列地址線。這樣可進一步減少地址線的數量、提高器件的性能,但尋址過程會由此變得復雜,新型的SDRAM的容量一般比較大,如果還采用簡單的陣列結構,就會使存儲器的字線和位線的長度、內部寄生電容及寄生電阻都變得很大,從而使整個存儲器的存取速度嚴重下降,實際上,現在SDRAM一般都以Bank(存儲體或存儲塊)為組織,來將SDRAM分為很多獨立的小塊,然而由Bank地址線BA控制Bank之間的選擇;SDRAM的行、列地址線貫穿所有的Bank;每個Bank的數據位寬同整個存儲器的相同。這樣,Bank內的字線和位線的長度就可被限制合適的范圍內,從而加快存儲器單元的存取速度,另外,BA也可以使被選中的Bank處于正常工作模式,而使沒有被選中的Bank工作在低功耗模式下,這樣還可以降低SDRAM的功耗。

為了減少MOS管的數量、降低功耗、提高集成度和存儲容量,SDRAM都是利用其內部電容存儲信息,由于電容的放電作用,必須每隔一段時間給電容充電才能使存儲在電容里的數據信息不丟失,這就是刷新過程,這種機制使SDRAM的控制過程變的更加復雜,從而給應用帶來難度。

三星公司的SDRAM(K4S561632C)的外部同步時鐘速率可在一定的頻率范圍內連續變化,最高頻率可達到133MHz,每塊SDRAM內含四個獨立的Bank;它的基本存儲單元都是按照陣列排列的,它的數據位寬和整個存儲器的位寬相同,同時支持多種讀寫模式;所有的輸入信號均以時鐘的上升沿為基準,這使得地址、控制和數據輸入到緩沖器的時間可保持一致且建立和保持的時間很小;該器件使用完全流水線型內部結構;另外,它還具有突發長度可編程、延遲可編程等優點。這些優點使得K4S561632C能廣泛的應用于寬頻帶、高性能存儲器應用系統。

SDRAM的基本信號

SDRAM的基本信號可以分成以下幾類:

(1)控制信號:包括片選(CS)、同步時鐘(CLK)、時鐘有效(CLKEN)、讀寫選擇(WE)、數據有效(DQM)等;

(2)地址選擇信號:包括行地址選擇(RAS)、列地址選擇(CAS)、行/列地址線(SA0-SA12)分時復用、Bank塊地址線(BA0-BA1);

(3)數據信號:包括雙向數據端口(DQ0-DQ15)、接收數據有效信號(DQM)控制等。DQM為低時,寫入/讀出有效。

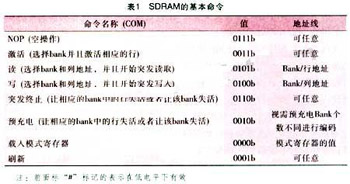

對SDRAM的基本命令

要正確的對SDRAM進行操作,就需要輸入多種命令:包括模式寄存器設置、預充電、突發停止、空操作等命令。SDRAM內部的狀態會根據表1的命令進行轉移,其中,命令COM={CS#;RAS#;CAS#;WE#}。

模式寄存器的規定

利用模式寄存器(Mode Register)[5]可通過裝載模式寄存器命令(LOADMODE REGISTER)進行

編程,這組信息將會一直保存在模式寄存器中,直到它再次被編程或器件掉電為止;它規定了SDRAM的操作模式,包括突發長度、突發類型、CAS延遲時間、運行模式及寫突發模式、具體格式如圖2所示,模式寄存器M0-M2用于規定突發長度(Burst length)。M3用于規定突發類型BT(Burst Type),M3=0時,突發類型是連續的;M3=1時,突發類型是交錯的,M4-M6用于規定CAS延遲的時鐘周期數,M7-M8規定運行模式,M9規定寫突發模式WB(Write Burst Mode),當M9=0時,按實際編程的突發長度存取,當M9=1時,則按單個存取單元寫入,但可按實際編程的突發長度讀出,M10和M11為保留位,可供未來使用。在模式寄存器裝載期間,地址A12(M12)必須被驅動至低電平,本方案中,模式寄存器的值為ox220h。

初始化操作

SDRAM在上電以后必須先對其進行初始化操作,而后才能對其進行其他操作。出初始化操作具體步驟如下:

(1)SDRAM在上電以后需要等待100-200μs,在等待時間結束后還至少要執行一條空操作命令;

(2)SDRAM執行一條預充電命令后,要執行一條空操作命令,這兩個操作會使所有的存儲單元進行一次預充電,從而使所有陣列中的器件處于待機狀態;

(3)SDRAM要執行兩條自刷新命令,每一條刷新命令之后,都要執行一條空操作命令,這些操作可使SDRAM芯片內部的刷新及計數器進入正常運行狀態,以便SDRAM為模式寄存器編程做好準備;

(4)執行加載模式寄存器(LOAD MODE REGISTER)命令,完成對SDRAM工作模式的設定。完成以上步驟后,SDRAM即可進入正常工作狀態,以等待外部命令對其進行讀、寫、預充電和刷新等操作。

SDRAM的基本讀寫操作

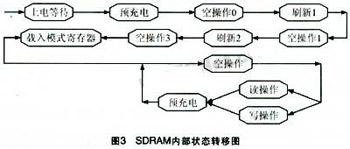

SDRAM的基本讀操作[3]需要控制線和地址線相配合并發出一系列命令來完成。SDRAM的讀操作只有突發模式(Burst Mode);而寫操作則可以有突發寫和非突發寫兩種模式,具體如下:

(1)帶有預充電的突發讀寫模式,該模式一次能夠訪問的列地址的最大數為1、2、4、8;

(2)不帶有機充電的全頁讀寫、此模式可任意控制一次能夠訪問的列地址的最大數。 根據實際情況,本設計只選取了與本方法相關的基本操作命令,并沒有設計通用的控制器,圖3是本方案的SDRAM內部狀態轉移圖。

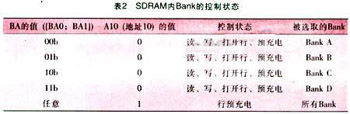

Bank乒乓操作

由于Bank內的行與行之間具有關聯性,因此,當其中一個Bank的讀或寫操作結束后,必須執行一次預充電命令以關閉正在操作的行、預充電命令執行后,會有一個tRP的延時,延時完成后才能向同一Bank行(或其他行)發出新的激活命令。由于Bank之間是相互獨立的,因此,在一個Bank進行正常的讀或寫操作時,可以對另外幾個Bank進行預充電或空操作;當一個Bank的進行預充電期間也可以直接調用另一個已經進行預充電的Bank,而并不需要等待,具體的Bank控制過程要參考特定的器件數據手冊。三星公司的K4S561632內的Bank控制狀態如圖2所列。

常用的三種尋址方式

K4S561632C器件的常用尋址方法有以下三種:

(1)頁命令中PH(Page Hit):若尋址的行與所在的Bank的空閑的,即該Bank內所有的行是關閉的,那么此時便可直接發送行有效命令,這種情況下,數據讀取前的總耗時為tRCD+CL;(tRCD為RAS到CAS的延時;CL為CAS latency)。

; (2)頁快速命中PFH(Page Fast Hit)或頁直接命中PDH(Page Direct Hit):如果要尋址的行正好是在正常讀或寫,即要尋址的行正處于被選通的有效狀態,那么此時可直接發送列尋址命令,這種情況下,數據讀取前的總耗時僅為CL,這就是所謂的背靠背(Back to Back)尋址;

(3)頁錯失PM(Bage Miss):若要尋址的行所在的Bank中已經有一個行處于激活狀態(未關閉),這種現象而稱為尋址沖突,這樣,就必須要進行預充電來關閉正在工作的行、然后再對其他的行發送行有效命令,其總耗時為:tRP+tRCD+CL。(tRP為Row precharge time)。

在以上三種尋址方式中,PFH是最理想的尋址方式,PM則是最糟糕的尋址方式,實際應用中要盡量采用PFH尋址方式而應避免采用PM尋址方式。

減少延遲的方法

自動預充電技術是一種有效的減少延遲的方法,它通過自動在每次行操作之后進行預充電操作來減少對同一Bank內的不同行尋址時發生沖突的可能性,但是,如果要在正在讀或寫的行完成操作后馬上打開同一Bank的另一行時,仍然存在tRP的延遲。 交錯式控制是另一種更有效的減少延遲的方法,即在一個Bank工作時,對另一個Bank進行預充電或者尋址(此時要尋址的Bank是關閉的),預充電與數據的傳輸交錯執行,當訪問下一個Bank時,tRP已過,這樣就可以直接進入行有效狀態,如果配合得比較理想,那么就可以實現無間隔的Bank交錯讀或寫,因此,Bank之間的切換可使存儲效率成倍提高,并能夠大大地提高多組SDRAM協同工作時的性能。

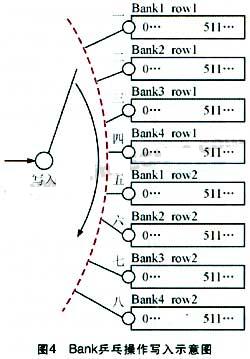

Bank乒乓操作寫入

一個由行、場同步信號控制的計數器在預定的時刻會產生一個控制信號,先發出激活相應Bank的激活命令(ACTIVE),并鎖存相應的Bank地址(由BA0、BA1給出)和行地址(由A0-A12給出)。一個周期后再給出列地址和寫入命令;在CL個周期后,便可將所需寫入的數據依次送到數據總線上,當計數器的計數周期到達時,系統會產生一個控制信號,并向SDRAM發送預充電(PRECHARGE)命令(如果使用了可編程長度,則在這前要使用突發終止命令),以關閉已經激活的頁。在下一個視頻行同步信號來臨時,系統將重復以上操作,并如此循環下去,具體操作如圖4所示,圖中左邊的一、二、三……為所對應的視頻行同步信號,右邊1至511……則代表對應的存儲器中的列地址(即是屏幕上對應的像素的位置)。

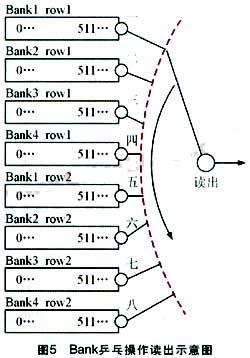

Bank乒乓操作讀出

由行、場同步信號控制的一個計數器可在預定的時刻產生一個控制信號,它首先發出相應的Bank激活命令(ACTIVE),并鎖存相應的Bank地址(由BA0、BA1給出)和行地址(由A0-A12)給出,然后在一個周期后給出列地址和讀命令,當計數器的計數周期到達時,系統會產生一個控制信號,并向SDRAM發出預充電(PRECHARGE)命令,以關閉已經激活的頁(如果使用了可編程長度,則在這之前要使用突發終止命令)。之后,再在下一個視頻行同步信號來臨時重復以上操作,如此循環(具體操作如圖5),圖中左邊的一、二、三……為所對應的視頻行同步信號,右邊1至511……代表對應的存儲器中的列地址(即是屏幕上對應的像素的位置。

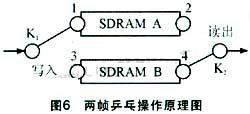

場乒乓操作

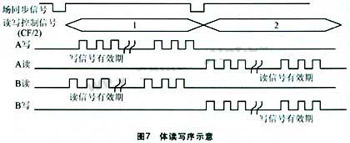

為了SDRAM能正確進行讀和寫兩個操作,本方案選用兩場乒乓操作[6]來實現數據存取,實際上,就是在不同的時間對兩場輪換進行讀或寫,一場讀而另一場寫,其原理如圖6所示。當開關K1在1位置,K2在4位置是時,A寫B讀;反之,當開關K1在3位置,K2在2位位置時,A讀B寫。如此循環往復。

若以場同步信號的二分頻計數器F/2為讀寫控制信號,假設SDRAM A在F/2時為1寫、2讀,則SDRAM B在F/2時為2寫、1讀,兩場即為一個場乒乓操作周期,讀寫信號均在場同步信號為高電平時有效,由于存在消隱期,消音所以,將會有一段時間讀寫都無效(讀寫信號都是低電平,此時SDRAM進入預充電狀態),其總體時序如圖7所示。

結束語

SDRAM的控制過程雖然很復雜,但如果根據實際情況進行取舍以滿足實際系統要求,那么,SDRAM的控制過程還是比較簡單的,在實驗中,使用ALTERA公司的Cyclone FPGA器件進行設計時,程序設計可采用Verilog語句來實現對實時視頻信號的采集,并通過改變計數器的周期及SDRAM的行、列地址線和時序就可以對任意位置的視頻圖像進行平移、旋轉、截取等處理,此外,由于程序設計采用了化整為零和參數化設計思想,因而結構透明、簡單;對于特定容量的SDRAM的特定工作模式而言,該方法只需根據器件重新設定參數而不要重新編寫程序,因而具有較強的通用性。