摘? 要: 針對ADSP-21535 Blackfin 的Mem DMA 高速通信" title="高速通信">高速通信中的關鍵技術進行了討論,分析了系統的內存管理" title="內存管理">內存管理,對DMA的相關寄存器的配置進行了詳細講解,并給出了具體實例。對多種內存之間的DMA列出了實際的指標評測,為該系列DSP工程應用的高速通信設計提供了重要參考。

關鍵詞: ADSP-21535 Blackfin? Mem DMA

?

ADSP-21535 Blackfin 是美國AD公司和Intel 公司于2001年底聯合推出的一款定點DSP, RISC指令結構,運作高效,具有十分優異的性能。該DSP具有300MHz的主頻,2個40bit的MAC(乘加器)和2個32bit的ALU(算術邏輯單元),4個8bit的視頻處理單元,16個地址尋址單元。該DSP內部集成了308KB的RAM,并具有豐富的外部接口,如PCI、USB、SPI、同步和異步串口等。同時,芯片內部設計了看門狗和多種定時器,充分滿足軟件工程穩定性的設計要求。值得一提的是,21535可以動態地控制電壓輸入,調整運行頻率,減少芯片功耗,十分適用于移動產品的設計。

2002年底,AD公司在中國開始大規模推廣Blackfin系列的DSP,21535成為該系列的旗艦產品。由于該DSP推出時間不長,相關文獻幾乎沒有報道;而且,在許多接口性能方面,AD公司也沒有對其給出準確的指標。根據通常的設計經驗可知,新產品通常在某些方面沒有達到設計要求。筆者所設計的高速通信板數據交換速度必須達20M Word/s以上,因此對該DSP的高速通信必須進行準確仔細的評估和設計。

ADSP-21535的內存訪問支持I/O方式、內存映射和多種DMA方式,其中Mem DMA(Memory to memory DMA)方式是最快的一種并行通信方式。因此,筆者在設計時選擇了Mem DMA作為高速通信方式。由于21535支持多種內存,因此在設計Mem DMA時,必須對21535的內存管理有一個詳細的了解。

1 ADSP-21535的內存管理

21535的內存管理十分強大。它把存儲器視為一個統一的4GB的地址空間,使用32位地址。所有的資源,包括內部存儲器、外部存儲器、PCI地址空間和I/O控制寄存器,都具有獨立的地址空間。此地址空間的各部分存儲器按照分級結構排列,以提供較高的性能價格比。一些快速、低延遲的存儲器(如L1)的位置接近處理器核心,而低成本低性能的存儲器遠離核心。 芯片內部的308KB RAM中,其中L1(一級緩存)52KB,L2(二級緩存)256KB;外部地址訪問空間可以高達768MB,通過EBIU(External Bus Interface Unit,外部總線接口單元)進行管理。EBIU支持多種內存,如SDRAM、SRAM、ROM、EPROM、FLASH、FIFO等。內存地址的具體配置空間如圖1所示。

?

L1作為DSP的一級緩存,可以與DSP的內核一樣,運行在300Mbps的高速上。它分為三部分:16KB的Instruction Ram(指令存儲器)、,兩塊16KB的Data Ram(數據存儲器)、4KB的Scratchpad Ram(中間結果緩存)。指令存儲器既可以作為SRAM,也可以配置為4路聯合設置的Cache。數據存儲器能夠配置成雙路聯合設置的Cache或者SRAM;中間結果緩存只能作為SRAM使用。指令緩存和數據緩存都可以通過DMA方式灌入數據,但是對于中間結果緩存這種方式不能使用。

L2作為DSP的二級緩存,是一個統一的指令和數據存儲器,能夠根據系統設計要求同時存放代碼和數據。L2具有DSP核心同樣的帶寬,但是延遲時間較長,訪問L2單個獨立的地址時系統需要經過7個周期的延時,這時它的訪問速度在42.8Mbps左右。所以如果程序比較大,必須在L2中編寫程序時,通常將L1配置為L2的Cache,這樣,速度可以大大加快。

21535支持的片外存儲器種類很多,值得一提的是它的SDRAM控制器。21535集成的SDRAM控制器能夠以fSCLK(系統時鐘,為核心時鐘的若干分頻)的速度,與多達4個Bank的工業標準SDRAM或者DIMM接口。每個Bank可以配置為16MB~128MB的存儲器,符合PC133 SDRAM的標準。

存儲器的DMA控制器提供高帶寬的數據傳輸能力,它能夠在內部L1/L2存儲器和外部存儲器(包括PCI存儲空間)之間執行代碼或者數據的塊傳輸。

2 DMA寄存器的配置

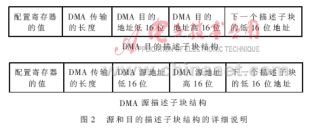

為了描述Mem DMA序列,DMA控制器使用一套名為描述子塊" title="子塊">子塊(Descriptor)的參數。當需要后繼的DMA序列時,這些描述子塊被鏈接起來。這樣,一個DMA序列完成時能夠自動初始化下一個序列,并將其啟動。如果不需啟動下一個序列,只要將其指向一個內容為0的地址空間即可。如果下一次鏈接指向原描述子塊,則DMA完成后暫停。為訪問整個ADSP-21535的地址空間,源地址和目的地址描述子塊采用了全32位地址的基指針。兩個描述子塊均為5個字的連續空間,需要注意的是該連續空間必須定義在L2范圍內。描述子塊內包含的內容如圖2所示。

?

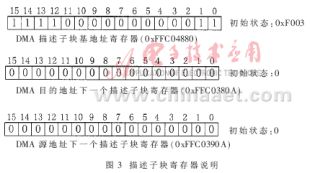

Mem DMA規定,描述子塊所在的首地址必須傳入相關的寄存器。描述子塊首地址的高16位裝入DMA_DBP寄存器(DMA Descriptor Base Pointer Register,DMA描述子塊基地址寄存器)內。由于該寄存器嚴格限定必須在0xF000~0xF003,這就限定了源和目的地址描述子塊只能定義在L2存儲器內,并且高16位地址相同。

描述子塊首地址的低16位放在兩個寄存器中,源地址描述子塊低16位裝入MDS_DND寄存器(Source Memory DMA Next Descriptor Pointer Register,DMA源地址下一個描述子塊寄存器),而目的地址描述子塊低16位裝入MDD_DND寄存器(Destination Memory DMA Next Descriptor Pointer Register,DMA目的地址下一個描述子塊寄存器)。其說明如圖3所示。

在描述子塊的地址傳入相應寄存器后,后面的四項先配置,然后設置第一項。也就是對管理DMA啟動參數的寄存器進行參數配置。兩個配置寄存器" title="配置寄存器">配置寄存器的詳細內容如圖4所示。例如當目的地址寄存器為0x8003,源地址寄存器為0x8001時,傳輸的數據總長=DMA傳輸的長度×字。需要注意的是,雖然此時傳輸以16位(字長)傳輸,但DMA的帶寬是32位,剩下的帶寬資源將被浪費。8位傳輸時,帶寬資源利用率更低。

?

?

下面,以一個具體的32位DMA例子說明上面的描述子塊和多個寄存器的使用方法。

3 32位DMA的例程

R0.H = 0x8009;?? //DMA源配置字,設置為32位傳輸

R0.L = 0x800;???? //DMA長度

R1.L = 0x2000; ? //DMA源地址低16位

R1.H = 0xf000; ? //DMA源地址高16位,這里指向L2

R2.L = RAM_READ;?? //DMA源描述子塊首地址低十六位,DMA讀

R2.H = 0x800b;?? //DMA目的配置字,設置為32位傳輸

R3.L =0x0000;??? //DMA目的地址低16位

R3.H =0xff90; ?? //DMA目的地址高16位,這里指向L1數據存儲器-Bank B

R4.L = RAM_WRITE; //DMA目的描述子塊首地址低十六位,DMA寫

P0.L = RAM_READ;?? //將32位的源描述子塊的地址載入P0

????P0.H = RAM_READ;

P1.L = RAM_WRITE;?????? //將32位的目的描述子塊的地址載入P1

??? P1.H = RAM_WRITE;

W[P0+0x2] = R0;???????? //將DMA長度寫入源描述塊第二個字中

[P0+0x4] = R1; ???????? //將DMA的32位源起始地址寫入源描述塊第三第四個字中

W[P0+0x8] = R2.L;?????? //將下一個源描述子塊的地址寫入源描述塊第五個字中

W[P1+0x2] = R0;???????? //將DMA長度寫入目的描述塊第二個字中

[P1+0x4] = R3; ???????? //將DMA的32位目的起始地址寫入目的描述塊第三第四個字中

W[P1+0x8] = R4;???????? //將下一個目的描述子塊的地址寫入目的描述塊第五個字中

W[P0] = R0.H; ????????? //將DMA源配置字寫入源描述塊第一個" title="第一個">第一個字中

W[P1] = R2.H; ????????? //將DMA目的配置字寫入目的描述塊第一個字中

R6 = P0;????????????????//將P0的值同時存在R6內

P2.L = 0x390A; ???????? //將DMA源描述子塊配置寄存器的地址傳給P2

P2.H = 0xFFC0;

W[P2] = R6.L; ???????? //將DMA源描述子塊所在地址的低16位傳給P2指向的地方

P3.L = 0x4880;?????????//將描述子塊基地址寄存器的地址傳給P3

P3.H = 0xFFC0;????????????????????????????????????

W[P3] = R6.H;?????????? //將DMA源描述子塊所在地址的高16位傳給基地址寄存器

P4.L = 0x380A;????????????????

P4.H = 0xFFC0;? ??????? //將DMA目的描述子塊配置寄存器的地址傳給P4

R6 = P1;????????????????//將P1的值轉存到R6

W[P4] = R6.L; ????????? //將目的描述子塊所在地址的低16位傳給配置目的地址寄存器

P5.L = 0x3902

P5.H = 0xFFC0;? ?????? //將DMA源地址配置寄存器所在地址傳給P5

R6 = W[P5];

BITSET(R6,0);??????? ?//設置R6的最低位為1,表示準備啟動讀DMA

I0.L = 0x3802;

I0.H = 0xFFC0;?? ???? ?//將DMA目的地址配置寄存器的地址傳給I0

R7.L = W[I0];

BITSET(R7,0);??????? ?//設置R7的最低位為1,表示準備啟動寫DMA

????W[P5] = R6;??????????? //將R6和R7的低16位寫入兩個配置寄存器中,真正啟動DMA

????W[I0] = R7.L;???????????????????????????????????????

DMA_WAIT:????????????? //等待DMA結束

R6 = W[P1];??????????? //根據寫描述子塊第一個字的最高位判斷描述子塊的所有權

????cc = bittst(R6,15);???

IF cc JUMP DMA_WAIT;?? //如果為1,表示還在DMA狀態,繼續判斷,等待

????????????????????????????????????????????????

RTS;

.align 4;?????????????? //在L2空間范圍內定義兩個描述子塊,要求4個字節對齊

????.BYTE2 RAM_READ[5];????????????????????????

.align 4;

.BYTE2 RAM_WRITE[5];

????值得注意的是,在上述DMA例程中,筆者使用了查詢等待方式,但中間完全可以插入其他指令,例如DSP還可以同時作雙乘加和兩次32位取數。只要不訪問正在DMA讀寫的地址區域,沒有任何影響。這意味著,在系統DMA的同時,DSP可以同時進行其他操作,這一點對于提高DSP的效率至關重要。

4 各種內存空間的DMA訪問指標測試及分析

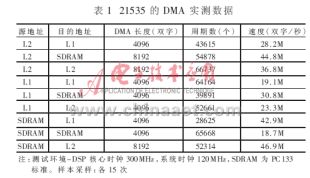

? 根據以上配置,筆者對ADSP-21535的DMA性能進行了比較詳盡的測試。測試數據如表1所示。

?

?

? 從表1中的實測數據可以看出,DMA的速度均在18.7M雙字/秒以上,最高速度達46.9M雙字/秒,可以滿足工程中高速采集的需要。從表中數據可以得出以下結論:

(1)DMA雙向速度不對稱,將源地址和目的地址交換后,速度會發生變化;

(2)低速向高速區域傳輸時,要比反向傳輸快;

(3)同類區域DMA一般比區域之間DMA要慢。如L1 DMA到L1,比L1 DMA到L2和SDRAM都要慢一些。其它區域也有類似現象。

(4)高速區域DMA速度并不一定快,如L1區域DMA速度總體表現反而最低。

?

參考文獻

1 AD公司. ADSP-21535 Blackfin DSP Hardware Reference. 2002

2 AD公司. Blackfin DSP Instruction Set Reference.? 2002