I2C總線(inter integrated circuit bus)由飛利浦公司于20世紀80年代研究開發。I2C總線接口電路其簡單性和有效性而被廣泛用于連接微處理器及外圍設備。在電視中頻解調電路中,二線制的I2C總線接口電路使得主控制器只需要2個引腳便可實現對解調電路所有功能的控制,且總線接口集成在器件中,各電路單元之間只需要最簡單的連接,大大簡化了電路板上的走線,減少了電路板面積,提高了其可靠性,降低了成本。

在該中頻解調的接口電路中,基于I2C總線傳輸協議,通過對狀態機與控制邏輯的優化設置,只需要1個3位的狀態機便可實現電路的使能、啟動、終止、應答、復位、選址等功能,電路得到了最優化,且通過地址選擇位的增加,防止了芯片地址沖突,極大地改善了電路的可靠性及穩定性。

1 I2C總線的特點及數據傳輸

1.1 總線特點

I2C總線是由數據線SDA和時鐘線SCL構成的雙向串行總線,I2C總線上的所有節點,如主控器、外圍器件、接口模塊都連接到SDA,SCL上,在總線備用時,SDA和SCL都保持高電平,I2C不工作時SCL嵌位在低電平。為了使總線上所有電路的輸出都能實現“線與”功能,I2C總線接口電路的輸出端必須是漏極開路結構,輸出端要接上拉電阻。

1.2 總線的數據傳輸格式

I2C總線數據傳送格式按圖1進行。首先由主控設備發出起始信號(S),即SDA在SCL高電平期間由高電平跳變為低電平,然后主控器發送1個字節的數據。首先傳送的是最高位(MSB)。在傳輸了每個字節之后,必須要有接收設備發出1位應答信號。

起始信號后的第1個字節是尋址字節,尋址字節的高7位是接收設備的地址,第8位是方向位,“O”發送數據(寫狀態),“1”接收數據(讀狀態)。尋址字節后面可以有很多數據字節,每個字節后都要有一位發自接收設備的應答信號。在結束與該接收設備通信時,主控設備

必須發出終止信號(P),即在時鐘線SCL為高電平期間,SDA由低電平跳變為高電平。

2 中頻解調電路I2C總線接口的實現

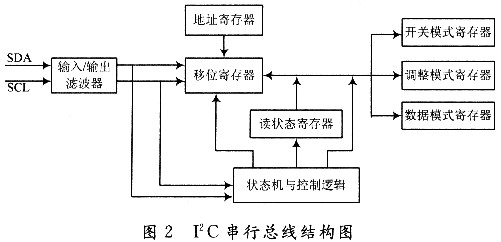

電視中頻解調電路中的I2C總線接口主要由輸入濾波器、地址寄存器、移位寄存器、控制寄存器、狀態機與控制邏輯、讀狀態寄存器、輸出模式寄存器等構成,如圖2所示。其中,輸入濾波器具有I2C總線邏輯兼容電平,輸入時鐘與內部時鐘同步,可濾除部分干擾信號。控制邏輯作為控制核心控制著每一部分的狀態。地址寄存器存放著自己的7位地址,用來與接收到的地址比較。移位寄存器、輸出模式寄存器與讀狀態寄存器端口并行相接,各存儲著8位數據字節。

(1)起始信號與結束信號檢測。起始信號與結束信號的檢測由2個下降沿D觸發器和1個反相器構成,如圖3所示。D1在SDA從高電平跳變到低電平時觸發,此時只有當SCL保持高電平時,Start才為1,即檢測到起始信號。同理,D2在SDA從低電平跳變到高電平時觸發,此時只有當SCL保持高電平時,Stop才為1,即檢測到結束信號。

(2)地址檢測。根據設計要求,I2C總線每次通信輸入8位地址數據和控制數據,電路進行地址比較以后,如果地址正確,則接收控制數據。為了防止地址沖突,增加了地址選擇位,具體實現如圖4所示。D7~D1為發送的數據地址,由于S1,S2是可設置端口,有4種組合,即總線接口有4個地址,分別為 1000010,100001l,1001010,100101l,只有當D7~D1為100S101S2時,選址成功,即可以有效解決地址沖突。

(3)數據串并與并串的轉換。電路中,串行數據轉換為并行數據、并行數據轉換為串行數據主要由移位寄存器完成。它以并行方式與輸出模式寄存器和讀狀態寄存器相連;以串行方式與數據線SDA相連。發送的數據由讀狀態寄存器裝載到數據寄存器中。發送后數據又從串行通道返回數據寄存器中,接收數據時,數據寄存器裝入SDA線上的數據。

(4)內部總線狀態的檢測。讀狀態寄存器連接著內部總線的8位狀態位S0~S7,在讀狀態時,該寄存器將內部總線的狀態讀進去,再以并行方式傳給移位寄存器,移位寄存器以串行的方式傳給數據線,即內部總線狀態被主控器讀取,如圖5所示。

(5)并行端口的擴展。根據芯片功能的需要,設置了4組輸出模式寄存器,分別為調整模式寄存器、備用寄存器、開關模式寄存器、數據模式寄存器。寄存器個數可根據芯片功能的需要進行并行擴展,由于每一組寄存器都對應著相應的子地址,所以每一組寄存器對應相應的時鐘CPl,CP2,CP3,CP4和控制端 C1,C2,C3,C4。這些時鐘和控制端由1個帶控制端的2/4譯碼器輸出,所以每次只有1組寄存器工作,如圖5所示。

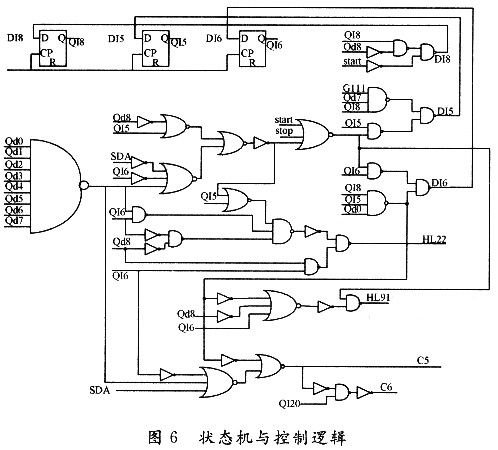

(6)狀態機與控制邏輯的設置與優化。狀態機與控制邏輯作為I2C接口的控制中心,主要用于控制I2C接口電路的使能、啟動、終止。圖5給出寄存器組圖的應答、復位、選址及中斷請求等。通過對狀態機與控制邏輯的優化設置,僅使用3位狀態作為狀態機的狀態端,在滿足更多功能的基礎上,電路更易于實現。如圖6 所示,3個觸發器的輸出Q18,Q15,Q16為狀態機的狀態,Qd0~Qd8為移位寄存器的輸出,HL91為移位寄存器的可控復位端,G111為地址檢測位,HL22為應答位,C5,C6為移位寄存器與讀狀態寄存器的控制端。

上電后,狀態機的初始值被置位為全0。HL91作為移位寄存器輸入端的置位端將移位寄存器的輸入端置0。當初始信號到來時,start信號變為1,此時狀態機的狀態變為100,開始傳送尋址字節;當8位地址傳送完畢后,假設為寫狀態,此時Qd8變為高電平,應答位HL22由高電平變為低點平,狀態機的狀態變為110。HL91變高將移位寄存器的輸入置0,響應結束后,應答位由低電平變為高電平,狀態機的狀態變為010,此時開始傳輸數據。

I2C總線開始工作后,主控器便發送尋址字節給移位寄存器,在移位寄存器將7位串行地址并行移出,且與地址寄存器的從地址進行比較,當地址相同時,Glll變為1,尋址成功,此時應答信號HL22變為0,并告知主控制器。在尋址成功后,如果為讀狀態,則在傳完該字節之后,產生應答信號,狀態機變為100,移位寄存器控制端C5變為低電平,讀狀態寄存器的控制端C6變為高電平,讀狀態寄存器讀入內部總線狀態。其中,QI20是與讀/寫有關的控制端,響應結束后,狀態機狀態變為110,此時,C5變為高電平,C6變為低電平,讀狀態寄存器將存儲的8位狀態位并行傳給移位寄存器;移位寄存器將狀態串行移出,發送給主控制器;主控制器接收到8位狀態位后,發送非應答信號給接收器,使它釋放數據線;響應結束后,主控制器產生結束信號,結束數據傳送。 如果為寫狀態,在接收器產生應答信號后,主控器將發送子地址給移位寄存器。根據輸出模式寄存器功能的不同,分別對應3組不同的子地址。在狀態機與控制邏輯的作用下,子地址具有自動加1功能,所以在讀寫多字節時,可以實現自動操作,加上后面的2/4譯碼器,每次只選通1路輸出模式寄存器,如圖7所示。

在所有數據發送完畢后,接收器發送應答信號給主控制器,響應結束后,主控制器發送停止信號(P),結束數據傳送。

3 仿真結果

通過VHDL的程序編寫,對I2C模塊進行了分析綜合,得到如圖8、圖9的仿真結果。

在寫狀態時,尋址位后的讀/寫位為0,C6一直為低電平,即讀狀態寄存器不工作,在開始后的第8個時鐘,移位寄存器將SDA的數據并行移出,第9個時鐘時,應答位HL22變為低電平。在讀狀態時,當傳完7位尋址位和“1”方向位時,C5變為低電平,C6變為高電平,讀狀態寄存器工作,可將內部總線狀態讀進來。

在讀/寫2種狀態下,I2C控制模塊都能很好地實現I2C總線的開始、停止、讀、寫、響應等功能,仿真結果正確,完全符合I2C總線標準和電路預期的要求。

4 結 語

目前,I2C總線已作為一種標準廣為人們接受,除了帶有I2C總線的單片機和一些常用的外圍設備器件,在電信、電視、音像等產品中都有成套的I2C總線器件。

隨著大量串行數據的傳輸,I2C總線的傳輸速率已提升為高速模式,可達到3.4 Mb/s,尋址范圍也由原來的7位擴展為10位,這樣被控器的地址數量約增加了10倍。