1 引言

隨著IC工藝的提高,從幾百兆赫到幾千兆赫的處理器已經非常普及,以往的低速PCB" title="PCB">PCB設計方法已完全不能滿足日益增長信息化發展的需要.利用EDA工具分析解決高速設計所而臨的問題是一種有效辦法。在設計的過程中,由EDA工具對輸入器件模型數據進行分析,將結果直接反給設計者,設計者根據反饋信息對設計進行修改完善.從而縮短了開發周期,避免了人力、財力的浪費。

2 系統組成

本試驗平臺采用Motorola 公司的Dragonball系列芯片中的MC9328MX1,其CPU時鐘速度200MHz;SDRAM采用了SUMSUNG公司的同步 K4S281632E,時鐘速度100MHz以上。由于地址總線和數據總線的布線密度比較大,速度較高,系統對信號完整性要求較高,因此采用MENTOR 公司的PADS2004" title="PADS2004">PADS2004設計軟件,它將原理圖設計、PCB Layout和高速仿真分析集成于一體,可以解決在PCB設計中存在的信號完整性、串擾等問題,大大提高了設計成功率。

系統沒計中最關鍵走線的是SDRAM與MC9328MX1之間的連接走線,它們的信號完整性直接影響著系統能否正常工作。PCB設計中,采用 PADS2004軟件的高速仿真工具HyperLynx進行仿真,HyperLynx包括LineSim和BoardSim 兩部分,其中LineSim是布線前仿真工具,而BoardSim是布線后仿真工具。仿真模型采用IBIS模型,IBIS模型采用I/V和V/T表的形式來描述數字集成電路I/O單元和引腳的特性。由于IBIS模型無需描述I/O單元的內部設計和晶體管制造參數,因而受到半導體廠商的歡迎和支持,現在各主要數字集成電路制造商都能在提供芯片的同時提供相應的IBIS模型。

3 系統設計

3.1 電源分配

高速系統板設計中電源層的網絡分配很重要。在PCB布線方面,PCB板首先要考慮電源的完整性,它直接影響最終PCB板的信號完整性。很多情況下,影響信號畸變的主要原因是電源系統,例如去耦電容設計不好,地層設計不合理,電流分配不均勻,地彈噪聲太大,回路影響很嚴重等。

由于電源層是通過整個金屬層來分配電源,其電源阻抗很小,所以電源噪聲也比總線式小得多,因此設計時將電源單獨作為一層。

為了消除電源噪聲,在電路板的電源輸入上放置一個47uF電容,用來消除低頻噪聲。在板子上的每個有源器件的電源引腳和接地引腳上放置一個0.1uF高頻濾波電容來濾除線路高頻噪聲。濾波電容應盡量接近電源引腳,使電源引腳到濾波電容的走線最短來取得最好的濾波效果。

3.2 時鐘設計

時鐘設計在PCB設計中是很重要的一部分,通過規劃時鐘線,使得時鐘線的連線遠離其它的信號線,時鐘在跟地層相鄰的信號層上走,走線盡量在一層走,不要穿越多層。時鐘線和其它數據、地址線之間的距離應該滿足3W原則(繞線的間距要兩倍于線寬)。時鐘連線盡量短,并且加上地線保護。為了保證時鐘信號的完整性,時鐘的輸出串接一個33歐姆左右的端接電阻。

3.3 關鍵信號與非關鍵信號

在仿真分析前,先對系統中的信號進行劃分,劃分為關鍵信號與非關鍵信號。劃分的原則主要是根據器件驅動沿速率快慢、工作頻率的高低與信號線長度等條件進行劃分,當然還應依實際的設計而定。

在本系統中,關鍵信號有:時鐘信號;CPU與SDRAM、CPU與FLASH等存儲器的數據線、地址線以及讀寫等控制信號線。其中最關鍵的是SDRAM與 MC9328MX1之間的連接走線,它們的信號完整性好壞直接影響著MC9328MX1能否將數據正確存取于SDRAM 中。

4 仿真分析與結果

4.1 LineSim仿真

在原理圖完成之后即可進行布線前信號完整性仿真,在這里使用HyperLynx的布局前分析工具LineSim完成布線前仿真。LineSim用在布線設計以前約束布線和各層的參數、設置時鐘的布線拓撲結構、選擇元器件的速率、診斷并避免信號完整性、電磁輻射等問題。

LineSim進行布線前仿真是很方便的,將廠商提供的IBIS模型添加到相應的模型庫中,在LineSim原理圖中將驅動端,接受端以及它們之間的連線方式設置好,就可以進行仿真了。LineSim還提供了對仿真結果一些建議,如連線的拓撲結構、連線的長度、端接電阻和電容的數值是否匹配等。

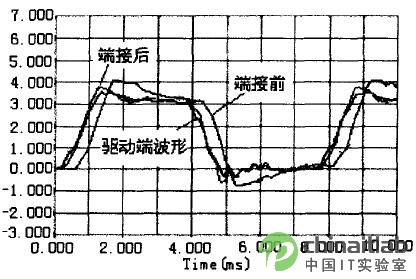

通過在布線之前信號完整性分析對布局進行指導,對邏輯器件的類型進行選擇,決定哪些信號需要端接,以及采用何種端接方法及端接電阻的阻值大小。圖1是在工作頻率為100 MHz時數據線D0添加33歐姆的并聯電阻端接前與端接后信號完整性分析的不同結果,可以看出在端接后明顯消除了上沖與下沖,且振蕩也大幅度地減小了

圖1 數據線D0仿真波形

4.2 BoardSim仿真

在布線前信號完整性仿真指導下完成布局布線之后,還可能存在一些信號完整性問題,如相鄰線網之間的串擾、EMC等,所以需要進行布線后的信號完整性仿真,對完成布線后的設計進行進一步的分析。在這里使用HyperLynx的布局后分析工具BoardSim完成信號完整性分析。BoardSim用于布線以后快速地分析設計中的信號完整性、電磁兼容性和串擾問題,生成串擾強度報告,區分并解決串擾問題。

對于某一網絡,像LineSim一樣,BoardSim可以進行單獨仿真,BoardSim還可以進行串擾仿真,相互耦合干擾的網絡仿真結束后顯示為白色。通過進行串擾仿真,可以很方便的找出相互干擾的網絡,通過改變網絡的間距或者是減小介質層厚度可以減小串擾。

對于整個pcb板,BoardSim可以進行快速仿真和詳細仿真,快速仿真,可以高效地分析PCB板,查找信號完整性和EMC等問題;詳細仿真提供了更具體的報告信息,針對一個網絡上的每個接收端IC的Pin、詳細的過沖、最小/最大IC Pin的延遲和極限域值等。仿真結果以文本型式輸出,這是一個很完整的分析報告,可以通過關鍵字“find warning”和“find warning(severe)”來找警告位置,該位置就是可能會出現信號完整性或者是EMC問題的地方。

根據布線后信號完整性仿真的仿真結果,通過改變端接方式與具體阻值即在驅動端添加不同阻值的串聯端接、在負載端添加不同阻值的并聯端接、調整端接的位置、修改走線的拓撲結構、調整板層間的介質厚度等方法進行反復的修改與仿真驗證,將各種信號完整性問題限制在可接受的范圍之內。

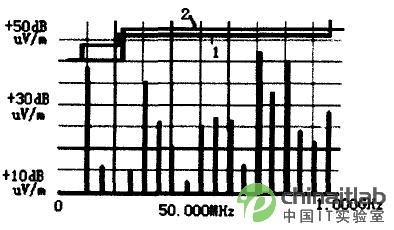

圖2為數據線D0產生的電磁輻射仿真圖,圖中曲線1與曲線2分別代表歐洲以及美國的規定輻射容限,垂直條為數據線D0在不同頻率下產生的輻射分貝值,從圖中可以看出,數據線Do產生的輻射均低于歐洲和美國所規定的輻射容限,符合要求。

4.3 實際結果分析

PCB制版后,為了測試PCB的性能和信號完整性,將MC9328MX1和SDRAM的運行速度設置在最高頻率100MHz,測試其時鐘線、地址線和數據線的波形,圖3為數據線D0在最高頻率100MHz下的波形圖。比較圖1可以看出,當SDRAM運行于100MHz時數據線的波形較好,證明仿真的結果是可信的。由此,系統平臺中MC9328MX1與SDRAM之間的數據傳輸可以達到其傳輸的最高性能。從而驗證了HyperLynx仿真軟件對信號完整性和 EMC分析的正確性。

5 結束語

隨著數字器件切換速度的逐步提高,信號完整性、串擾EMC分析對于設計成功的高速PCB設計而言越來越重要。在設計早期和設計期間進行信號完整性,串繞和 EMC分析問題有利于為PCB布線產生約束條件;避免昂貴的PCB返工,節省了大量的時間。在本設計中,借助基于IBIS模型和HyperLynx仿真工具進行信號完整性仿真分析,解決了許多信號完整性問題,避免了因信號完整性問題可能帶來的重復制板,縮短了設計周期。