摘要:針對通信中的回波問題,基于自適應濾波的LMS算法,設計了自適應回波抵消器。并基于利用FPGA芯片,在DSP Builder平臺上,有效結合MatLab/Simulink和Quanus II設計工具,根據模塊化設計思想實現了LMS算法自適應回波抵消器硬件電路設計。軟件仿真和系統FPGA硬件實測結果表明,該設計方法使回波抵消器的FPGA硬件實現更加簡便快捷。

關鍵詞:DSP Builder;回波抵消器;FPGA

在數字通信、衛星通信等系統中,不同程度的存在回波現象,影響了通信質量。為了消除回波可以采用回波抵消器,它能估計回波路徑的特征參數,以產生一個估計的回波信號,然后從接收信號中減去該信號,以實現回波抵消。而一般采用自適應濾波器模擬回波路徑,可以跟蹤回波路徑的變化。

DSP Builder是Ahera公司推出的面向DSP開發的系統級工具,它作為Matlab的一個Simulink工具箱出現,使得用FPGA設計的DSP系統完全可以通過圖形化界面進行設計和仿真。

文中介紹以DSP Builder為平臺完成自適應回波抵消器的FPGA電路設計,用FPGA驗證設計電路的正確性和可靠性。

1 自適應回波抵消器原理

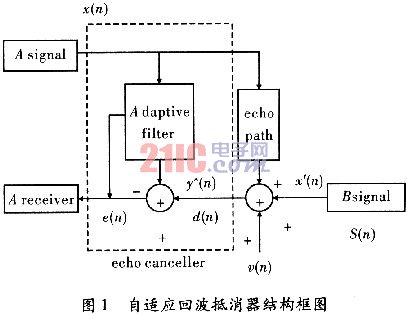

自適應回波抵消結構框圖,如圖1所示。

圖1中s(n)表示B信號;x’(n)表示A信號產生的回波;v(n)為近端環境噪聲;y’(n)是濾波器模擬的回波信號;e(n)是殘留回波信號或誤差信號。信號d(n)由B信號s(n)和回波x’(n)及噪聲組成,即d(n)=x’(n)+s(n)+v(n)。假定模擬回波信號估計為

![]()

式中,ωk(n)為自適應濾波器的時變系數,從信號d(n)中減去模擬回波y’(n)信號后的殘留回波信號或誤差信號為

![]()

當自適應濾波器的單位脈沖響應能很好地模擬回波通道的傳遞函數時,可以認為時,從而有e(n)=s(n)+v(n),這樣傳向遠端的信號中不包括回波信號x’(n),即回波被抵消。

其中,回波抵消器的主要部分自適應濾波器所用算法選擇LMS算法,其迭代公式為

![]()

式中,X(n) =[X(n),X(n-1),X(n-2),…,X(n-M+1)]T表示時刻n時的輸入信號矢量,由最近M個信號采樣值構成,W(n)=[W0(n),Wl(n),…,WM-1(n)]T表示n時刻自適應濾波器的系數矢量估值,μ是控制穩定性和收斂速度的步長參量。

2 FPGA硬件設計

設計選用FPGA是Altera公司Cyclone系列的EPlCl2Q240C8。FPGA中I/O端口可自由定義,電路設計方便、編程靈活、不易受外部干擾。系統編譯環境采用QuartusⅡ,頂層設計為圖形化方式。芯片模塊劃分為分頻模塊、D/A轉換模塊和回波抵消器模塊。分頻模塊采用VHDL語言編程實現,D/A轉換模塊采用硬件電路實現,同波抵消器模塊用DSPBuilder軟件進行設計。

2.1 分頻模塊設計

分頻模塊是將外部時鐘進行分頻設定,得到系統內部DA模塊和回波抵消器模塊所需要的時鐘。分頻模塊的外部時鐘輸入頻率為50 MHz,8分頻后產生的時鐘頻率約為6 MHz。

2.2 回波抵消器模塊設計

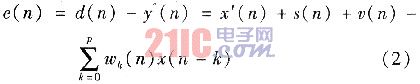

該部分采用層次化的設計方法。利用DSP Builder模塊構建自適應算法部分,根據LMS算法迭代公式(4)和濾波器的估計輸出式(2),建立加權分量模型。如圖2(a)所示。

在圖2(a)中,第i個延時單元的輸入信號為x(n),延時后的輸出信號為x(n-1),同時輸入信號x(n)產生一個乘積y’(n)=ω(n)x(n),由于是濾波器的估計輸出是一系列權值分量與輸入矢量的各分量乘積之和。因此,除第一級外,后續單元必須加上前一級的加權單元的輸出。封裝后,則可以根據濾波器階數的不同而相應調整,以實現多級級聯。尤其是在構造階數可變和階數較大的濾波器時更能顯出其靈活性。然后將封裝后的加權分量單元依照階數級聯,并再次封裝即構成抵消器模塊。可運用于頂層模型中。

在頂層系統模型中連接各子模塊,如圖2(b)所示,圖中兩個信號源sin2,sin1采用正弦信號發生器實現,利用正弦查找表產生正弦波數據,函數調用格式為lOsin([0:2π/2∧4:2π])和5sin[0:2π/2∧6:2π],其輸入地址分別為4位和6位,輸出為16位。Dixiaoqi模塊由圖2(a)級聯封裝得到,模塊Parallel to serial為并行/串行轉換器。

設計中,因語音信號頻率可以看作約為3.4 kHz,所以信號采樣頻率設為8 kHz,假設回波延遲2.5 ms(小于回波對聽覺產生干擾的范圍20 ms),考慮收斂速度和實現情況,步長采用0.1,計算得出濾波器階數20。

2.3 D/A轉換模塊設計

利用Texas Instruments公司的D/A芯片TLC5620,并輔助使用4輸入與門SN74HC08M和運算放大器LM358AM,構建數模轉換器。TLC5620是8位電壓輸出的數模轉換器,需5V外接電壓,有4個輸出端口可以選擇。利用擴展插槽與FPGA連接,信號接119腳,時鐘由所編程序在FPGA內實現,通過73腳與TLC5620連接,控制信號通過63腳連接TLC5620。

3 DSP Builder仿真和FPGA驗證

通過Simulink仿真得到波形,如圖3(a)所示,圖中第一行為返回A聽筒的誤差e信號波形,第二行為輸入話筒的所有信號,即B信號與回波信號之和。由變化的波形可以看出,隨著自適應濾波器的“學習”過程,回波逐漸被抵消。

利用ModelSim針對生成的RTL級VHDL代碼進行功能仿真,設置信號為模擬形式,如圖3(b)所示,圖中為減去回波后的誤差信號,與Simu-link仿真結果一致。

使用ModelSim完成RTL級功能仿真,其仿真結果并不能精確反映電路的全部硬件特性,進行門級的時序仿真仍然十分重要。在Quartus Ⅱ下編譯后進行時序仿真,其仿真波形,如圖3(c)所示。

把回波抵消器模型轉化生成圖元文件,作為一個子模塊在頂層系統中調用。在QuartusⅡ環境下,調用各個子模塊,構成完整的系統原理圖設計,然后進行編譯、仿真和引腳分配等工作。最后下載到FPGA芯片中,對硬件進行測試,采用SignalTapⅡ實際測得的值如圖4所示,驗證本設計的正確性。

最后通過D/A轉換電路接入示波器。觀測結果,如圖5(a),圖5(b)所示,通過比較混合回波的信號和經過抵消后得到的返回聽筒的消除回波以后的信號,可以看出回波已基本消除,設計達到目的。通過測試,回波衰減率約為25 dB,基本達到ITUTG.167標準中回波衰減率至少20 dB的要求。

4 結束語

采用DSP Builder進行設計,使用圖形界面,用模塊化設計代替以往的VHDL語言編程,并綜合多種設計工具,便于研究者迅速地將算法級的構思應用于系統設計中,從而可以專注于系統算法的設計,避免了繁瑣的語言編程和電路設計,提高了設計速度,縮短設計周期,為產品開發節約了研發時間。