CPLD" title="CPLD">CPLD是復雜的PLD,專指那些集成規模大于1000門以上的可編程邏輯器件。它由與陣列、或陣列、輸入緩沖電路、輸出宏單元組成,具有門電路集成度高、可配置為多種輸入輸出形式、多時鐘驅動、內含ROM或FLASH(部分支持在系統編程)、可加密、低電壓、低功耗以及支持混合編程技術等突出特點。而且CPLD的邏輯單元功能強大,一般的邏輯在單元內均可實現,因而其互連關系簡單,電路的延時就是單元本身和集總總線的延時(通常在數納秒至十數納秒),并且可以預測。所以CPLD比較適合于邏輯復雜、輸入變量多但對觸發器的需求量相對較少的邏輯型系統。

MAX7000" title="MAX7000">MAX7000系列產品與高速

2 MAX7000系列CPLD及其開發平臺介紹

由于高速數據采集系統的特殊要求,在眾多的CPLD器件中,選擇了ALTERA公司的MAX系列器件。MAX系列的高性能和高密度是基于它先進的MAX(Multiple Array Matrix--多重陣列矩陣)架構,因此為高速應用提供了非常高的性價比。MAX7000系列還提供了業界速度最快的可編程邏輯解決方案。它基于CMOS EEPROM工藝,傳播延遲最小為3.5ns,可以實現速度高于200MHz的計數器,并且為高密度的器件提供了非常寬的選擇余地,十分適合高速設計時應用。該公司的MAX+plusII軟件是一款易于使用的開發工具,其界面友好,集成化程度高,兼容工業標準,支持FLEXMAXACEX 1K等系列產品。并且為大學提供了學生版軟件,在功能上與商業版類似,僅在可使用的芯片上受限制。由于MAX7000系列的這些優點,以下的設計都基于MAX7000系列產品。

3 CPLD在高速尋址中的應用

一般的數據采集均需由CPU將A/D轉換的結果讀入,然后再轉存到片外的存儲器中,這樣至少需要4個機器周期。如果按照一般一個機器周期為1μs,那么最高采樣率只能達到250kHz,絕難滿足高速采樣的需要。在本系統中,直接將采樣數據存到高速緩沖RAM中,而存儲器尋址則采用ALTERA公司的EPM7032LC44-6構成的地址發生器來完成。寫信號可采用A/D轉換的時鐘信號,但需經過一系列分頻及邏輯組合,也可另由電路產生或放在地址發生器中。EPM7032LC44-6構成地址發生器的基本原理是采用5片級聯的74161組成20位的同步計數器,第20位接在高速緩沖RAM的片選線上,用來切換緩沖存儲器組。用CPU2的P1.7控制計數允許端,異步清零,則20位地址線輸出保持同步。其具體的實現可以采用圖形編輯輸入或者文本編輯輸入的方法。下面給出其VHDL語言程序。

其仿真結果如圖2所示。

4 CPLD構成數據總線控制器

在這個高速數據采集系統中,為了提高數據傳輸和尋址的速度,在正常采樣期間,其數據總線和地址總線并不需要CPU控制,數據存儲是由系統硬件自動完成的。但當CPU2監測到輸入模擬量的突變時,再經過預定的一段持續采樣時間后,就會發出控制信息給地址發生器和數據總線控制器,停止繼續存儲采樣數據和自動產生地址,而由CPU2取得總線的控制權,對處在高速緩沖RAM中的故障前后數據進行操作。為避免總線沖突,就需要一塊數據總線的控制器處理好系統總線和局部總線的關系。

EPM7064可以很好地解決這個問題。在EPM7064的內部,用三態門將CPU2的讀寫控制線、8根數據總線以及AD9225的12根數據線及一根溢出線與控制高速緩沖RAM的讀寫控制線和數據線隔離開來,由CPU2的P1.7作為CPU2或高速A/D控制總線的控制信號線,這樣就能方便地實現緩沖RAM數據線訪問控制權的切換。考慮篇幅,不再詳細給出實現程序。地址總線控制邏輯實現方法類似,不再介紹。

5 CPLD構成的ISA總線接口

在PC系列機中,I/O空間是獨立的,共有1KB(地址編號為000H~3FFH)。由于I/O接口一部分分布在主機母板上,另一部分分布在擴展槽上,所以I/O的1024個口地址也分成兩個部分,其中前512個由母板上的接口控制器使用,后512個供擴展槽內的接口控制卡使用。而且由于后512個地址中的一部分已經被配置成系統資源的接口,所以真正能被用戶設計開發的I/O端口為數不多,而且不連續。這樣就不能采用常規的用PC機提供的地址總線來尋址雙口RAM的方法,因為這種方法只能尋址其中為數不多而且不連續的一些單元。所以這是一個難點。為此,采用用PC機的數據線來尋址雙口RAM的方式,只需占用三個I/O端口,就能尋址整個4K的RAM區。

歡迎轉載,本文來自電子發燒友網(www.elecfans.com)

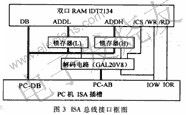

ISA總線接口電路邏輯框圖如圖3所示。

采用了ISA插槽中的8位數據線、10位地址線、讀寫控制線IOW和IOR以及電源線,并假設使用390H、391H、392H三個端口。當PC機要訪問某一地址單元時,首先通過390H端口將低8位地址送到數據總線上。此時由PC-AB送出的390H信號和IOW信號經解碼電路輸出一個鎖存脈沖到鎖存器(L),將此低8位地址鎖存;然后通過391H端口將高4位地址送到數據總線上,此時由PC-AB送出的391H信號和IOW信號經解碼電路輸出一個鎖存脈沖到鎖存器(H),將此高4位地址鎖存;最后通過392H端口進行讀寫,只要PC-AB上出現392H信號,解碼電路就輸出一個低電平到雙口RAM的/CS,再根據相應的讀寫控制信號就能進行讀寫操作。

用ALTERA公司的EPM7064SLC84-5實現這一接口的VHDL文件如下:

仿真結果表明此電路設計完全可以實現上述功能。PC機使用端口392H讀取雙口RAM中的數據時的仿真圖如圖4所示。

CPLD是現代電子工程領域的一門新技術,它提供了基于計算機和信息技術的電路系統設計方法,提高了設計電路的集成度和可靠性。筆者在將ALTERA公司推出的MAX7000系列產品應用于高速數據采集方面做了嘗試,具體使用EPM7032和EPM7064設計了地址發生器、數據總線控制器和ISA總線的接口,目前已經將其應用在電力系統某精確故障定位系統中。