0 引言

軟件無線電是在無線通信領域提出的一種新的通信系統體系結構,其核心思想是以開放性、標準化、模塊化的硬件為通用平臺,通過在平臺加載不同軟件來實現對工作頻段、調制解調、信道多址方式等無線功能的靈活配置。而調制解調技術是軟件無線電的主要組成部分。直接數字合成技術(DDS)具有較高的頻率分辨率,可實現快速的頻率切換,能夠保持相位的連續性,很容易實現幅度、頻率和相位的數控調制。目前,軟件無線電調制技術多采用具有調制功能的專用芯片或可編程器件和專用芯片相結合的方法實現,靈活性并不是很強。

基于此,本系統在分析數字調制技術和DDS原理的基礎上,詳述了一種基于FPGA的DSP技術和DDS技術的適合于軟件無線電使用的可控數字調制器的設計過程,并在系統中進行了功能驗證。此調制器以FPGA硬件平臺為核心,可實現ASK,FSK,PSK,QAM等調制方式,靈活性強。

1 數字調制和DDS基本概述

在數字通信系統中,為了使數字信號能在帶限信道中傳輸,就必須將編碼后的信號進行數字調制。在此,主要分析和實現二進制單極性不歸零碼的鍵控調制。常見的二進制調制方式有ASK,FSK,PSK,QAM等。

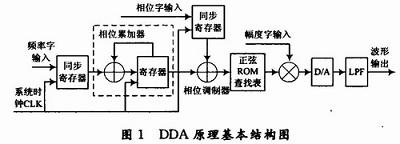

直接數字合成(DDS)器具有數控頻率合成的功能,它以數控振蕩器的方式產生頻率、相位和幅度可控的正弦波,電路主要由相位累加器、相位調制器、正弦ROM查找表、系統時鐘、D/A、LPF等組成。本文中用DDS產生的正弦波作為載波,具有精確、靈活、便于集成等優點。DDS原理基本結構圖如圖1所示。

使用DDS結構易實現頻率調制、相位調制和幅度調制,以DDS作為載波信號發生部分,具有頻率穩定度高,頻率轉換速度快,輸出帶寬寬,頻率分辨率高等特點。

2 基于FPGA的調制器的具體設計

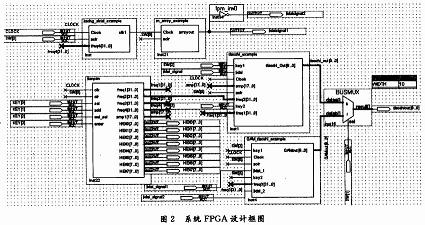

該設計借助QuartusⅡ7.2和Matlab/DSP Builder 7.2開發環境,在FPGA硬件平臺上實現,最大限度的實現了集成化。圖2是該設計的FPGA系統原理框圖,數字功能模塊全部集成在一片FPGA上,實現了SoPC的設計思想。

該設計由按鍵輸入、二進制基帶信號產生、數字調制和顯示等模塊組成,其功能是由按鍵輸入設定值,同時在LED上進行顯示,并根據設定值對二進制基帶信號進行相應的數字調制,產生調制信號輸出。現將各模塊的具體設計和功能描述如下:

按鍵輸入模塊 輸入采用按鍵和撥碼開關實現,通過復用的方式用于選擇調制方式,輸入信號頻率和幅度。在FPGA內部設計了一個按鍵接口模塊,用于處理和存儲輸入的設定值,輸出到LED顯示,并輸出相應的控制信號和調制模塊所需的載波頻率和幅度控制字等。

二進制基帶信號產生模塊 該設計中的基帶信號由一個基于DDS的矩形脈沖發生器和偽隨機序列M序列發生器產生。碼元速率可通過按鍵模塊輸入頻率字到矩形脈沖發生器控制輸出脈沖頻率,從而控制M序列輸出頻率來實現。當然,作為調制器,二進制數字基帶信號是由外部輸入的。本模塊是為了驗證系統功能和需要滿足系統產生單純的數字調制信號時而設計的,具體見系統原理圖中juxing_signal和m_array_exa-mple模塊。

數字調制模塊 數字調制模塊是整個系統的核心部分,包括ASK,FSK,PSK和QAM等數字調制方式。本模塊以DDS為核心模型,采用Quart-usⅡ7.2和Matlab/DSP Builder7.2進行硬件的軟件化設計,具體見系統原理圖中tiaozhi_example,QAM_tiaozhi_example和BUSMAX模塊。系統主要由時鐘和復位輸入端(CLOCK和SW[0])、調制方式選擇輸入端(SW[1],SW[2]和SW[3])、基帶信號輸入端(jidai_signal,jidai_sign-all,jidai_signal2)和頻率幅度字輸入端(freql[31..O],freq2[31..O],freq4[31..0]和amp[17..O])組成。頻率和幅度字由按鍵輸入實際頻率和幅度值經過按鍵接口模塊處理后,轉化為32位頻率字和18位幅度字,從而控制模塊產生所需頻率和幅度的載波信號。基帶信號輸入端接收被調制信號,被調制信號根據所選擇的調制方式在模塊內部進行相應調制后輸出到模塊輸出端。

3 系統仿真和硬件實現與測試

在進行系統各模塊設計的時候,為了防止在設計最后集成系統的時候出現功能錯誤,難于排查和修改,在設計過程中對各模塊的功能正確性都進行了軟件仿真。

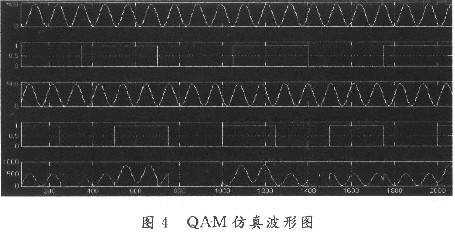

系統中的ASK,FSK,PSK和QAM波形仿真依次如圖3和圖4所示。

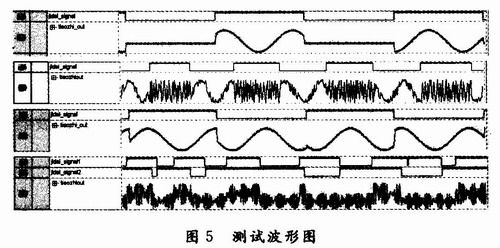

在確保各模塊在獨立狀態下均能正確工作后,在QuartusⅡ7.2中進行系統集成,并對集成后的系統進行再次的整體仿真。接著,便可以進行功能測試。在功能測試中使用嵌入式邏輯分析儀SignalTapⅡ進行測試分析。在分析儀中進行相應的設置后,把它隨設計文件一起下載入目標芯片中,用以捕捉芯片內部信號節點處的信號,并通過USB接口把數據傳回計算機,并顯示。以下是具體的測試過程,選擇相應功能控制開關,用按鍵輸入所需的載波頻率值和幅度值,通過LED顯示出來。相應的測試波形如圖5所示。

2ASK功能測試(SW[1]=0,SW[2]=O,SW[3]=O):載波頻率由freql輸入設置,當基帶碼元為高電平1時,輸出正弦信號;當為低電平0時,輸出一個常數值,從而實現2ASK調制。

2FSK功能測試(SW[1]=O,SW[2]=1,SW[3]=1):載波信號頻率由freql和freq2輸入設置,當基帶信號碼元為高電平1時,輸出頻率為freql正弦波信號;當為低電平0時,輸出頻率為freq2正弦波信號,從而實現了2FSK調制。

2PSK功能測試(SW[1]=0,SW[2]=O,SW[3]=1):載波信號頻率由freql輸入設置,但同時控制了正弦查找表和余弦查找表,當基帶信號碼元為高電平1時,控制正弦表輸出正弦波信號;當為低電平0時,輸出余弦波信號,從而實現了2PSK調制。

QAM功能測試(SW[1]=1,SW[2]=1,SW[3]=0):載波信號頻率由freq3輸入設置,同時控制了正弦查找表和余弦查找表,兩查找表信號相互正交,兩路基帶信號碼元分別乘上正余弦查找表輸出信號,然后將輸出信號進行疊加,從而實現了QAM調制。

4 結語

該設計完全在一片FPGA芯片上完成,減少了硬件的搭構,具有很高的集成度。采用DDS技術為核心,使載波信號獲得了較高的性能。借助強大的開發工具和FPGA的可重復編程及動態重構特性,使設計更具靈活性和通用性。系統設計了按鍵輸入和處理模塊,能根據需要變更載波頻率,并通過LED直觀顯示出來。重點對調制模型進行了設計,并進行了系統級仿真和最后的硬件功能測試,達到了設計的具體要求。