直接數(shù)字頻率合成技術(shù)(Direct Digital Synthesis,DDS)是一種從相位概念出發(fā)直接合成所需要的波形的新的全數(shù)字頻率合成技術(shù),該技術(shù)具有頻率分辨率高、頻率變化速度快、相位可連續(xù)性變化等特點,在數(shù)字通信系統(tǒng)中被廣泛采用,是信號生成的最佳選擇。目前市場上可以見到很多集成的、多功能的專用DDS芯片,像AD9835、AD9954、AD9959等。但是在某些場合,專用DDS芯片在控制方式、頻率控制等方面與系統(tǒng)的要求差別很大,現(xiàn)場可編程門陣列(FPGA)器件具有工作速度快、集成度高、可靠性高和現(xiàn)場可編程等優(yōu)點。利用它來設(shè)計符合自己需要的DDS電路是一個很好的解決方法。

1 DDS的基本原理

DDS的主要思想是從相位的概念出發(fā)合成所需要的波形,其結(jié)構(gòu)由相位累加器、波形存儲器、數(shù)模轉(zhuǎn)換器、低通濾波器和參考時鐘五部分組成,其基本原理框圖如圖1所示。

綜上所述,在采樣頻率一定的情況下,可以通過控制頻率控制字K來控制所得離散序列的頻率,經(jīng)保持、濾波之后可唯一地恢復(fù)出此頻率的模擬信號。

關(guān)鍵字:DDS FPGA 數(shù)字通信系統(tǒng)

2 基于FPGA技術(shù)實現(xiàn)DDS的方案

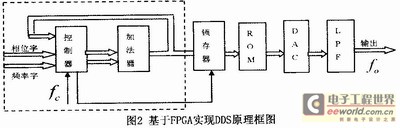

用FPGA實現(xiàn)DDS的基本工作過程為:通過VXI接口電路將生成的數(shù)據(jù)存入固定數(shù)據(jù)RAM中,然后用FPGA設(shè)計的相位累加器來計算并選擇RAM中的數(shù)據(jù)存放地址,最后將數(shù)據(jù)給定的頻率控制字輸出,經(jīng)DAC轉(zhuǎn)換即實現(xiàn)了任意波形輸出。原理圖如圖2所示。虛線部分可用FPGA來實現(xiàn)。

圖2中參考時鐘由高穩(wěn)定的晶體振蕩器產(chǎn)生,主要用于控制DDS中各器件同步工作。虛線部分相當于相位累加器,它由N位加法器與N位相位寄存器構(gòu)成,它實際上是一個計數(shù)器。每來一個時鐘脈沖,加法器將相位增量數(shù)據(jù)與相位寄存器輸出的累積相位數(shù)據(jù)相加,把相加后的結(jié)果送至相位寄存器的數(shù)據(jù)輸入端。相位寄存器將加法器在上一個時鐘作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器在下一個時鐘的作用下繼續(xù)與頻率控制字相加。由此看來,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器輸出的數(shù)據(jù)就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。

3 結(jié)束語

采用FPGA設(shè)計DDS電路,充分發(fā)揮了FPGA在系統(tǒng)可編程的優(yōu)點,可以通過軟件靈活改變相關(guān)參數(shù),給設(shè)計帶來很多方便。用FPGA設(shè)計DDS電路較采用專用DDS芯片更為靈活,只要改變FPGA中的ROM數(shù)據(jù),DDS就可以產(chǎn)生所需波形數(shù)據(jù),并且FPGA的功能完全取決于設(shè)計需要,因而具有相當大的靈活性,將DDS設(shè)計嵌入到FPGA芯片所構(gòu)成的系統(tǒng)中,其系統(tǒng)成本并不會增加多少,因此,采用FPGA來設(shè)計DDS系統(tǒng)具有很高的性價比。