Spartan-3FPGA能以突破性的價位點實現嵌入式DSP功能。本文闡述了Spartan-3 FPGA針對DSP而優化的特性,并通過實現示例分析了它們在性能和成本上的優勢。

所有低成本的FPGA都以頗具吸引力的價格提供基本的邏輯性能,并能滿足廣泛的多用途設計需求。然而,當考慮在FPGA構造中嵌入DSP功能時,必須選擇高端FPGA以獲得諸如嵌入式乘法器和分布式存儲器等平臺特性。

Spartan-3 FPGA的面世改變了嵌入式DSP的應用前景。雖然Spartan-3系列器件的價位可能較低,但它們同樣具有DSP設計所需的平臺特性。這些平臺特性能夠以較高的面積利用率實現信號處理功能,使設計達到更低價位點。

Spartan-3器件用作協處理器或預/后處理器是非常理想的,它們將運算密集型功能從可編程DSP上卸載下來以增強系統性能。

1 針對DSP而優化

賽靈思公司的Spartan-3器件采用90nm工藝技術以及300mm晶圓,大大降低了FPGA的成本。與此同時,這些器件還包括諸如嵌入式18×18位乘法器、大塊存儲器(18kb)、分布式RAM以及移位寄存器等關鍵DSP資源。這些高級特性意味著采用Spartan-3 FPGA,能以比其它競爭FPGA低得多的價位實現DSP算法。

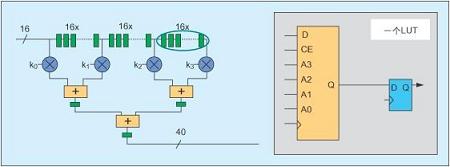

圖1:增強型架構允許用

單個LUT代替16個寄存器。除增加系統的基本性能之外,這些嵌入式特性還能提高器件的利用率。例如,如果在邏輯結構中實現Spartan-3嵌入式乘法器,需要占用300~400個邏輯單元(LE)。此外,因為嵌入式乘法器緊鄰邏輯結構,所以拓展其功能(比如創建加法器或者級聯多個乘法器來支持復雜的算法功能)是非常簡單的。

為提高效率,許多DSP功能以時分復用的形式在管道中得以很好實現。這樣做雖然能創建帶寬更高、速度更快的系統,但同時也將面臨更多臨時存儲單元需求而帶來的成本增加。譬如,時分復用濾波器需要將各個乘法-累加單元的結果存儲在移位寄存器里。這種設計將在用完FPGA的邏輯資源之前就可能耗盡寄存器或存儲器資源。Spartan-3 FPGA系列的獨特之處在于它們可提供這樣一種模式:一個查找表(LUT)能夠執行邏輯功能或配置成一個16位移位寄存器。

如圖1所示,這種增強型的架構允許用單個LUT來代替16個寄存器,在實現時分復用DSP功能時能使面積利用率最大化。

許多DSP功能也需占用大量的存儲器資源,它們需要便箋存儲器來保存系數、執行FIFO以及獲得較大的緩沖區。與目前使用的其它低成本FPGA相比,Spartan-3器件可提供更多的存儲位數。對于許多DSP設計而言,最重要的資源是FPGA內的嵌入式存儲器,而不是邏輯電路或者乘法器。因為存儲資源不足,采用競爭的低成本器件的設計工程師不得不選用更大規模的器件或采用外部存儲器來構建系統,而這些系統只需一片體積很小的Spartan-3 FPGA就可以得到實現。

2 常見的DSP功能實現

下面通過分析有限沖擊響應(FIR)濾波器的兩個實現示例來說明這些特性是如何影響器件的利用率。一個是基于乘法累加器(MAC)的實現,另一個是基于多通道分布式算法(DA)的實現。

FIR濾波器通常應用于基站、數字視頻、無線局域網、xDSL以及有線調制解調器。測試基準是在Spartan-3 XC3S400 FPGA中實現頻率為130MHz、數據和系數均為16位的64抽頭MAC FIR濾波器。第一個實現僅用了一個MAC,第二個實現則用了四個MAC。

從采用單個MAC的實現到采用四個MAC的實現可顯著增加FIR濾波器的性能,而LUT數量只增加一倍并仍僅占總可用邏輯資源的4%。四個MAC的實現使用了四塊RAM和四個MAC,以最少的器件邏輯資源高效地實現了FIR濾波器。

另一個有趣的實現是多通道FIR功能的實現,在這里可以看到從單通道FIR濾波器到8通道FIR濾波器,器件利用率是如何變化的。

實現單通道分布式算法FIR濾波器使用了XC3S1000 Spartan-3器件29%的邏輯資源和39%的寄存器資源。當實現同樣的8通道濾波器時,通常將不同通道進行時分復用來保存邏輯,但這將占用很多寄存器或者大量的片內存儲器來存放中間結果。

如果使用Spartan-3 FPGA,中間結果將被存放在由LUT配置成的16位移位寄存器(SRL-16)中。這樣,實現同樣的8通道濾波器只多使用10%的可用邏輯資源和7%的可用寄存器資源,也就是說,構建8個通道僅多占用25%的器件資源。

這種顯著的資源節約與Spartan-3器件中SRL-16的使用有直接關系,在8通道實現中還有另外1,343個LUT被用作SRL-16模式。

如果在不支持SRL-16性能的FPGA中實現這種設計,將需要額外的10,744(1343×8)個觸發器用作存儲單元,這就必須選用大規模器件以提供數量龐大的寄存器,同時將也會消耗相關的組合邏輯資源。