摘要:給出了任意比例系數的加減法運算電路,分析了比例系數與平衡電阻、反饋電阻的關系。目的是探索比例系數任意取值時加減法運算電路構成形式的變化。結論是在輸入端電阻平衡時,各加運算輸入信號比例系數之和與各減運算輸入信號比例系數之和的差值在大于1、小于1或等于l情況下,加減法運算電路還可簡化。所述方法的創新點是將運放輸入端電阻的平衡條件轉化為與輸入信號比例系數的關系,從而可直觀確定簡化電路形式:擴大了加減法運算電路的應用范圍。

關鍵詞:加減法運算電路;比例系數;平衡條件

0 引言

加減法運算電路以集成運算放大器為核心元件構成,多個輸入信號分別作用于運放的同相輸入端和反相輸入端,實現對輸入信號的加、減法運算,外部電阻決定輸入信號的比例系數。

加減法運算電路中運放的輸入端有共模信號成分,為使共模輸出為零,同時補償運放輸入平均偏置電流及其漂移影響,通常要求運放的輸入端電阻平衡,即運放反相輸入端、同相輸入端所接的電阻相等。

本文給出了任意比例系數的加減法運算電路,并指出在輸入端電阻平衡時,根據輸入信號比例系數的數值范圍,加減法運算電路還可簡化。

1 任意比例系數的加減法運算電路

所給出的任意比例系數的加減法運算電路如圖1所示。其中,u111、u112、…u11n為n個減運算輸入信號,u121、u122、…u12m為m個加運算輸入信號,u0為輸出信號,R11、R12、…R1n、R21、R22、…R2m為輸入端電阻,RF為反饋電阻,Rp為平衡電阻,R’為附加電阻。

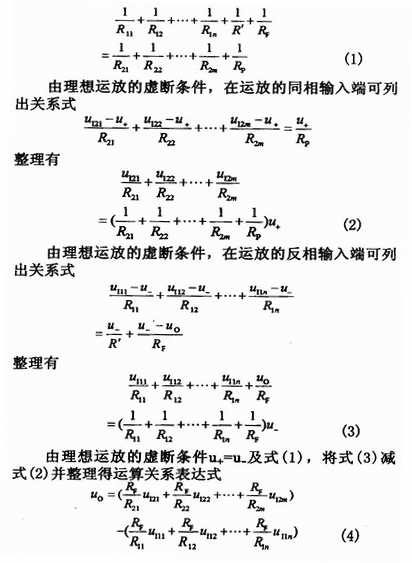

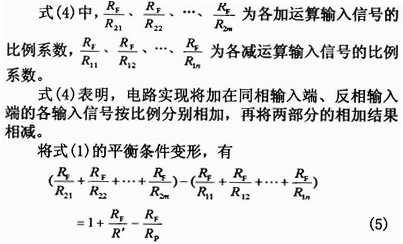

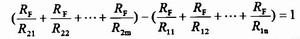

運放輸入端電阻的平衡條件為

式(5)反映了輸入信號比例系數與附加電阻、平衡電阻、反饋電阻的關系,表明在滿足電阻平衡的條件下,各加運算輸入信號比例系數之和與各減運算輸入信號比例系數之和的差值可以大于l、小于1或等于1,即輸入信號的比例系數無限定。

根據輸入信號比例系數的數值范圍,加減運算電路還可簡化。

2 比例系數加減結果特定取值時的電路簡化方案

2.1 各加運算輸入信號比例系數之和與各減運算輸入信號比例系數之和的差值大于1的加減運算電路

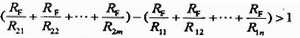

當各輸入信號的比例系數關系為

時,可令式(5)中電阻Rp→∞,即圖1所示電路中去掉電阻Rp,由式(5) 中實現大于1的平衡條件。

中實現大于1的平衡條件。

2.2 各加運算輸入信號比例系數之和與各減運算輸入信號比例系數之和的差值小于1的加減運算電路

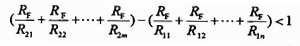

當各輸入信號的比例系數關系為

時,可令式(5)中電阻R’→∞,即圖1所示電路中去掉電阻R’,由式(5)中 實現小于1的平衡條件。

實現小于1的平衡條件。

2.3 各加運算輸入信號比例系數之和與各減運算輸入信號比例系數之和的差值等于1的加減運算電路

當各輸入信號的比例系數關系為

時,可令式(5)中電阻R’→∞,Rp→∞,即圖1所示電路中去掉電阻R’及Rp。

3 設計步驟及舉例

3.1 設計步驟

(1)由參與運算的各輸入信號比例系數加、減的數值范圍確定電路形式;

(2)由運算關系及平衡條件確定外部各個電阻值。

3.2 設計舉例

例1,試設計實現u0=2u121+3u122-u111運算關系的加減運算電路。

將所要實現的運算關系式與式(4)對比,確定式(4)中各輸入信號的比例系數為

![]()

因,確定所設計電路的形式為圖1中去掉電阻Rp,按三個輸入信號重畫如圖2所示。

選取Rp=120kΩ,代入各輸入信號的比例系數表達式中,解出

R21=60kΩ,R22=40kΩ,R11=120kΩ

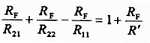

由式(5)并考慮Rp→∞,有

代入各輸入信號的比例系數,有

![]()

解出R’=40kΩ。

例2,試設計實現u=2u121-3u111-u112運算關系的加減運算電路。

將所要實現的運算關系式與式(4)對比,確定式(4)中各輸入信號的比例系數為

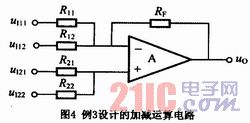

例3,試設計實現u0=2u121+u122-1.5u111-0.5u112運算關系的加減運算電路。

將所要實現的運算關系式與式(4)對比,確定式(4)中各輸入信號的比例系數為

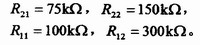

確定所設計電路的形式為圖1中去掉電阻R’及Rp,按四個輸入信號重畫如圖4所示。

選取RF=150kΩ,代入各輸入信號的比例系數表達式中,解出

4 結語

本文討論了加減運算電路的構成形式及比例系數適應范圍,從而可實現輸入信號以任意比例系數參與運算的電路設計,使運算電路具有普遍適用性。